# ΕΘΝΙΚΟ ΚΑΙ ΚΑΠΟΔΙΣΤΡΙΑΚΟ ΠΑΝΕΠΙΣΤΗΜΙΟ ΑΘΗΝΩΝ

#### ΣΧΟΛΗ ΘΕΤΙΚΩΝ ΕΠΙΣΤΗΜΩΝ ΤΜΗΜΑ ΦΥΣΙΚΗΣ ΔΙΑΤΜΗΜΑΤΙΚΌ ΠΡΟΓΡΑΜΜΑ ΜΕΤΑΠΤΥΧΙΑΚΩΝ ΣΠΟΥΔΩΝ ΣΤΟΝ ΗΛΕΚΤΡΟΝΙΚΌ ΑΥΤΟΜΑΤΙΣΜΟ

#### ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

#### Design and Implementation of Image Processing Algorithms on SoC Platforms for Embedded Applications

Ιωάννης Γ. Στρατάχος Α.Μ. : 2013522

Επιβλέπων : Δημήτριος Ι. Σούντρης

Αναπληρωτής Καθηγητής ΕΜΠ

Συνεπιβλέπων : Διονύσιος Ι. Ρεΐσης

Αναπληρωτής Καθηγητής ΕΚΠΑ

Αθήνα Οκτώμβριος 2016

#### ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

#### Design and Implementation of Image Processing Algorithms on SoC Platforms for Embedded Applications

Iωάννης Γ. Στρατάχος A.M.: 2013522

Επιβλέπων : Δημήτριος Ι. Σούντρης

Αναπληρωτής Καθηγητής ΕΜΠ

Συνεπιβλέπων : Διονύσιος Ι. Ρεΐσης

Αναπληρωτής Καθηγητής ΕΚΠΑ

Τριμελής Επιτροπή Εξέτασης

(Υπογραφή) (Υπογραφή) (Υπογραφή)

Δημήτριος Σούντρης Διονύσιος Ρεΐσης Γεώργιος Λεντάρης

Αναπληρωτής Καθηγητής Αναπληρωτής Καθηγητής Σίδάκτωρ

ΕΜΠ ΕΚΠΑ ΕΚΠΑ

Ημερομηνία Εξέτασης: 13 Οκτωβρίου 2016

# Περίληψη

Σήμερα η συνεχής πρόοδος στην τεχνολογία έχει οδηγήσει στην ανάπτυξη πιο πολύπλοκων και υπολογιστικά απαιτητικών αλγορίθμων επεξεργασίας εικόνας. Πολλοί από αυτούς τους αλγόριθμους έχουν υιοθετηθεί σε ενσωματωμένα συστήματα τα οποία στοχεύουν σε μια ποικιλία εφαρμογών, όπως η αυτοκινητοβιομηχανία, 3D πλοήγηση, την επιτήρηση, κλπ. Ωστόσο, σε ενσωματωμένα συστήματα πραγματικού χρόνου, όπου η καθυστέρηρη μεταφοράς δεδομένων και τη κατανάλωση ισχύος διαδραματίζουν σημαντικό ρόλο, εφαρμογές λογισμικού προσανατολισμένες να εκτελούνται σε επεξεργαστές γενικής χρήσης δεν μπορούν να προσφέρουν ικανοποιητικές λύσεις.

Σκοπός της παρούσας διπλωματικής εργασίας είναι ο σχεδιασμός ενός συστήματος επεξεργασίας εικόνας για ενσωματωμένες εφαρμογές, η υλοποίησή του σε Σύστημα-σε-Ψηφίδα και η αξιολόγηση του. Ως εφαρμογή επιλέχθηκε ο εντοπισμός ενός αντικειμένου και η ενημέρωση του χρήστη για το πώς να μετακινήσει την κάμερα ώστε να ευθυγραμμιστεί με το αντικείμενο. Ένα βασικό στοιχείο αυτής της διπλωματικής εργασίας είναι η μελέτη των βημάτων επεξεργασίας της εικόνας και ο εντοπισμός των κρίσιμων βημάτων που επηρεάζουν σημαντικά το χρόνο επεξεργασίας. Με την εφαρμογή μεθοδολογιών συσχεδίασης Υλικού/Λογισμικού, επιμέρους τμήματα αναπτύχθηκαν ως κομμάτια του υλικού με τη χρήση VHDL και τα υπόλοιπα αναπτύχθηκαν ως συστατικά στοιχεία του λογισμικού χρησιμοποιώντας τη γλώσσα προγραμματισμού C. Η πλατφόρμα που χρησιμοποιήθηκε για την ανάπτυξη του συστήματος βασίζεται στην οικογένεια των συσκευών Zynq-7000 All Programmable SoC (AP SoC) της Xilinx. Η αξιολόγηση του συστήματος βασίστηκε στη μέτρηση του ποσοστού επιτυχίας της συνολικής λειτουργίας και τις μετρήσεις που σχετίζονται με την πλατφόρμα που χρησιμοποιείται, όπως η κατανάλωση ισχύος, η κατανάλωση πόρων, ο χρόνος εκτέλεσης κλπ. Επίσης πραγματοποιήθηκε σύγκριση με εναλακτικές πλατφόρμες οι οποίες εκτελούσαν την λειτουργία του συστήματος αποκλειστικά στο λογισμικό.

**Λέξεις Κλειδιά**— Συσχεδίαση Υλικού/Λογισμικού, Επεξεργασία Εικόνας, Σύστημα-σε-Ψηφίδα, Harris Corner Detector, Ενσωματωμένο Σύστημα, Zynq

## Abstract

Nowadays the ever-increasing advancements in technology has led to the deployment of more complex and computationally intensive image processing algorithms. Many of these algorithms have been adopted in present-day embedded systems targeting a variety of applications such as automotive, 3D navigation, surveillance, etc. However in real-time embedded systems, where latency and power play an important role, software-oriented implementations running on general purpose CPUs may not offer satisfactory solutions.

The purpose of this thesis is the design of an image processing system for embedded applications, its deployment on a System-on-Chip (SoC) platform and the evaluation of the developed system. As a case study was selected to identify an object and to inform the user on how to move the camera in order to be able to stay aligned with the object. A key element of this thesis is the study of the image processing steps and the identification of critical steps that significantly affect the processing time. By applying hardware/software codesign methodologies individual parts were implemented as hardware components described using VHDL and the rest developed as software components using the C programming language. The platform used to deploy the system is based upon Xilinx's Zynq-7000 All Programmable SoC (AP SoC) family of devices. The system was evaluated based on measuring the success rate of the overall operation and on measurements related to the SoC platform used, such as power consumption, resource utilization, execution time etc. Also a comparison with software oriented approaches executed in CPUs was conducted.

**Keywords**— Hardware/Software codesign, Image Processing, System-on-Chip, Harris Corner Detector, Embedded System, Zynq

# Ευχαριστίες

Πρώτον, θα ήθελα να εκφράσω την ευγνωμοσύνη μου στους επιβλέποντές μου, Καθηγητή Δημήτριο Σούντρη ΕΜΠ και Καθηγητή Διονύσιο Ρεΐση ΕΚΠΑ που με εμπιστεύθηκαν με αυτήν την διπλωματική εργασία που αντιμετωπίζει ένα πολύ απαιτητικό θέμα σε ένα πολύ ανταγωνιστικό πεδίο, όπως η επεξεργασία εικόνας. Ειδικά τον Καθηγητή Δημήτριο Σούντρη που μου έδωσε την ευκαιρία να εκπονήσω την διπλωματική μου εργασία στο Εργαστήριο Μικροϋπολογιστών και Ψηφιακών Συστημάτων (MicroLab) στο ΕΜΠ.

Επίσης, θα ήθελα να ευχαριστήσω τον μεταδιδακτορικό ερευνητή Γεώργιο Λεντάρη και τον υποψήφιο διδάκτωρ Κωνσταντίνο Μαραγκό για τη βοήθεια και τη συνεργασία τους καθ όλη τη διάρκεια της διπλωματικής μου. Οι οξυδερκείς παρατηρήσεις τους κατά τη διάρκεια των συνομιλιών μας με βοήθησαν να βελτιώσω και να επεκτείνω τις γνώσεις μου γύρω από το θέμα της διπλωματικής αυτής εργασίας και είμαι ευγνώμων για το ότι θα έχω την ευκαιρία να συνεργαστώ μαζί τους στο μέλλον. Θα ήθελα επίσης να ευχαριστήσω όλα τα μέλη του Microlab για το ευχάριστο περιβάλλον εργασίας.

Τέλος θα ήθελα να ευχαριστήσω τους φίλους και την οικογένειά μου. Η συνεχή υποστήριξή τους καθ ΄όλη τη ζωή και τις σπουδές μου, μου έδωσε δύναμη να συνεχίσω να επιδιώκω τους στόχους μου.

## Acknowledgments

First I would like to express my gratitude to my supervisors, Prof. Dimitrios Soudris NTUA and Prof. Dionysios Reisis NKUA for trusting me with this diploma thesis that tackles a very demanding topic in a very competitive field such as image processing. Especially Prof. Dimitrios Soudris who gave me the opportunity to do my diploma thesis at the Microprocessors and Digital Systems Lab (MicroLab) in NTUA.

Also i would like to thank Post-Doctoral researcher Georgios Lentaris and Phd candidate Konstantinos Maragos for their help and cooperation throughout the course of my diploma thesis. Their insightful comments during our conversations helped me improve and expand my knowledge around the topic of this diploma thesis and i am grateful that i will have the opportunity to work with them in the near future. I would also like to thank all the members of Microlab for the pleasant working environment.

Last but not least, I would like to thank my friends and family. Their continuous support throughout my life and studies gave me strength to continue pursue my goals.

# Contents

| 118               | Περίληψη                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |           |         |      |                                       |          | j                                            |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------|---------|------|---------------------------------------|----------|----------------------------------------------|

| Al                | Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |           |         |      |                                       |          | ii                                           |

| $\mathbf{E}\iota$ | Ευχαριστίες                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |           |         |      |                                       |          | iii                                          |

| Ac                | Acknowledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |           |         |      |                                       |          | iv                                           |

| Eν                | Εκτεταμένη Περίληψη                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |           |         |      |                                       |          | 1                                            |

| 1                 | <ul> <li>1 Introduction</li> <li>1.1 Image Processing in Embedded Systems</li> <li>1.2 FPGAs in Image Processing</li> <li>1.3 Thesis Goals and Organization</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |           |         | <br> |                                       | <br>     | <br>17                                       |

| 2                 | 2 Hardware Platform         2.1 FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |           |         |      |                                       |          |                                              |

| 3                 | 3 System Description 3.1 Processing Flow 3.2 Hardware/Software Codesign 3.2.1 System Partitioning 3.3 The Harris Corner Detector 3.3.1 Feature Detection 3.3.2 Theoretical Background 3.3.3 Hardware Implementation 3.4 Data Clustering 3.4.1 k-means Algorithm 3.4.2 DBSCAN Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |           |         |      | · · · · · · · · · · · · · · · · · · · | <br>     | 25<br>27<br>28<br>28<br>29<br>30<br>32<br>32 |

| 4                 | 4 Software Environment 4.1 Bare-metal Environment 4.2 Operating System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |           |         | <br> |                                       | <br>     | <br>35<br>35<br>36                           |

| 5                 | 5 System Integration 5.1 Hardware/Software Communication 5.1.1 Data Streaming : Xillybus IP Construction : Xillybus Solution : Xillybus Solu | re<br>us-Lite I | <br>P Cor | · · · · | <br> |                                       | <br><br> | <br>37<br>37<br>38<br>39<br>40               |

| 6 | System Evaluation        | <b>43</b> |

|---|--------------------------|-----------|

|   | 6.1 Experimental Results | 43        |

| 7 | Conclusions              | 48        |

|   | 7.1 Thesis Summary       | 48        |

|   | 7.2 Future Work          | 49        |

# List of Figures

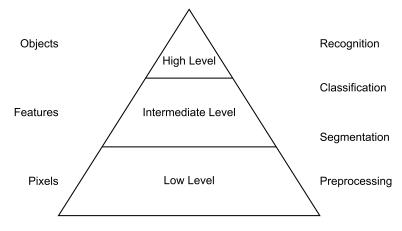

| 1.1 | Image processing pyramid                                                                                            | .6  |

|-----|---------------------------------------------------------------------------------------------------------------------|-----|

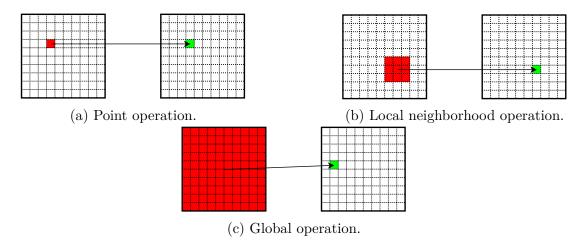

| 1.2 | Various types of image operations                                                                                   | 7   |

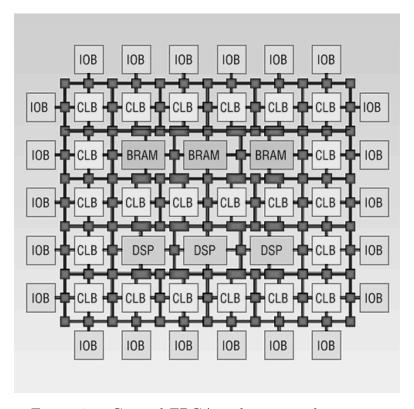

| 2.1 | General FPGA architecture alternative                                                                               | :0  |

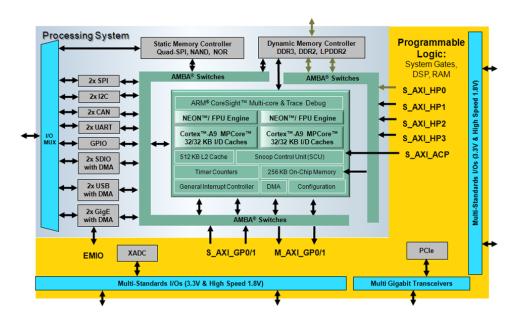

| 2.2 | Zynq SoC architecture                                                                                               | 1   |

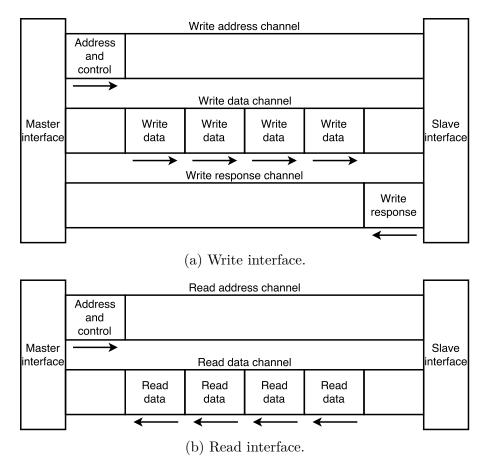

| 2.3 | AXI4 channels architecture                                                                                          | 2   |

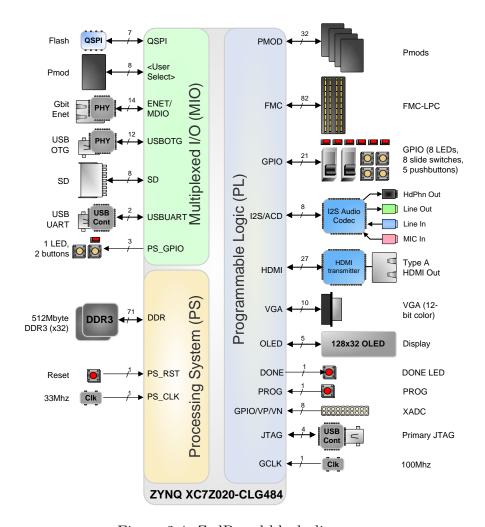

| 2.4 | ZedBoard block diagram                                                                                              | :4  |

| 2.5 | The ZedBoard development board                                                                                      | 4   |

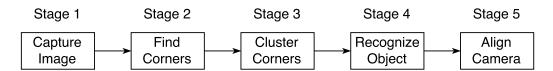

| 3.1 | Processing flow of the developed system                                                                             | 25  |

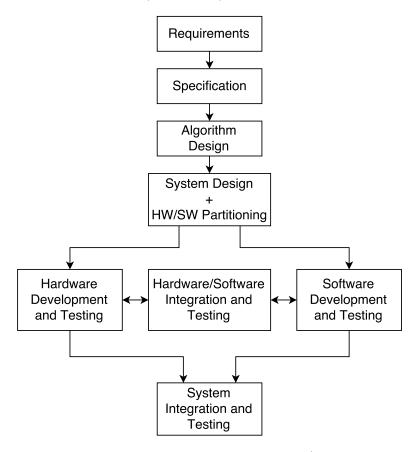

| 3.2 | The modern approach on hardware/software codesign                                                                   | 6   |

| 3.3 | Hardware/software partitioning of the implemented system                                                            | 8   |

| 3.4 | An example of (a) a flat region, (b) an edge and (c) a corner                                                       | 0   |

| 3.5 | Classification of image points based on their corner response                                                       | 1   |

| 3.6 | Harris Corner Detector block diagram                                                                                | 1   |

| 5.1 | General architecture of an AXI based accelerator                                                                    | 8   |

| 5.2 | Xillybus IP core interface to PS and PL on Zynq                                                                     | 8   |

| 5.3 | Xillybus-Lite IP core in systems hierarchy                                                                          | 9   |

| 5.4 | Examples of clock domain crossing syncronizers                                                                      | :1  |

| 5.5 | Finalized hardware architecture                                                                                     | 2   |

| 5.6 | Finalized software components architecture                                                                          | 2   |

| 6.1 | System bandwidth and FPGA memory resource utilization for various number of bands using a 16-bit Xillybus interface | 1.3 |

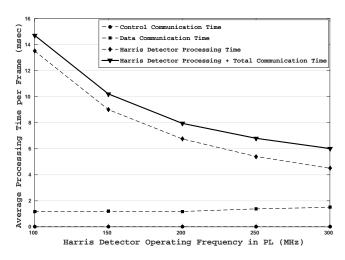

| 6.2 | Execution time vs PL clock frequency                                                                                |     |

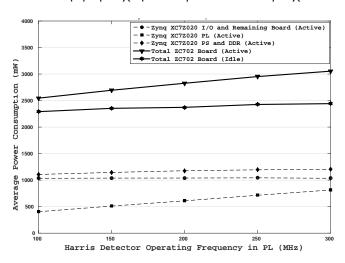

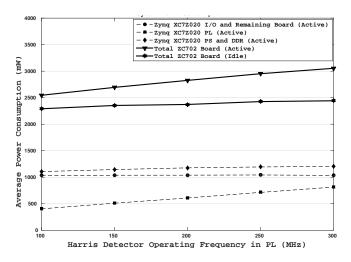

| 6.3 | Power Consumption vs PL clock frequency                                                                             |     |

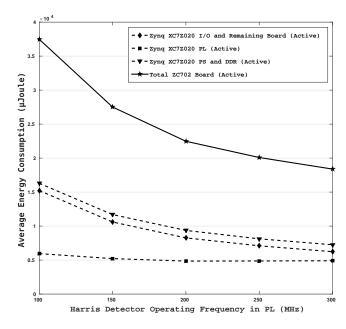

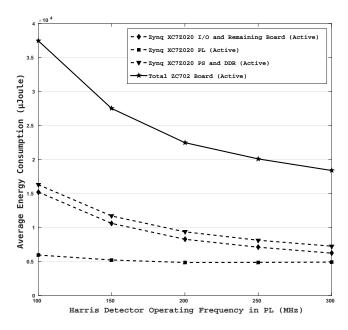

| 6.4 | Energy Consumption vs PL clock frequency                                                                            |     |

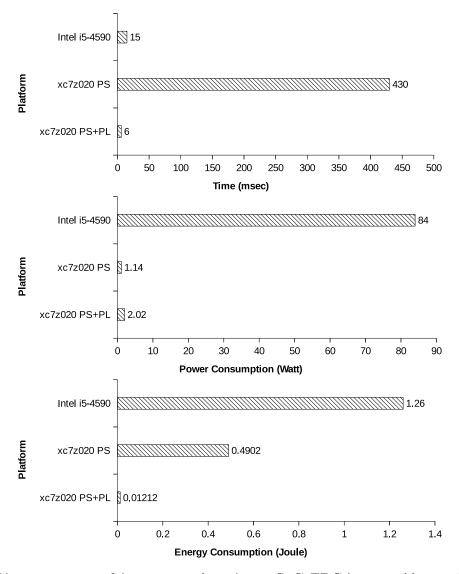

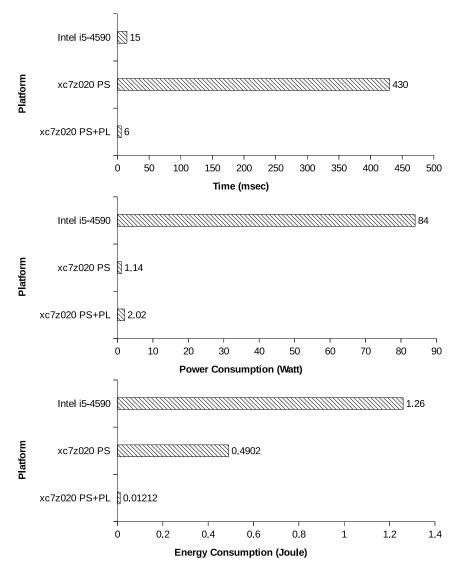

| 6.5 | Performance comparison of SoC FPGA implementation with alternative process-                                         |     |

|     | ing platforms                                                                                                       | 6   |

|     | U1                                                                                                                  | _   |

# List of Tables

| 3.1 | Profiling results for the processing steps of the developed system              | 27 |

|-----|---------------------------------------------------------------------------------|----|

| 6.1 | Operating frequency and resource utilization of the system analyzed in Xillybus |    |

|     | communication and Harris implementation                                         | 44 |

| 6.2 | Performance gain of SoC FPGA implementation versus alternative processing       |    |

|     | platforms                                                                       | 47 |

| 6.3 | Algorithm quality of the implemented system                                     | 47 |

# Listings

| 5.1 | Xillybus programming example      | 39 |

|-----|-----------------------------------|----|

| 5.2 | Xillybus-Lite programming example | 40 |

# Εκτεταμένη Περίληψη

#### Εισαγωγή

Σήμερα η συνεχής πρόοδος στην τεχνολογία έχει οδηγήσει στην ανάπτυξη πιο πολύπλοκων και υπολογιστικά απαιτητικών αλγορίθμων επεξεργασίας εικόνας. Πολλοί από αυτούς τους αλγόριθμους έχουν υιοθετηθεί σε ενσωματωμένα συστήματα τα οποία στοχεύουν σε μια ποικιλία εφαρμογών, όπως η αυτοχινητοβιομηχανία, 3D πλοήγηση, την επιτήρηση, χλπ. Ωστόσο, σε ενσωματωμένα συστήματα πραγματικού χρόνου, όπου η καθυστέρηρη μεταφοράς δεδομένων και τη κατανάλωση ισχύος διαδραματίζουν σημαντικό ρόλο, εφαρμογές λογισμικού προσανατολισμένες να εκτελούνται σε επεξεργαστές γενικής χρήσης δεν μπορούν να προσφέρουν ικανοποιητικές λύσεις. Αυτό προχύπτει από το γεγονός ότι οι επεξεργαστές έχουν περιορισμένες δυνατότητες παράλληλης επεξεργασίας για να υποστηρίξουν τις απαιτήσεις των εφαρμογών αυτών και καταναλώνουν σημαντικά ποσά ισχύος. Προκειμένου να ξεπεραστούν αυτά τα μειονεκτήματα και να αυξηθεί η απόδοση/watt, διάφορες προσεγγίσεις έχουν προταθεί όπου εξειδικευμένο υλικό χρησιμοποιείται παράλληλα με την CPU για την επιτάχυνση κρίσιμων τμημάτων ή ακόμη και ολόκληρων αλγορίθμων. Οι προσεγγίσεις αυτές βασίζονται σε διάφορους συνδυασμούς σε επίπεδο συστήματος, όπως CPU-DSP, CPU-GPU και CPU-FPGA. Ωστόσο, αυτό το είδος των συστημάτων πάσχουν από μειωμένη απόδοση που προχύπτει από την αύξηση της καθυστέρησης στην επιχοινωνία μεταξύ των διαφόρων συσχευών. Μια άλλη εναλλακτική λύση είναι η κατασκευή ASIC. Ωστόσο, η προσέγγιση αυτή θεωρείται αναποτελεσματική από την άποψη του χρόνου διάθεσης στην αγορά και το κόστος ανάπτυξης και υλοποίησης.

Τα τελευταία χρόνια, οι κατασκευαστές FPGA εισήγαγαν System-on-Chip (SoC) συσκευές, οι οποίες συνδυάζουν ενσωματωμένο επεξεργαστή(-ες) μαζί με προγραμματιζόμενη λογική FPGA στο ίδιο τσιπ (SoC FPGA). Η ενσωμάτωση αυτή επιτρέπει μεγαλύτερη απόδοση, εξοιχονόμηση ενέργειας και τη βελτίωση γενικά της επικοινωνίας, σε αντίθεση με απλές υλοποιήσεις FPGA που εξωτερικά επικοινωνούν με CPUs Αυτά τα σημαντικά πλεονεκτήματα μπορούν να αξιοποιηθούν σε ενσωματωμένα συστήματα πραγματικού χρόνου που στοχεύουν απαιτητικές υπολογιστικές εφαρμογές, όπως η επεξεργασία εικόνας, και να παρέγουν ελκυστικές λύσεις με εντυπωσιακές τιμές αποδόσεων/watt. Ακόμα κι αν τα SoC FPGAs παρέχουν μια μεγάλη σειρά από οφέλη, η διαδικασία ανάπτυξης μιας εφαρμογής σε αυτές την πλατφόρμες αποτελεί μια πολύπλοχη χαι χρονοβόρα διαδικασία. Οι κατασκευαστές SoC FPGA έχουν επενδύσει πολλή προσπάθεια για την προώθηση ειδικών εργαλείων και framework με στόχο να διευκολυνθεί η διαδικασία ανάπτυξης SoC συστημάτων. Σήμερα, έχουν σημειώσει σημαντική πρόοδο όσον αφορά την μείωση της προσπάθειας προγραμματισμού υλικού με την εισαγωγή της Σύνθεσης Υψηλού Επιπέδου (High Level Synthesis - HLS) [3]. Παρόλ' αυτά η ενσωμάτωση υλικού/λογισμικού και η εφαρμογή της κατάλληλης επικοινωνίας μεταξύ τους εξακολουθεί να παραμένει ένα πολύ επίπονο και δύσκολο έργο για τον μηχανικό. Αυτό είναι αποτέλεσμα της μεγάλης προσπάθειας που απαιτείται για την κατανόηση των χαμηλού επιπέδου λεπτομεριών των πρωτοχόλλων επιχοινωνίας, τη προσαρμογή των διεπαφών του επιταχυντή υλικού σε αυτά τα πρωτόκολλα και το cross-trigger debugging, προκειμένου να επιχυρώθει η σωστή ενσωμάτωση υλιχού/λογισμιχού.

#### Περιγραφή συστήματος και διαδικασία υλοποίησης

#### Πλατφόρμα Υλοποίησης

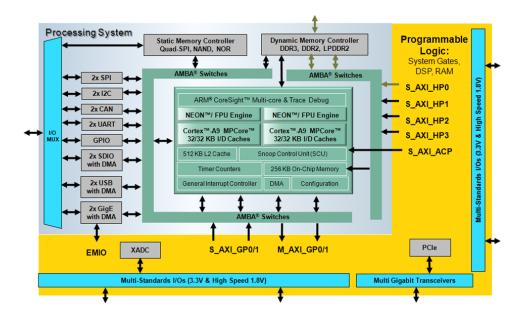

Περίπου το 2010 η Xilinx παρουσίασε την οικογένεια συσκευών Zynq-7000 All Programmable SoC, τις πρώτες συσκευές SoC που συνδύαζαν τα χαρακτηριστικά ενός Dual-Core ARM Cortex A9 επεξεργαστή (υποσύστημα PS) με προγραμματιζόμενη λογική (υποσύστημα PL), ή με άλλα λόγια έναν διπύρηνο επεξεργαστή με ένα FPGA.

Στη συσκευή Zynq, ο ARM Cortex-A9 είναι ένας επεξεργαστής που μπορεί να εκτελέσει λειτουργικά συστήματα, όπως το Linux, ενώ η προγραμματιζόμενη λογική βασίζεται στην αρχιτεκτονική 7-series FPGA της Xilinx . Η ενσωμάτωση ενός επεξεργαστή ARM με FPGA, σε μία μόνο συσκευή, προσφέρει στους προγραμματιστές τη δυνατότητα εφαρμογής ενοποιημένης προσέγγισης στην σχεδίαση υλικού/λογισμικού για ενσωματωμένα συστήματα και προσφέρει επίπεδα απόδοσης που λύσεις με δύο συσκευές (π.χ. CPU εξωτερικά συνδεδεμένη με ένα FPGA) δεν μπορούν να προσφέρουν λόγω του περιορισμένου εύρους ζώνης επικοινωνίας, της καθυστέρησης και της κατανάλωση ενέργειας τους. Η Xilinx έχει υιοθετήσει το δίαυλο δεδομένων για μικροελεγκτές ΑΜΒΑ και το πρωτόκολλο ΑΧΙ ως το κύριο μέσο επικοινωνίας μεταξύ του PS και της λογικής που υλοποιείται στο PL, όπως φαίνεται στην Εικόνα 1 όπου παρουσιάζεται η αρχιτεκτονική των συσκευών Zynq SoC.

Εικόνα 1: Αρχιτεκτονική συσκευών Zynq SoC.

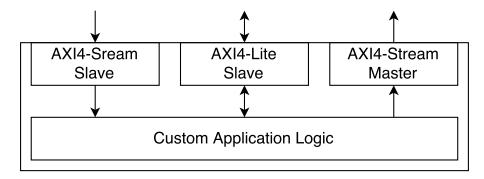

Το πρωτόχολλο ΑΧΙ είναι ένα πρωτόχολλο επιχοινωνίας που ανήχει στην οιχογένεια πρωτοχόλλων επιχοινωνίας για μιχροελεγχτές ARM AMBA. Το AMBA είναι ένα ανοιχτών προδιαγραφών πρότυπο για on-chip διασύνδεση, που επιτρέπει τη σύνδεση και τη διαχείριση πολλών ελεγχτών και περιφερειαχών σε ένα multi-master σύστημα. Απευθύνεται σε συστήματα υψηλής απόδοσης και συχνότητας. Η τέταρτη έκδοση του πρωτοχόλλου, ΑΧΙ4, έχει σχεδιαστεί και βελτιστοποιηθεί για να χρησιμοποιείται ως μέσο επιχοινωνίας μεταξύ πυρήνων υλιχού IP σε συστήματα υλοποιημένα με FPGA. Υπάρχουν τρεις τύποι διεπαφών ΑΧΙ4, καθεμία κατάλληλη για εφαρμογές με διαφορετιχές απαιτήσεις [14]:

- **AXI4** (or **AXI4-Full**): Διασύνδεση υψηλής απόδοσης, κατάλληλη για memory mapped επικοινωνία που επιτρέπει ριπές δεδομένων έως και 256 δεδομένα ανά διεύθυνση.

- **AXI4-Lite**: Μια παραλλαγή της διεπαφής AXI4-Full, που χρησιμοποιείται για memory mapped επικοινωνία μόνο. Αυτή η παραλλαγή δεν υποστηρίζει ριπές δεδομένων και έτσι

μόνο ένα δεδομένο ανά διεύθυνση μεταφέρεται.

• **AXI4-Stream**: Η διεπαφή αυτή ορίζει ένα μόνο κανάλι για μεταφορά δεδομένων συνεχούς ροής (streaming), επιτρέποντας ριπές δεδομένων απεριορίστου μεγέθους. Η σύνδεση είναι από τον Master στον Slave μόνο, οπότε αν χρειάζεται αμφίδρομη μεταφορά μεταξύ δυο περιφεριαχών, τα περιφερειαχά πρέπει να υλοποιούν συγχρόνως διεπαφές τύπου Master και Slave.

#### Ροή επεξεργασίας εικόνων

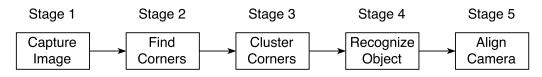

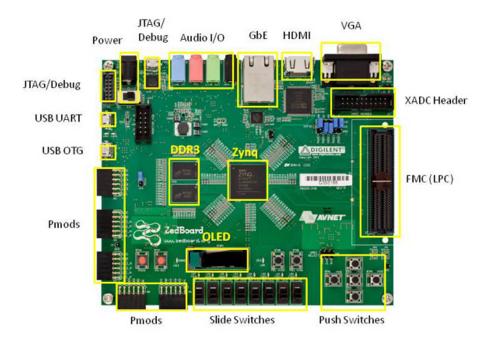

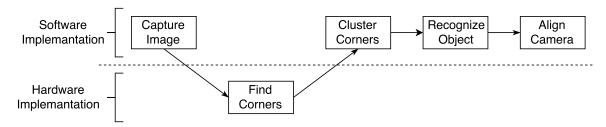

Εικόνα 2: Ροή επεξεργασίας συστήματος.

Η υλοποίηση του συστήματος βασίζεται σε ροή επεξεργασίας έξι σταδίων όπως φαίνεται στην Εικόνα 2. Τα στάδια αυτά περιγράφονται στη συνέχεια:

- Το 1° στάδιο αφορά τη λήψη της εικόνας με τη βοήθεια μιας κάμερας που συνδέεται με την πλατφόρμα. Η εικόνα αποθηκεύεται προσωρινά σε μια προκαθορισμένη περιοχή στην κύρια μνήμη του συστήματος ώστε να είναι έτοιμη προς επεξεργασία.

- Το 2° στάδιο είναι η επεξεργασία της εικόνας για να βρεθούν οι γωνίες, χρησιμοποιώντας το γνωστό αλγόριθμο εύρεσης γωνιών Harris. Στο στάδιο αυτό, η αποθηκευμένη εικόνα γίνεται είσοσδος στον Harris, ο οποίος με τη σειρά του εξάγει τις γωνίες που βρέθηκαν επιστρέφοντας τις συντεταγμένες τους και τη δύναμη της απόκρισης της γωνίας, δηλαδή μία τιμή που υποδηλώνει πόσο καλή γωνία είναι. Τα αποτελέσματα από αυτό το στάδιο αποθηκεύονται στη δική τους περιοχή στην κύρια μνήμη του συστήματος.

- Το 3° στάδιο είναι το στάδιο στο οποίο τα αποτελέσματα που προέχυψαν από το Στάδιο 2 επεξεργάζονται από έναν αλγόριθμο συσταδοποίησης (clustering alogrithm). Η έξοδος αυτού του σταδίου είναι ένας αριθμός από συστάδες (ομάδες). Στο τέλος αυτού του σταδίου κάθε γωνιά που βρέθηκε κατηγοριοποιείται σε μία από αυτές τις συστάδες και ένα αντιπροσωπευτικό σημείο (κεντροειδές) για κάθε ομάδα υπολογίζεται. Για αυτό το στάδιο δύο αλγόριθμοι συσταδοποίησης δοκιμάστηκαν, ο αλγόριθμος k-means και ο αλγόριθμος DBSCAN, και οι οποίοι θα παρουσιαστούν αργότερα.

- Το 4° στάδιο υπολογίζει τη γεωμετρία του αντικειμένου, με βάση τα κεντροειδή που υπολογίστηκαν στο Στάδιο 3, και τη συγκρίνει με ένα προκαθορισμένο αφηρημένο μοντέλο του αντικειμένου που θέλουμε να παρακολουθείται.

- Τέλος κατά το 5° στάδιο, εάν η ανίχνευση του αντικειμένου είναι επιτυχής, το σύστημα ενημερώνει πώς να κινήθει η κάμερα ώστε να ευθυγραμμιστεί με το αντικείμενο.

#### Συσχεδίαση Υλικού/Λογισμικού Συστήματος

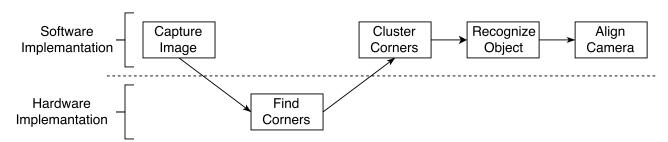

Η συσχεδίαση υλικού/λογισμικού αφορά στον ταυτόχρονο σχεδιασμό τόσο του λογισμικού όσο και του υλικού σε ένα σύστημα. Το λογισμικό είναι αυτό που εκτελείται σε επεξεργαστές, όπως η κεντρική μονάδα επεξεργασίας (CPU) και επεξεργαστές ψηφιακών σημάτων (DSP). Το υλικό υλοποιείται ως ASIC ή σε FPGA. Δεδομένου ότι τα συστήματα λογισμικού και υλικού έχουν

Πίνακας 1: Χρόνοι εκτέλεσης για τα στάδια επεξεργασίας του συστήματος.

| Capture Image        | Find Corners             | Cluster              | Corners              | Recognize Object     | Align Camora         |  |

|----------------------|--------------------------|----------------------|----------------------|----------------------|----------------------|--|

| Capture Image        | (Harris)                 | k-means              | DBSCAN               | Trecognize Object    | Aligh Camera         |  |

| $\ll 1 \text{ msec}$ | $\sim 430~\mathrm{msec}$ | $\ll 1 \text{ msec}$ |  |

διαφορετικά χαρακτηριστικά, ένας συνδυασμός τους έχει τη δυνατότητα να υοθετήσει τα καλύτερα χαρακτηριστικά και των δύο κόσμων. Ένα σημαντικό κομμάτι της συσχεδίασης είναι ο διαχωρισμός της εφαρμογής σε υλικό και λογισμικό. Σε απλές εφαρμογές ο διαχωρισμός με το «χέρι» μπορεί να είναι επαρκής. Σε πιο πολύπλοκες εφαρμογές, η εξερεύνηση του χώρου των δυνατών λύσεων είναι περιορισμένη και τα αποτελέσματα είναι απίθανο να είναι τα βέλτιστα. Για τον ανεπτυχθέν σύστημα, μετά από μέτρήσεις του χρόνου εκτέλεσης των σταδίων επεξεργασίας που αναφέρθηκαν νωρίτερα, ο διαχωρισμός με το «χέρι» υιοθετήθηκε λόγω του χαμηλού αριθμού των σταδίων επεξεργασίας που χρησιμοποιούνται στο σύστημα.

Στον Πίναχα 1 δίνεται ο χρόνος εκτέλεσης των διαφόρων σταδίων της επεξεργασίας. Με βάση τα αποτελέσματα αυτά στην Εικόνα 3 δίνεται ο τελικός διαχωρισμός των σταδίων επεξεργασίας σε υλικό και λογισμικό που χρησιμοποιούνται στο τελικό σύστημα.

Εικόνα 3: Διαχωρισμός υλικού/λογισμικού του συστήματος που υλοποιήθηκε.

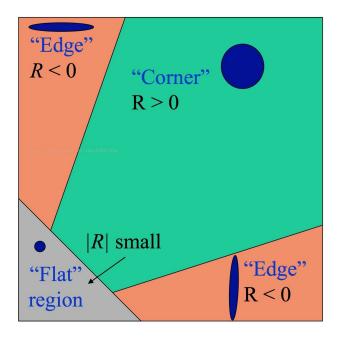

#### Αλγόριθμος ανίχνευσης γωνιών Harris

Η ανίχνευση γωνιών είναι μια πολύ κοινή λειτουργία σε πολλές εφαρμογές επεξεργασίας εικόνας και ο αλγόριθμος Harris [8] είναι αναμφισβήτητα ο πιο δημοφιλής αλγόριθμος για αυτό το σκοπό. Σε γενικές γραμμές, ο αλγόριθμος Harris δέχεται ως είσοδο μία grayscale εικόνα και ανιχνεύει τα πιο βασικά χαρακτηριστικά της, δηλαδή τις γωνίες (σημεία στην εικόνα που παρουσιάζουν σημαντική τοπική διακύμανση στην ένταση σε όλες τις κατευθύνσεις), οι οποίες μπορούν να ανιχνευτούν επανειλημμένα με αρκετή ακρίβεια κάτω από διαφορετικές συνθήκες (π.χ. φωτισμός, περιστροφή, κλπ). Η δημοφιλία του Harris και οι ποικίλες υπολογιστικές τεχνικές του (π.χ. συνέλιξη, σταθερής και κινητής υποδιαστολής αριθμητική) κάνουν τον Harris ένα ιδιαίτερα αντιπροσωπευτικό πυρήνα υλικού για τους σκοπούς της εργασίας.

Από αλγοριθμική άποψη, για κάθε εικονοστοιχείο, ο αλγόριθμος Harris υπολογίζει την δύναμη μιας γωνίας ("cornerness") σύμφωνα με τον τύπο  $I_x^2I_y^2-(I_xI_y)^2-0.04\cdot(I_x^2+I_y^2)^2$ , όπου  $I_x^2$ ,  $I_y^2$  και  $I_xI_y$  αντιπροσωπεύουν τα Gaussian-smoothed γινόμενα των παραγώγων της εικόνας, τα οποία υπολογίζονται μέσω ενός φίλτρου Sobel. Τιμές του cornerness που υπερβαίνουν ένα συγκεκριμένο όριο και οι αντίστοιχες τιμές των υπόλοιπων σε μια γειτονιά  $3\times 3$  του υπό εξέταση εικονοστοιχείου (αποτελούν τοπικό μέγιστο), ορίζουν γωνίες στην εικόνα. Αυτές οι γωνίες φιλτράρονται με την εφαρμογή μιας τετραγωνικής επιφάνειας στην προαναφερθείσα  $3\times 3$  περιοχή.

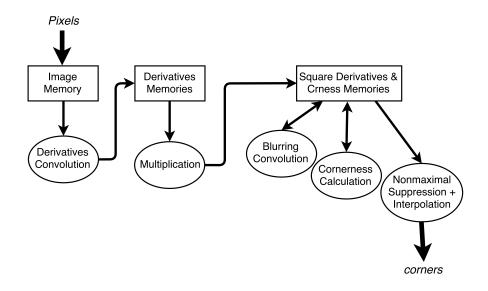

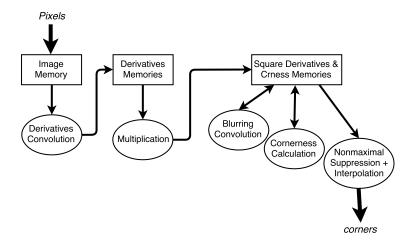

Στο FPGA, ο αλγόριθμος Harris επιταχύνεται σύμφωνα με την βαθιάς διοχέτευσης αρχιτεκτονική που φαίνεται στην Εικόνα 4, και η οποία περιγράφηκε σε VHDL. Τα εικονοστοιχεία της εικόνας φορτώνονται στην μνήμη "Image Memory", η οποία τροφοδοτεί τη μονάδα "Derivatives

Εικόνα 4: Μπλοκ διάγραμμα ανιχνευτή γωνιών Harris.

Convolution" με δύο διαδοχικές ριπές της εικόνας (1 εικονοστοιχείο ανά κύκλο) για να υπολογίσει τις παραγώγους της εικόνας dx και dy. Οι παράγωγοι της εικόνας τετραγωνίζονται και στη συνέχεια αποθηκεύονται προσωρινά σε διακριτές θέσεις μνήμης. Κάθε  $dx^2$ ,  $dy^2$  και dxdy προωθείται μεμονωμένα στην μονάδα "Bluring Convolution" για να παράγου μοναδικά τα  $I_x^2$ ,  $I_y^2$  and  $I_xI_y$  (οι προκύπτουσες τιμές αντικαθιστούν τις παλιές παραγώγους στη μνήμη). Στη συνέχεια τα τρία I προωθούνται παράλληλα στην μονάδα "Cornerness Calculator" (1 τριάδα  $\langle I_x^2, I_y^2, I_xI_y \rangle$  ανά κύκλο) για τον υπολογισμό του ανωτέρου μαθηματικού τύπου για κάθε εικονοστοιχείο (ένα cornerness ανά κύκλο, αντικαθιστά την αντιστοιχή του τριάδα I στη μνήμη). Οι τιμές cornerness προωθούνται με ριπή (μία ανά κύκλο) στην τελική μονάδα για να υποστούν non-maximal suppression και interpolation.

#### Συσταδοποίηση δεδομένων

Η συσταδοποίηση δεδομένων είναι μια διαδικασία ανάθεσης ενός συνόλου δεδομένων σε υποσύνολα (κατηγορίες), που ονομάζονται συστάδες (clusters), έτσι ώστε τα δεδομένα στο ίδιο υποσύνολο να είναι παρόμοια και δεδομένα σε διαφορετικά υποσύνολα να διαφέρουν αρκετά [10]. Η συσταδοποίηση δεδομένων συχνά συγχέεται με την ταξινόμηση, στην οποία τα αντικείμενα εκχωρούνται σε προκαθορισμένες κατηγορίες. Στην συσταδοποίηση δεδομένων, οι κατηγορίες πρέπει να καθοριστούν.

Σε αυτή την εργασία δύο αλγόριθμοι συσταδοποίησης χρησιμοποιούνται και αξιολογούνται ως προς το πόσο καλά εκτελούν το ρόλο τους στη ροή επεξεργασίας της εικόνας που παρουσιάστηκε νωρίτερα. Αυτοί οι αλγόριθμοι είναι ο k-means και ο DBSCAN και μια σύντομη περιγραφή τους δίνεται παρακάτω.

#### Ο αλγόριθμος k-means

Ο αλγόριθμος για συσταδοποίηση k-means [15] είναι ο πιο ευρέως χρησιμοποιούμενος διαμεριστικός αλγόριθμος συσταδοποίησης. Ξεκινά με την επιλογή k αντιπροσωπευτικών σημείων ως αρχικά κεντροειδή. Κάθε δεδομένο στη συνέχεια αντιστοιχίζεται στο πλησιέστερο κεντροειδές με βάση μία μετρίκη για την απόσταση που έχει επιλεγεί. Μόλις δημιουργηθούν οι συστάδες, τα κεντροειδή για κάθε συστάδα ανανεώνονται. Ο αλγόριθμος στη συνέχεια επαναλαμβάνει αυτά τα δύο βήματα μέχρι τα κενροειδή να μην αλλάζουν ή οποιοδήποτε άλλο εναλλακτικό κριτήριο σύγκλισης να εκπληρωθεί. Ο αλγόριθμος k-means είναι ένας greedy αλγόριθμος που εγγυημένα συγκλίνει σε

τοπικό ελάχιστο.

#### Ο αλγόριθμος DBSCAN

Ο αλγόριθμος DBSCAN [6] υπολογίζει την πυχνότητα των δεδομένων μετρώντας τον αριθμό των σημείων σε μια γειτονιά σταθερής αχτίνας και θεωρεί δύο σημεία ότι συνδέονται αν βρίσχονται στο εσωτερικό της γειτονιάς του άλλου. Ένα σημείο ονομάζεται σημείο πυρήνας αν στη γειτονιά του αχτίνας eps περιέχονται τουλάχιστον minPts σημεία, δηλαδή η πυχνότητα στη γειτονιά πρέπει να υπερβαίνει κάποιο όριο. Ένα σημείο q είναι άμεσα προσβάσιμο από ένα σημείο πυρήνα p, αν το q είναι εντός της αχτίνας eps του p. Δύο σημεία p και q λέμε ότι συνδέονται κατα πυχνότητα αν υπάρχει ένα τρίτο σημείο ο από το οποίο τα p και q είναι άμεσα προσβάσιμα. Μια συστάδα είναι τότε ένα σύνολο σημείων συνδεδεμένα κατά πυχνότητα, η οποία πυχνότητα είναι μέγιστη σε σχέση με την πυχνότητα-προσβασιμότητας. Ο θόρυβος ορίζεται ως το σύνολο των σημείων από το αρχικό σύνολο δεδομένων που δεν ανήκουν σε καμία από τις συστάδες. Η συσταδοποίηση με βάση την πυχνότητα είναι να βρεθούν όλες οι συστάδες με βάση τις παραμέτρους eps και minPts σε ένα συγκεχριμένο σύνολο δεδομένων.

#### Περιβάλλον λογισμικού

Το λειτουργικό σύστημα αποτελεί έναν σημαντικό παράγοντα που επηρεάζει την απόδοση του όλου συστήματος, καθώς και την προσπάθεια ανάπτυξης που απαιτείται για την εφαρμογή του. Παρά το γεγονός ότι σε ενσωματωμένα συστήματα μια ευρέως χρησιμοποιούμενη προσέγγιση είναι η ανάπτυξη λογισμικού σε bare-metal περιβάλλον, όπου ο προγραμματιστής μπορεί να τρέξει το λογισμικό απευθείας στο υλικό αντί να χρησιμοποιήσει κάποιο λειτουργικό σύστημα. Για εφαρμογές με χαμηλή πολυπλοκότητα αυτό οδηγεί σε πιο ελαφρύς λύσεις και σε εξοικονόμηση πόρων. Ωστόσο, η ανάπτυξη bare-metal εφαρμογών είναι μια επίπονη και χρονοβόρα διαδικασία λόγω της περιορισμένης διαθεσιμότητας σε βιβλιοθήκες λογισμικού και της ανάγκης προγραμματισμού σε χαμηλό επιπέδο των διαφόρων εξαρτημάτων του υλικού και των προγραμμάτων οδήγησης για συγκεκριμένες συσκευές. Ένα άλλο μειονέκτημα είναι ότι σε περιβάλλον bare-metal η εφαρμογή είναι single-threaded. Επιπλέον, δοκιμές και εντοπισμός σφαλμάτων μπορούν να πραγματοποιηθούν μέσω cross-compilation.

Η εναλλακτική λύση είναι να χρησιμοποιηθεί ένα λειτουργικό σύστημα ανοικτού κώδικα το οποίο προσφέρει μια πληθώρα από οφέλη. Τα πιο σημαντικά από αυτά τα οφέλη συνοψίζονται παρακάτω:

- Προσφέρει ένα υψηλό επίπεδο αφαίρεσης του συστήματος μέσα από μια ποικιλία βιβλιοθηκών για το υλικό. Ως εκ τούτου, ο προγραμματιστής μπορεί να επικεντρωθεί στην κύρια λειτουργικότητα της εφαρμογής χωρίς να ανησυχεί για λεπτομέρειες χαμηλού επιπέδου.

- Παρέχει έτοιμους προς χρήση οδηγούς συσκευών για ένα ευρύ φάσμα περιφερειακών.

- Μπορεί να γίνει χρήση multithreading για παράλληλη επεξεργασία.

- Προσφέρει ασφάλεια περιορίζοντας την εφαρμογή σε μία συγκεκριμένη περιοχή της μνήμης και προστατεύει από μη εξουσιοδοτημένες προσβάσεις στο υλικό.

Τα προαναφερθέντα οφέλη μπορούν να μειώσουν το χρόνο ανάπτυξης μιας εφαρμογής σημαντικά και προσφέρουν ένα πιο άνετο περιβάλλον για προγραμματισμό ενσωματωμένων συστημάτων. Με βάση αυτά τα πλεονεκτήματα έγινε χρήση λειτουργικού συστήματος για την γρήγορη ανάπτυξη του λογισμικού. Αρκετά λειτουργικά συστήματα ανοικτού κώδικα μπορούν να βρεθούν διαθέσιμα για SoC FPGAs βασισμένα σε επεξεργαστές ARM (π.χ. το Petalinux της Xilinx, το Linaro Ubuntu κ.λ.π.). Στην παρούσα εργασία χρησιμοποιήθηκε το Xillinux [1], μια διανομή Linux που

βασίζεται στο Ubuntu LTS 12.04 για ARM επεξεργαστές, λύση που ταιριάζει επίσης καλά με τον χρησιμοποιούμενο τρόπο επικοινωνίας PS-PL που περιγράφεται στη συνέχεια.

#### Υλοποίηση Επικοινωνίας PS-PL

Η επεξεργασία εικόνας απαιτεί υψηλά ποσοστά απόδοσης και χαμηλή καθυστέρηση ανταλαγής δεδομένων μεταξύ της CPU και του επιταχυντή υλικού. Λαμβάνοντας υπόψη αυτές τις απαιτήσεις, ένα πρωτόκολλο συνεχούς ροής (streaming protocol) είναι η πλέον ενδεδειγμένη λύση για τέτοιες εφαρμογές. Σε ένα πρωτόκολλο συνεχούς ροής οι μηχανισμοί χειραψίας (handshake mechanism) περιορίζονται στην αρχή της επικοινωνίας μεταξύ της CPU και του επιταχυντή υλικού και στη συνέχεια, έγκυρα δεδομένα μπορούν να μεταφερθούν για επεξεργασία σε κάθε διαδοχικό κύκλο ρολογιού. Η υλοποίηση μιας αποτελεσματικής επικοινωνίας συνεχούς ροής θα πρέπει να βασίζεται σε ένα μηχανισμό άμεσης προσπέλασης της μνήμης (DMA).

Η λογική DMA επιτρέπει στον επιταχυντή υλικού να έχει άμεση πρόσβαση στη μνήμη του συστήματος αποδεσμεύοντας την CPU από το να εμπλέκεται στην μεταφορά των δεδομένων. Ο μηχανισμός αυτός αυξάνει σημαντικά τη συνολική απόδοση του συστήματος, αφού η CPU μπορεί να συνεχίσει να επεξεργάζεται ταυτόχρονα άλλα δεδομένα. Στην παρούσα εργασία χρησιμοποιήθηκε αυτή η προσέγγιση για τη μεταφορά δεδομένων από το PS στο PL και αντίστροφα. Σε SoC FPGAs βασισμένα σε ARM ένα ευρέως χρησιμοποιούμενο πρωτόκολλο συνεχούς ροής είναι το AXI4-Stream, που βασίζεται στο πρωτόκολλο AXI4 [11]. Παρόλ΄ αυτά, η υλοποίηση του AXI4-Stream αποτελεί μεγάλη σχεδιαστική πρόκληση, λόγω του χρόνου που πρέπει να δαπανηθεί για την παραμετροποίηση των διεπαφών του επιταχυντή σύμφωνα με αυτό το πρωτόκολλο, την επικύρωση της ορθής λειτουργίας και την ενσωμάτωση στο σύστημα.

Όσο αφορά την μεταφορά σημάτων ελέγχου στον επιταχυντή υλικού (π.χ. start, enable, complete, κλπ.), καθώς και για την αρχικοποίηση του μηχανισμού DMA, χρησιμοποιούνται απλούστερα πρωτόκολλα επικοινωνίας. Τέτοια πρωτόκολλα βασίζονται σε ένα απλό μηχανισμό χειραψίας. Μια ευρέως χρησιμοποιούμενη προσέγγιση για SoC FPGAs που βασίζονται σε ARM επεξεργαστές είναι το πρωτόκολλο ΑΧΙ4-Lite.

Προκειμένου να διευκολυνθεί η υλοποίηση της επικοινωνίας μεταξύ της CPU και του επιταχυντή υλικού έγινε χρήση μίας γενικής λύσης, η οποία μπορεί να ενσωματωθεί στο σύστημα σχετικά γρήγορα και επιπλέον είναι προσαρμόσιμη ώστε να καλύπτει συγκεκριμένες ανάγκες της εκάστοτε εφαρμογής.

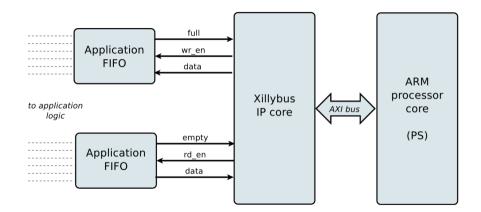

#### Πυρήνας υλικού Xillybus

Το Xillybus είναι μια οικογένεια από πυρήνες υλικού IP, που αναπτύχθηκαν από την εταιρεία Xillybus Ltd. [2], και αποτελείται από δύο πυρήνες που στοχεύουν εφαρμογές με διαφορετικές ανάγκες. Ο πρώτος πυρήνας υλικού, που ονομάζεται Xillybus IP, είναι μια λύση που υιοθετεί το μηχανισμό DMA, και προσφέρει έτοιμες προς χρήση διεπαφές επικοινωνίας συνεχούς ροής μεταξύ της CPU και του επιταχυντή υλικού στο PL. Παρέχει μια σειρά από χαρακτηριστικά για αύξηση της παραγωγικότητας. Αυτά τα χαρακτηριστικά συνοψίζονται στη συνέχεια:

- Ευελιξία όσον αφορά τον αριθμό των διεπαφών προς το PL και την προσαρμογή των παραμέτρων διαμόρφωσης για κάθε ξεχωριστή διεπαφή.

- Συμβατό με διαφορετικούς κατασκευαστές FPGAs (π.χ. Xilinx, Altera) και με διαφορετικά λειτουργικά συστήματα (π.χ. Linux, Windows).

- Εύκολο προγραμματιστικό μοντέλο, που υποστηρίζει διαφορετικές γλώσσες προγραμματισμού  $(\pi.\chi.\ C/C++,\ Java,\ Python\ κλπ.).$

• Πολύ απλό μοντέλο διασύνδεσης από την πλευρά του PL, χωρίς να απαιτείται επιπλέον προσπάθεια ανάπτυξης για την ενσωμάτωση με το επιταχυντή υλικού.

Η επιχοινωνία υλιχού/λογισμιχού με βάση το Xillybus μπορεί να πραγματοποιηθεί μέσω ενός τετριμμένου προγραμματιστιχού μοντέλου. Στον Κώδιχα 1 δίνετε ένα ενδειχτιχό παράδειγμα επιχοινωνίας μέσω Xillybus τόσο για την αποστολή όσο χαι για τη λήψη δεδομένων από/προς έναν επιταχυντή υλιχού στο PL. Οι διεπαφές επιχοινωνίας (π.χ. εγγραφής, ανάγνωσης) χειρίζονται ως αρχεία συσχευών (device files). Αξίζει να σημειωθεί ότι υπάρχει η δυνατότητα της ταυτόχρονης εκτέλεσης από την CPU άλλων διεργασιών μεταξύ των λειτουργιών εγγραφής χαι ανάγνωσης.

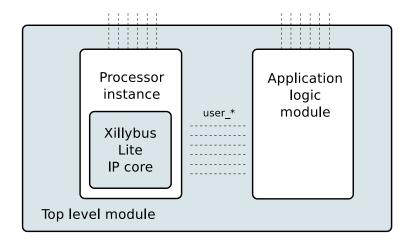

Ο δεύτερος πυρήνας υλικού, που ονομάζεται Xillybus-Lite IP, προσφέρει ένα επίπεδο αφαίρεσης στο πρωτόκολλο ΑΧΙ4-Lite, προσφέροντας εύκολη πρόσβαση σε καταχωρητές ή μονάδες μνήμης που υλοποιούνται στο PL. Μπορεί να γίνει χρήση πολλαπλών πυρήνων και το προγραμματιστικό μοντέλο του είναι εξίσου απλό όσο και του Xillybus IP, με ορισμένες εξαιρέσεις. Για να μπορεί να χρησιμοποιηθεί, η φυσική διεύθυνσή του πρέπει να αντιστοιχηθεί στο χώρο διευθύνσεων της εφαρμογής και η πρόσβαση μέσω αυτού σε πόρους στο PL πραγματοποιείται με αναθέσεις μεταβλητών. Ένα παράδειγμα του προγραμματιστικού μοντέλου του Xillybus-Lite δίνεται στον Κώδικα 2.

```

int write_fd , read_fd;

/* host application data buffer */

unsigned char *buffer;

/* open Xillybus write interface */

write_fd = open("/dev/

xillybus_write_device ,O_WRONLY);

/* write size of (buffer) number of bytes

write(write_fd, buffer, sizeof(buffer));

/* close Xillybus write interface */

close (wrire_fd);

map\_addr;

/* open Xillybus read interface */

read_fd = open("/dev/

xillybus_read_device " ,O_RDONLY) ;

/* read size of (buffer) number of bytes

read(read_fd, buffer, sizeof(buffer));

/* close Xillybus read interface */

close (read_fd);

```

Κώδικας 1: Προγραμματιστικό μοντέλο για το Xillybus IP.

```

int xillite fd;

void *map_addr;

/* open Xillybus-Lite interface */

xillite_fd = open("/dev/uio0",O_RDWR);

/* creates user address space for

mapping \ of \ Xillybus-Lite \ interfacing

map_addr = mmap(NULL, size, PROT_READ

PROT_WRITE, MAP_SHARED, xillite_fd ,0);

volatile unsigned int *pointer =

/* write to address */

*pointer = the_value_to_write;

/* read from address */

the_value_read_from_register = *pointer

/* deletes Xillybus-Lite mapping */

munmap(map_addr, size);

/* close Xillybus-Lite interface */

close(xillite_fd);

```

Κώδικας 2: Προγραμματιστικό μοντέλο για το Xillybus-Lite IP.

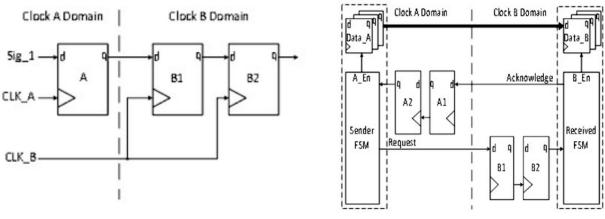

#### Τεχνικές Συγχρονισμού για Ενσωμάτωση Υλικού/Λογισμικού

Τα SoC FPGAs περιλαμβάνουν διάφορους τομείς που αναφέρονται στο PS, PL, και στη μνήμη και λειτουργούν με διαφορετική συχνότητα ρολογιού. Συνήθως, το ρολόι στο PL θεωρείται το ίδιο με αυτό των επιταχυντών υλικού και της υποδομής επικοινωνίας. Το πρόβλημα είναι ότι η υποδομή επικοινωνίας μπορεί να λειτουργήσει αξιόπιστα μέχρι μια συγκεκριμένη συχνότητα και ως εκ τούτου μπορεί να εμποδίσει την αύξηση της απόδοση ενός επιταχυντή, που ενδεχομένως μπορεί

να λειτουργήσει με μεγαλύτερη συχνότητα ρολογιού. Προχειμένου να ξεπεραστεί αυτό το εμπόδιο έχουν προταθεί διάφορες τεχνιχές cross-clock domain [4].

Όταν ασχολούμαστε με δεδομένα 1-bit μια ευρέως γνωστή τεχνική που βασίζεται στην χρήση συνχρονιστών με διπλά flip-flops μπορεί να χρησιμοποιηθεί. Αυτή η τεχνική είναι πολύ απλή στο σχεδιασμό, αλλά απαιτεί την εφαρμογή πρόσθετων περιορισμών κατά τη φάση της υλοποίησης και παρουσιάζει αναξιόπιστη συμπεριφορά για υψηλές συχνότητες ρολογιού. Μια άλλη λύση είναι να εμπλουτιστούν οι συνχρονιστές με διπλά flip-flop με ένα μηχανισμό χειραψίας, προκειμένου να μειωθεί η πιθανότητα διάδοσης λανθασμένων δεδομένων, αυξάνοντας όμως την καθυστέρηση διάδοσης των δεδομένων. Παρόλ΄ αυτά, η προσέγγιση αυτή απαιτεί επιπλέον προσπάθεια ανάπτυξης και μπορεί να οδηγήσει σε ανακριβή αποτελέσματα που οφείλονται στη διακύμανση της καθυστέρησης διάδοσης που παρουσιάζει κάθε σήμα του 1-bit όταν αυτά αποτελούν μέρος σημάτων πολλαπλών bit (π.χ. δίαυλος δεδομένων).

Μια εναλλακτική προσέγγιση για την επίτευξη του συγχρονισμού είναι η χρήση ασύγχρονων FIFO. Το κύριο πλεονέκτημα των ασύνγχρονων FIFO είναι ότι παρέχουν ασύγχρονη ανάγνωση και εγγραφή από περιοχές που λειτουργούν με διαφορετικές συχνότητες ρολογιού. Επιπλέον, η προσέγγιση αυτή παρέχει τα ακόλουθα πλεονεκτήματα:

- Όλοι οι κατασκευαστές FPGA παρέχουν έτοιμους προς χρήση προσαρμόσιμους πυρήνες IP

για ασύγχρονες μνήμες FIFO, οι οποίοι έχουν βελτιστοποιηθεί για χρήση στην εκάστοτε

συσκευή και η ενσωμάτωσή τους απαιτεί ελάχιστη προσπάθεια.

- Όταν ο επιταχυντής υλικού επεξεργάζεται ένα σύνολο δεδομένων, το επόμενο σύνολο δεδομένων μπορεί να αποθηκευεί προσωρινά και να είναι έτοιμο προς επεξεργασία αμέσως όταν χρειαστεί.

- Μη συμμετρικά πλάτη διαύλων δεδομένων μπορούν να χρησιμοποιηθούν στις διεπαφές εισόδου και εξόδου των μνημών FIFO. Για παράδειγμα πολλαπλά δεδομένα μπορούν να γραφούν παράλληλα και να διαβαστούν σειριακά από τον επιταχυντή υλικού.

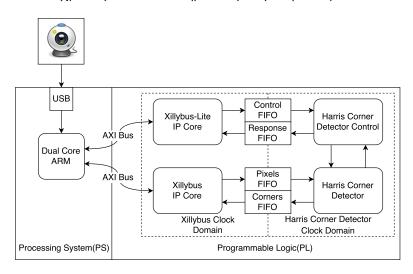

Λαμβάνοντας υπόψη τα παραπάνω πλεονεκτήματα, χρησιμοποιήθηκαν ασύγχρονες μνήμες FIFO στο αναπττυχθέν σύστημα μεταξύ του πυρήνα Xillybus IP και του Harris, τόσο για την μεταφορά σημάτων ελέγχου όσο και για τη μεταφορά δεδομένων. Σε γενικές γραμμές αυτή η προσέγγιση διασφαλίζει το σωστό συγχρονισμό του συστήματος με αμελητέα προσπάθεια.

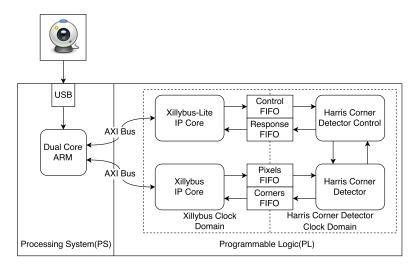

Εικόνα 5: Τελική αρχιτεκτονική υλικού.

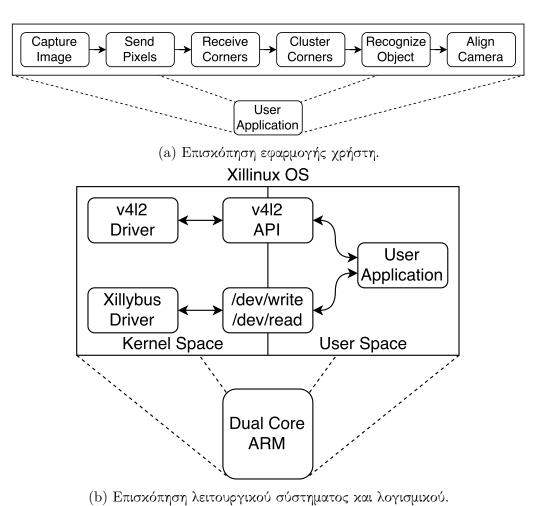

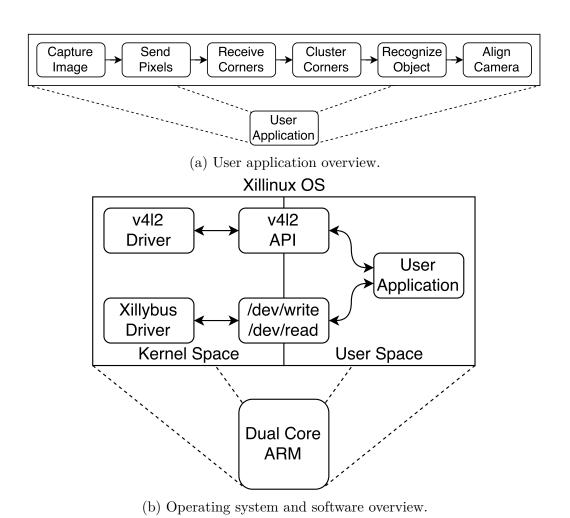

Εφαρμόζοντας όλες τις τεχνικές που περιγράφηκαν σε αυτή την ενότητα, η τελική αρχιτεκτονική του συστήματος δίνεται στις Εικόνες 5 και 6. Στην Εικόνα 5 παρουσιάζεται η αρχιτεκτονική του υλικού, όπου φαίνεται πως διασυνδέονται τα στοιχεία υλικού στο PL (π.χ. Harris, Xillybus) μεταξύ

Εικόνα 6: Τελική αρχιτεκτονική λογισμικού.

τους αλλά και με το PS, στην Εικόνα 6a δίνεται η ροή εκτέλεσης της εφαρμογής που εκτελεί ο χρήστης, ενώ στην Εικόνα 6b φαίνεται πως η εφαρμογή χρήστη επικοινωνεί με τα απαραίτητα περιφεριακά μέσω του λειτουργικού συστήματος.

## Πειραματικά Αποτελέσματα και Ανάλυση Επιδόσεων

Η ενότητα αυτή επικεντρώνεται στην παρουσίαση των επιδόσεων του συστήματός που αναπτύχθηκε με βάση τις χρησιμοποιούμενες τεχνικές που παρουσιάστηκαν νωρίτερα. Η ανάλυση των επιδόσεων γίνεται σε συνάρτηση με τη συχνότητα λειτουργίας του Harris και συγκρίνετε η υλοποίηση στη συσκευή Zynq XC7Z020 SoC FPGA με εναλλακτικές πλατφόρμες επεξεργασίας από πλευράς χρόνου εκτέλεσης, κατανάλωση ισχύος και ενέργειας. Επιπλέον το τελικό σύστημα αξιολογείται ως προς την ποιότητα των αποτελεσμάτων του.

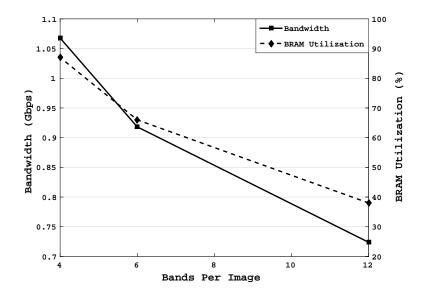

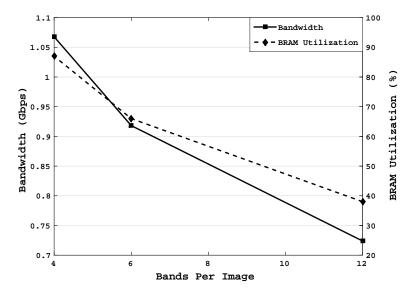

Όλα τα πειράματα διεξήθηκαν με τα ίδια δεδομένα εισόδου – εικόνα μεγέθους  $512 \times 384$  – τα οποία ήταν προαποθηκευμένα στη μνήμη του συστήματος και ίδιες τιμές για τις παραμέτρους διαμόρφωσης του αλγόριθμου Harris. Επιπλέον, διασφαλίστηκε ότι δεν εκτελούνταν περιττές διεργασίες στο PS. Επειδή το μέγεθος της εικόνας είναι πολύ μεγάλο για να χωρέσει στους πόρους μνήμης του FPGA, η εικόνα χωρίστηκε σε πολλές μικρότερες ζώνες, προκειμένου να επεξεργαστούν διαδοχικά (με επαναχρησιμοποίηση των πόρων του FPGA). Σημειώνεται ότι ο αριθμός των ζωνών έχει σημαντική επίπτωση στο συνολικό χρόνο εκτέλεσης. Πρώτον, οι ζώνες επικαλύπτουν η μία την άλλη για να εξασφαλιστεί λειτουργικά ισοδύναμο αποτελέσμα με τον αρχικό αλγόριθμο, και ως εκ τούτου, η αύξηση του αριθμού των ζωνών εισάγει μεγαλύτερη γενικά καθυστέρηση

στο χρόνο εκτέλεσης. Δεύτερον, όσο μικρότερος είναι ο αριθμός των ζωνών, λιγότερες κλήσεις συστήματος πρέπει να πραγματοποιηθούν για να μεταφερθούν προς το PL τα δεδομένα. Στην

Εικόνα 7: Εύρος ζώνης συστήματος και κατανάλωση πόρων μνήμης στο FPGA συναρτήσει του αριθμού των ζωνών ανα εικόνα χρησιμοποιώντας 16-bit εύρος διαύλου εγγραφής από το Xillybus.

Εικόνα 7 απεικονίζεται η σχέση μεταξύ της χρήσης πόρων μνήμης στο FPGA και του εύρους ζώνης επικοινωνίας συναρτήσει του αριθμού των ζωνών ανα εικόνα. Επιπλέον, μια άλλη παράμετρος που επηρεάζει το εύρος ζώνης της επικοινωνίας είναι το εύρος της διεπαφής εγγραφής των δεδομένων από το Xillybus. Προκειμένου να επιτευχθεί το μέγιστο θεωρητικό εύρος ζώνης των ~2,4 Gbps που προσφέρει το Xillybus IP, 32-bit εύρος διαύλου για τη μεταφορά των δεδομένων πρέπει να χρησιμοποιηθεί.

Σημειώνεται ότι για τα υπόλοιπα πειραμάτα, γίνεται χρήση 12 ζωνών ανα εικόνα, με εύρος διαύλου επικοινωνίας 16-bit. Με δεδομένη αυτή την υπόθεση, στον Πίνακα 2 δίνεται η συνολική χρήση πόρων και η συχνότητα λειτουργίας του συστήματος, όσο αφορά την πλευρά του PL και η οποία αναλύεται σε δύο μέρη, στον αλγόριθμο Harris (Harris Accelerator) και την επικοινωνία (Xillybus IP Cores). Αυτό που παρατηρείται είναι ότι το κόστος επικοινωνίας σε πόρους είναι

Πίνακας 2: Συχνότητα λειτουργίας και χρήση πόρων του συστήματος αναλύοντας τα στην επικοινωνία Xillybus και την υλοποίηση του Harris.

|                        |           | Harris Accelerator |             | Xillyb | ous IP Cores |

|------------------------|-----------|--------------------|-------------|--------|--------------|

| XC7Z020 PL Resources   | Available | Used               | Utilization | Used   | Utilization  |

| LUTs                   | 53200     | 11922              | 22%         | 2768   | 5%           |

| $\mathrm{DFFs}$        | 106400    | 14038              | 13%         | 2656   | 2%           |

| $\operatorname{BRAMs}$ | 140       | 52                 | 37%         | 1      | 1%           |

| DSPs                   | 220       | 54                 | 25%         | 0      | 0%           |

| Max. Operating Freq.   |           | 3                  | 800 Mhz     | ]      | 100 Mhz      |

σχετικά χαμηλό σε σχέση με το κόστος υλοποίησης του Harris.

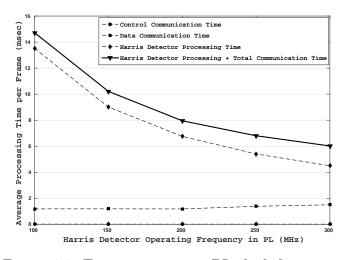

Στην Εικόνα 8 απεικονίζεται ο μέσος χρόνος εκτέλεσης του αλγορίθμου Harris στο PL και ο μέσος χρόνος επικοινωνίας PS/PL για την επεξεργασία μιας εικόνας ως συνάρτηση της συχνότητας λειτουργίας του Harris. Ο χρόνος επικοινωνίας αναλύεται σε δύο μέρη, τον χρόνο επικοινωνίας για τον έλεγχο και τον χρόνο επικοινωνίας για τα δεδομένα. Η επικοινωνία ελέγχου αναφέρεται στη χρήση του πυρήνα Xillybus-Lite IP που χρησιμοποιείται για τη μετάδοση των σημάτων ελέγχου,

Figure 8: Χρόνος εκτέλεσης εφαρμογής συναρτήσει της συχνότητας λειτουργίας του Harris στο PL.

ενώ η επιχοινωνία δεδομένων υποδηλώνει τον πυρήνα Xillybus IP για τη μεταφορά δεδομένων. Σημειώνεται ότι ο συνολιχός χρόνος επιχοινωνίας είναι σχεδόν σταθερός σε όλες τις συχνότητες λειτουργίας του Harris. Αυτό προχύπτει από το γεγονός ότι η επιχοινωνία βασίζεται στους πυρήνες Xillybus IP των οποίων η λειτουργία είναι σταθερή στα 100 Mhz. Από την άλλη πλευρά, ο χρόνος εχτέλεσης του Harris μειώνεται χαθώς αυξάνεται η συχνότητα του ρολογιού. Λαμβάνοντας υπόψη την Ειχόνα 8 αυτό που παρατηρείται είναι ότι το ποσοστό του συνολιχού χρόνου επεξεργασίας που δαπανάται στην επιχοινωνία αυξάνεται χαθώς αυξάνει η συχνότητα λειτουργίας του Harris. Για παράδειγμα, στα 100 Mhz το ποσοστό του χρόνο που δαπανάται στην επιχοινωνία είναι 8% του συνολιχού χρόνου επεξεργασίας, ενώ στα 300 MHz αυξάνει στο 25%.

Στην Εικόνα 9 παρουσιάζεται η κατανάλωση ισχύος του συστήματος ως συνάρτηση της συχνότητας λειτουργίας του Harris. Μετρήθηκε χωριστά η κατανάλωση ισχύος στο PL, στο PS (μαζί με

Ειχόνα 9: Κατανάλωση ισχύος συναρτήσει της συχνότητας λειτουργίας του Harris στο PL.

την μνήμη DDR) και τα περιφερειακά της πλακέτας κατά την επεξεργασία ενός μεγάλου αριθμού εικόνων. Παρουσιάζεται επίσης η συνολική κατανάλωση ισχύος της πλακέτας (PS, PL και I/O) σε κατάσταση αναμονής και εκτέλεσης της εφαρμογής. Αυξάνοντας τη συχνότητα λειτουργίας του Harris παρατηρείται ότι η κατανάλωση ισχύος αυξάνει γραμμικά στο PL ενώ στο PS υπάρχει μόνο μια πολύ μικρή μεταβολή που οφείλεται στην αύξηση του αριθμού των κλήσεων συστήματος που πρέπει να εξυπηρετηθούν στο ίδιο χρονικό διάστημα. Η μικρή αύξηση της ισχύος που παρατηρείται όταν το σύστημα είναι σε κατάσταση αναμονής είναι αποτέλεσμα της στατικής κατανάλωσης ισχύος στο PL. Επίσης παρατηρείται ότι η κατανάλωση ισχύος από τα I/O της συσκευής και τα

Εικόνα 10: Κατανάλωση ενέργειας συναρτήσει της συχνότητας λειτουργίας του Harris στο PL.

περιφερειακά της πλακέτας παραμένει σταθερή, καθώς δεν χρησιμοποιείται κάποιο από αυτά στο σύστημα που αναπτύχθηκε. Αξίζει να σημειωθεί ότι, ακόμα και αν το σύστημα καταναλώνει περισσότερη ισχύ σε υψηλότερες συχνότητες λειτουργίας του Harris, είναι ενεργειακά πιο αποδοτικό στις υψηλές συχνότητες για τον ίδιο φόρτο εργασίας, δηλαδή όταν εκτελείται η εφαρμογή. Οι μετρήσεις της ενέργειας που δίνονται στην Εικόνα 10 επιβεβαιώνουν αυτή την αρχή.

Για να αποδειχθεί η αποτελεσματικότητα του συστήματος που αναπτύχθηκε, όσο αφορά το χρόνο εκτέλεσης, την κατανάλωση ισχύος και ενέργειας, πραγματοποιήθηκε σύγκριση με εναλλακτικές πλατφόρμες επεξεργασίας. Η Εικόνα 11 παρουσιάζει τη σύγκριση των επιδόσεων της υλοποίησης σε SoC FPGA με υλοποιήσεις καθαρά σε λογισμικό που εκτελούνται σε επεξεργαστή ARM Cortex-A9 (μόνο PS) και επεξεργαστή Intel i5-4590. Με βάση αυτές τις μετρήσεις στον Πίνακα 3 παρουσιάζονται τα κέρδη σε απόδοση του συστήματος σε SoC FPGA έναντι των δύο εναλλακτικών πλατφορμών. Μπορεί να φανεί καθαρά ότι η SoC υλοποίηση είναι ανώτερη από άποψη απόδοσης/watt. Σημειώνεται ότι αν και η υλοποίηση σε ARM (XC7Z020 PS) καταναλώνει λιγότερη ισχύ η υλοποίηση του συστήματος σε SoC FPGA είναι πιο ενεργειακά αποδοτική.

Πίνακας 3: Κέρδος απόδοσης της υλοποίησης SoC FPGA με εναλλακτικές πλατφόρμες επεξεργασίας

|                    | XC7Z020 PS    | Intel i5-4590 |               |

|--------------------|---------------|---------------|---------------|

| Execution Time     | 71.6×         | $2.5 \times$  |               |

| Power Consumption  | $0.56 \times$ | $41.6 \times$ | XC7Z020 PS+PL |

| Energy Consumption | $40.4 \times$ | $104 \times$  |               |

Για να ολοκληρωθεί η αξιολόγηση, το σύστημα δοκιμάστηκε σε ένα πραγματικό σενάριο όπου το σύστημα παρακολουθούσε ενα στατικό αντικειμένο ορθογωνίου σχήματος και προσπαθούσε να ευθυγραμμίσει την κάμερα με το αντικείμενο. Ο σκοπός αυτού του πειράματος ήταν να δείξει πόσο καλά το τελικό σύστημα εκτελεί τη λειτουργία του υλοποιώντας τη ροή επεξεργασίας που παρουσιάστηκε νωρίτερα. Για το σκοπό αυτό με την κάμερα ελήφθησαν 1000 διαδοχικές εικόνες προκειμένου να τροφοδοτήσουν το σύστημα επεξεργασίας. Το πρώτο μέτρο αξιολόγησης ήταν να μετρηθεί ο αριθμός των εικόνων στις οποίες το σύστημα ήταν σε θέση να αναγνωρίσει το αντικείμενο σε τρεις διαδοχικές εικόνες το αποτέλεσμα ερμηνευόταν ως επιτυχής ευθυγράμμιση με το αντικείμενο και

Εικόνα 11: Σύγκριση των επιδόσεων της υλοποίησης SoC FPGA με εναλλακτικές πλατφόρμες επεξεργασίας

καταγραφόταν επίσης. Με βάση αυτές τις μετρήσεις, η ποιότητα των αλγορίθμων αξιολογήθηκε με τον υπολογισμό του ποσοστού επιτυχών ευθυγραμμίσεων, δηλαδή πόσες ομάδες των τριών διαδοχικών εικόνων μετρήθηκαν από το μέγιστο δυνατό των 333.

Ο Πίναχας 4 παρουσιάζει τις μετρήσεις που ελήφθησαν όταν η χάμερα μεταχινούνταν στον τρισδιάστατο χαρτεσιανό χώρο και επιτρεπόταν ή όχι να περιστρέφεται γύρω από τον οπτικό της άξονα. Όπως μπορεί να φανεί από τον πίναχα, όταν η χάμερα επιτρεπόταν να περιστραφεί και ο αλγόριθμος k-means χρησιμοποιούταν για τη συσταδοποίηση των γωνιών που έβρισχε ο Harris, μόνο σε ένα πολύ μιχρό αριθμό ειχόνων, το σύστημα ήταν σε θέση να αναγνωρίσει και να ευθυγραμμιστεί με το αντιχείμενο, έχοντας ποσοστό επιτυχίας μόνο 5%. Από την άλλη πλευρά, όταν χρησιμοποιήθηκε ο αλγόριθμος DBSCAN το ποσοστό επιτυχίας του συστήματος έφτασε το 75%. Αυτό το τεράστιο χάσμα μπορεί να δικαιολογηθεί από το γεγονός ότι ο k-means δεν μπορεί να διαχρίνει μεταξύ θορύβου (outliers) και χρήσιμων δεδομένων, ένα χαραχτηριστικό που είναι ενσωματωμένο στην λογιχή του αλγορίθμου DBSCAN. Τέλος όταν δεν επιτρεπόταν περιστροφή της χάμερας περι τον οπτικό άξονα, ο k-means βελτίωσε σημαντικά την αχρίβεια του συστήματος, αλλά όχι αρχετά ώστε να θεωρηθεί ως μια χαλή επιλογή για χρήση αχόμη και για αυτή την ειδιχή περίπτωση. Σε αντίθεση με την βελτίωση του k-means, ο αλγόριθμος DBSCAN αύξησε το ποσοστό επιτυχίας του ~2%.

Πίνακας 4: Ποιότητα αλγορίθμων υλοποιημένου συστήματος.

|                      | Processing pipeline with k-means |       | Processing pipeline with DBSCAN |           |  |

|----------------------|----------------------------------|-------|---------------------------------|-----------|--|

|                      | Dataset 1 Dataset 2              |       | Dataset 1                       | Dataset 2 |  |

| Rotation             | ✓                                | ×     | ✓                               | X         |  |

| Num. of recognition  | 127                              | 623   | 832                             | 863       |  |

| Successful alignment | 17                               | 175   | 250                             | 256       |  |

| Succes rate          | 5.1%                             | 52.8% | 75.1%                           | 76.9%     |  |

# Chapter 1

### Introduction

#### 1.1 Image Processing in Embedded Systems

Image processing is a rapidly growing area of computer science. Its growth has been fueled by technological advances in digital imaging, computer processors and mass storage devices. Fields which traditionally used analog imaging are now switching to digital systems, for their flexibility and affordability. Important examples are medicine, film and video production, photography, remote sensing and security monitoring. These and other sources produce huge volumes of digital image data every day, more than could ever be examined manually.

Image processing can be defined as the manipulation of an image for the purpose of either extracting information from the image or producing an alternative representation of the image. These operations can be grouped according to the type of data that they process as presented in Figure 1.1.

At the lowest level of the image processing pyramid are those operations which deal directly with the raw pixel values and can be though as prepossessing steps. Such operations includes distortion correction, contrast enhancement and filtering for noise reduction or edge detection etc. At the middle are those algorithms which utilize results obtained from the low level processing. Operations at this level can be grouped in two main classes named Segmentation and Classification. Segmentation operations such as thresholding, color detection, region growing and connected components labeling occur at the boundary between the low and intermediate levels. The purpose of segmentation is to detect objects or regions in an image, which have some common property. Classification operations use features of each region to identify objects or parts of objects, or to classify an object into one of several predefined categories. Classification transforms the data from regions to features, and then to labels. The data is no longer image

Figure 1.1: Image processing pyramid.

Figure 1.2: Various types of image operations.

based, but position information may be contained within the features, or be associated with the labels. At the highest level are those methods which attempt to extract semantic meaning from the information provided by the lower levels.

Figure 1.2 presents another way to categorize image processing operations based on how many input data must be processed to obtain a result or in other words the computational overhead associated with a given operation. These categories are

- Point operations: The output value at a specific coordinate depends only on the input value at that same coordinate. These operations have constant computation time as they just apply a simple transformation to the input data (Figure 1.2a).

- Local neighborhood operations: The output value at a specific coordinate depends not only on the input value of that specific coordinate, but also on the values on the neighborhood of that same coordinate. These operations have computation time proportional to the size of the region being processed (Figure 1.2b).

- Global operations: The output value at a specific coordinate depends on all the values in the input image. These operations have computation time proportional to the size of the image being processed (Figure 1.2c).

An embedded system is a computational unit embedded in electronic devices combining computer hardware and software. They are getting more and more common in cars, cameras, and even on washing machines and fridges. Some examples are auto-focus cameras, battery chargers, cell phones, temperature controllers etc. They are specifically designed and optimized for a particular function or a range of functions, to achieve shorter startup times, higher processing speed, greater reliability, low cost, low power consumption and/or some other property that a general-purpose computing system may not fulfill.

Embedded systems are particularly well suited to process data streams at high speeds with fairly small programs, that is why recent years have witnessed a dramatic increase in the use of embedded systems to run image processing applications. Other than on CPUs, data can be processed in a highly parallel fashion, with high speeds and low power requirements.

### 1.2 FPGAs in Image Processing

An FPGA based design is inherently parallel in nature. Different algorithm sequences will be mapped to different hardware modules in a FPGA, which operates concurrently. The main reasons for choosing FPGA as an embedded image processing platform are given below:

- 1. Parallel operation: FPGAs is a collection of logic elements which can be electrically re-wired. FPGAs implement an application by developing separate hardware for each functionality and hence such designs are inherently parallel. Each instruction that the programmer enters will be mapped into a separate hardware component. Thus, such a design is suitable in those image processing algorithms, which has significant amount of parallelism in them.

- 2. **Execution speed**: Due to parallel nature of FPGA's, the execution speed will be considerably increased. In practical applications, the image will be partitioned into different sub-blocks and then each block will be processed in parallel.

- 3. **Flexibility**: An FPGA based system provides full programming flexibility. Current FPGAs have sufficient logic resources to implement even complex applications in a single chip. Modern FPGA based systems will adaptively reconfigure according to the different operating environments. Hence FPGA based systems are inherently flexible.

- 4. Low power design: An FPGA based circuit implements several operations in one clock cycle simultaneously. This allow clock speed to be lowered significantly. In fact there will be a reduction in clock speed over a serial processor of the magnitude of 2 or more. Reduction in clock speed corresponds to reduction in dynamic power consumption of the system. Thus FPGA based design facilitates a low power design.

#### 1.3 Thesis Goals and Organization