### NATIONAL AND KAPODISTRIAN UNIVERSITY OF ATHENS

#### **SCHOOL OF SCIENCE**

### **DEPARTMENT OF INFORMATICS AND TELECOMMUNICATIONS**

#### **PROGRAM OF POSTGRADUATE STUDIES**

#### **PhD THESIS**

# Using scripting languages for hardware/software co-design

**Evangelos Logaras**

ATHENS

DECEMBER 2015

### ΕΘΝΙΚΟ ΚΑΙ ΚΑΠΟΔΙΣΤΡΙΑΚΟ ΠΑΝΕΠΙΣΤΗΜΙΟ ΑΘΗΝΩΝ

### ΣΧΟΛΗ ΘΕΤΙΚΩΝ ΕΠΙΣΤΗΜΩΝ ΤΜΗΜΑ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΤΗΛΕΠΙΚΟΙΝΩΝΙΩΝ

#### ΠΡΟΓΡΑΜΜΑ ΜΕΤΑΠΤΥΧΙΑΚΩΝ ΣΠΟΥΔΩΝ

#### ΔΙΔΑΚΤΟΡΙΚΗ ΔΙΑΤΡΙΒΗ

# Μέθοδοι συσχεδίασης υλικού/λογισμικού με χρήση scripting γλωσσών

Ευάγγελος Λογαράς

ΑΘΗΝΑ ΔΕΚΕΜΒΡΙΟΣ 2015

#### **PhD THESIS**

## Using scripting languages for hardware/software co-design

#### **Evangelos Logaras**

ADVISOR: Elias Manolakos, Associate Professor, UoA

### THREE-MEMBER ADVISING COMMITTEE:

Angela Arapoyanni, Professor, UoA

Elias Manolakos, Associate Professor, UoA

Antonios Paschalis, Professor, UoA

#### **SEVEN-MEMBER EXAMINATION COMMITTEE**

Kimon Anastasiadis Angela Arapoyanni

Professor, TEI of Athens Professor, UoA

Dimitrios Gizopoulos Elias Manolakos

Professor, UoA Associate Professor, UoA

Antonios Paschalis Dionysios Reisis

Professor, UoA Associate Professor, UoA

**Dimitrios Soudris**

Associate Professor, NTUA

Examination date: 4/12/2015

#### ΔΙΔΑΚΤΟΡΙΚΗ ΔΙΑΤΡΙΒΗ

# Μέθοδοι συσχεδίασης υλικού/λογισμικού με χρήση scripting γλωσσών

### Ευάγγελος Λογαράς

ΕΠΙΒΛΕΠΩΝ: Ηλίας Μανωλάκος, Αναπληρωτής Καθηγητής ΕΚΠΑ

ΤΡΙΜΕΛΗΣ ΕΠΙΤΡΟΠΗ ΠΑΡΑΚΟΛΟΥΘΗΣΗΣ:

**Αγγελική Αραπογιάννη**, Καθηγήτρια ΕΚΠΑ

Ηλίας Μανωλάκος, Αναπληρωτής Καθηγητής ΕΚΠΑ

Αντώνιος Πασχάλης, Καθηγητής ΕΚΠΑ

#### ΕΠΤΑΜΕΛΗΣ ΕΞΕΤΑΣΤΙΚΗ ΕΠΙΤΡΟΠΗ

Κίμων Αναστασιάδης Αγγελική Αραπογιάννη

Καθηγητής ΤΕΙ Αθήνας Καθηγήτρια ΕΚΠΑ

Δημήτριος Γκιζόπουλος Ηλίας Μανωλάκος

Καθηγητής ΕΚΠΑ Αναπ. Καθηγητής ΕΚΠΑ

Αντώνιος Πασχάλης Διονύσιος Ρεΐσης

Καθηγητής ΕΚΠΑ Αναπ. Καθηγητής ΕΚΠΑ

Δημήτριος Σούντρης

Αναπ. Καθηγητής ΕΜΠ

Ημερομηνία εξέτασης: 4/12/2015

#### Abstract

Multiprocessor embedded System on Chips (SoCs) include at least one programmable processor Intellectual Property (IP) core and several other hardware blocks, attached as domain-specific co-processors or peripheral units to the processor's data and control bus. Such a complex system architecture can take advantage of the reconfigurable, parallel processing and low power consumption features of modern FPGA devices. However these benefits cannot be fully delivered due to the lack of mature hardware/software co-design and rapid prototyping tools of embedded multi-processor SoCs.

In this doctoral dissertation we present a new methodology for the hw/sw co-design of multiprocessor embedded SoCs developed by exploiting the strengths of the popular Python scripting language. We exploit the features of Python to rapidly prototype and validate processor-centric SoC designs for Field Programmable Gate Arrays (FPGA). Specifically we developed methods to: (a) describe hardware blocks in Python and automatically generate synthesizable VHDL code, (b) describe in Python and simulate embedded systems both at the algorithmic/functional level as well as at the Register Transfer level, and automatically generate digital waveforms recording the results of the system's simulation that remains cycle-accurate and bit-true, (c) integrate into the design flow software development tools for programming in C the microprocessor core, and (d) generate scripts (Tcl) to ease integration of a complete hw/sw design with FPGA implementation tools that use logic synthesis to construct a physical implementation of the multi-processor SoC.

The above described hw/sw co-design and verification functionalities were implemented in the developed System Python (SysPy) tool that targets the prototyping of processor-centric embedded SoCs for FPGAs. In addition we have developed an Application Programming Interface (API) which enables easy data transfer between a SoC design, running in an FPGA device, and a host PC. The user can utilize Python software running on the PC and interact with C software running on the processor IP core of the SoC and in this way control data processing and storage in the FPGA.

Three sophisticated SoC's have been designed and implemented and are presented in detail as SoC design cases to demonstrate and assess the new co-design and co-simulation features of SysPy along with the supported design methodology. All three designs use a processor IP core as the main programmable system controller along with domain-specific hardware accelerator units designed for: a) image processing (edge detection), b) audio processing (music genre classification), and c) stochastic simulation of large-scale biochemical reaction networks (systems biology). These multi-processor SoC design cases demonstrate the evolution of the design methodology and each one of

them highlights different features of it.

We believe that with our methodology, developed using Python, we contribute towards the development of mature tools for the hw/sw co-design and rapid prototyping of FPGA-based embedded multiprocessor SoCs. To get useful feedback from end users community and contribute to the hw/sw co-design efforts we provide SysPy as an open source tool through GitHub, which is the largest online code repository.

Subject Area: Digital Design, Embedded Systems

**Keywords:** Python, Processor-centric SoCs, hw/sw co-design, VHDL, FPGA, SysPy.

### Περίληψη

Τα Ενσωματωμένα Συστήματα σε Ψηφίδα υλικού (embedded Systems on Chip - SoC) περιέχουν τουλάχιστον έναν προγραμματιζόμενο επεξεργαστή αλλά και διάφορες μονάδες (IP cores) που διασυνδέονται στους διαύλους ελέγχου και δεδομένων του ως περιφερειακά ή συνεπεξεργαστές ειδικού σκοπού. Ένας τέτοιος τύπος σύνθετης ψηφιακής αρχιτεκτονικής μπορεί να αξιοποιήσει τις δυνατότητες επαναπρογραμματισμού (reconfiguration) των μονάδων FPGA για να επιτύχει υψηλές επιδόσεις και χαμηλή κατανάλωση ενέργειας. Τις προοπτικές αυτές όμως περιορίζει η έλλειψη εργαλείων συσχεδίασης υλικού/λογισμικού για τη γρήγορη πρωτοτυποποίηση (rapid prototyping) ενσωματωμένων πολυεπεξεργαστικών SoCs.

Στην παρούσα διδακτορική διατριβή παρουσιάζουμε μεθοδολογία συσχεδίασης υλικού/λογισμικού για ενσωματωμένα πολυεπεξεργαστικά SoCs που υλοποιείται με τη χρήση της δημοφιλούς scripting γλώσσας προγραμματισμού Python. Αναδεικνύουμε εκείνα τα χαρακτηριστικά της γλώσσας Python που διευκολύνουν τη σχεδίαση ενσωματωμένων SoC με προγραμματιζόμενο επεξεργαστή (processorcentric) και την υλοποίηση τους σε μονάδες FPGA. Συγκεκριμένα αναπτύξαμε μεθόδους για: (α) υποστήριξη περιγραφών στοιχείων υλικού σε Python και αυτόματη μετατροπή τους σε VHDL, (β) χρήση περιγραφών Python για την προσομοίωση ενσωματωμένου συστήματος τόσο σε αλγοριθμικό επίπεδο λειτουργικότητας όσο και σε επίπεδο αρχιτεκτονικής RTL (Register Transfer level) και αυτόματη παραγωγή αρχείων ψηφιακών κυματομορφών με τα αποτελέσματα της ακριβούς προσομοίωσης (cycleaccurate και bit-true) του συστήματος. (γ) Υποστήριξη των απαραίτητων λειτουργιών για τον προγραμματισμό του επεξεργαστή σε γλώσσα C και (δ) παραγωγή αρχείων script (Tcl) για την εύκολη συνεργασία με υπάρχοντα εργαλεία λογικής σύνθεσης για τη φυσική υλοποίηση του συστήματος σε FPGA.

Οι παραπάνω λειτουργίες συσχεδίασης και προσομοίωσης υλικού/λογισμικού εντάχθηκαν στο εργαλείο System Python (SysPy) που στοχεύει στην αποδοτική πρωτοτυποποίηση ενσωματωμένων processor-centric SoCs για FPGAs. Επιπλέον αναπτύξαμε διεπαφή προγράμματος (API: Application Programming Interface) για την εύκολη ανταλλαγή δεδομένων μεταξύ του ενσωματωμένου επεξεργαστή στο FPGA και διασυνδεδεμένων Η/Υ. Με αυτή ο χρήστης μπορεί να αλληλεπιδρά με αντίστοιχο πρόγραμμα σε C που εκτελεί ο ενσωματωμένος επεξεργαστής, προκειμένου να ελέγχει προγραμματιστικά την επεξεργασία και καταχώρηση δεδομένων στο υλικό.

Για τον έλεγχο των δυνατοτήτων της μεθοδολογίας σχεδιάσαμε και υλοποιήσαμε με τη χρήση του SysPy τρία ενσωματωμένα πολυεπεξεργαστικά SoCs, τα οποία αναδεικνύουν τις νέες δυνατότητες συσχεδίασης και προσομοίωσης. Και τα τρία αυτά SoCs χρησιμοποιούν πυρήνα μικροεπεξεργαστή ως κύριο ελεγκτή του συστήματος αλλά και ειδικές μονάδες υλικού που σχεδιάστηκαν για την: α) επεξερ-

γασία εικόνων, β) επεξεργασία αρχείων ήχου και γ) στοχαστική προσομοίωση βιολογικών δικτύων. Η διαδικασία υλοποίησης των τριών πολυεπεξεργαστικών SoCs έγινε στα πλαίσια της εξέλιξης και βελτιστοποίησης του ίδιου του εργαλείου, ενώ κάθε σχέδιο χρησιμοποιεί και αναδεικνύει συγκεκριμένα του χαρακτηριστικά.

Πιστεύουμε ότι η μεθοδολογία σχεδίασης που αναπτύχθηκε με χρήση της Python συνεισφέρει σημαντικά προς την κατεύθυνση της συσχεδίασης υλικού/λογισμικού και πρωτοτυποποίησης για ενσωματωμένα συστήματα σε ψηφίδα υλικού, τομέα όπου σήμερα δεν υπάρχουν ώριμα διαθέσιμα εργαλεία. Επιπλέον το πρωτότυπο εργαλείο SysPy, αποτέλεσμα αυτής της έρευνας, παρέχεται ελεύθερα μέσω του GitHub που αποτελεί την μεγαλύτερη διαδικτυακή πλατφόρμα παροχής λογισμικού ανοιχτού κώδικα (open source) προκειμένου να λάβουμε χρήσιμες πληροφορίες από τους τελικούς χρήστες για την βελτίωση των λειτουργιών και της χρηστικότητάς του.

Θεματική περιοχή: Ψηφιακή Σχεδίαση, Ενσωματωμένα Συστήματα

**Keywords:** Python, πυρήνες επεξεργαστών, συσχεδίαση υλικού/λογισμικού, VHDL, FPGA, SysPy.

### Acknowledgements

First of all I would like to express my gratitude to my advisor Associate Professor Elias Manolakos for his support during my studies. I am really grateful that he gave me the opportunity to pursue my Ph.D. thesis by becoming part of his group. His deep knowledge in the field of embedded systems design gave me the opportunity to improve my technical skills and explore new ways and methods in digital hardware design. His advice helped me take important decisions in my career and under his guidance I learned how to use existing knowledge to expand and promote my ideas and in general how to interact in an academic environment.

I would also like to thank Professor Antonios Paschalis and Professor Angela Arapoyanni for their constant support and advice during my studies. I am also grateful to Professor George Tzanakos for his guidance and for the way he taught me to conduct research in his laboratory. His ideas and way of thinking will follow me in my professional career.

I also want to thank all my colleagues, officemates and friends who supported me during my studies. I express my gratitude to my good officemates and friends Symeon Chouvardas, Dimitrios Manatakis and Ioannis Stamoulias for the time we spent in the office working together and talking about science and the way to move on with our lives. I want to thank my colleague Orsalia Hazapis for working together, helping me improve my ideas and spending hours over electronic boards. I am grateful to Panagiotis Stamoulis for his support and friendship and for the countless hours we spent together discussing and solving all kinds of problems.

Finally I want thank my parents Elias and Christina, my sister Anna and my wife Rodica for their patience all these years, although sometimes I really feel that they do not have a clue about my research interests and my profession.

### List of Publications

#### Journals:

1. E. Logaras, O. G. Hazapis, and E. S. Manolakos. "Python to accelerate embedded SoC design: A case study for systems biology". ACM Transactions on Embedded Computing Systems, 13(4):84:1-84:25, March 2014.

### Conferences:

- 1. E. Logaras and E. S. Manolakos. "SysPy: using Python for processor-centric SoC design". In Proc. IEEE International Conference on Electronics, Circuits and Systems (ICECS), pages 762-765, 2010.

- O.G. Hazapis, E. Logaras, and E.S. Manolakos. "A soft IP core generating socs for the efficient stochastic simulation of large Biomolecular Networks using FPGAs". In Proc. IEEE International Conference on Electronics, Circuits and Systems (ICECS), pages 77-80, 2012.

- 3. E. Logaras, E. Koutsouradis and E.S. Manolakos. "Python facilitates the rapid prototyping and hw/sw verification of processor centric SoCs for FPGAs". submitted to the IEEE International Symposium on Circuits and Systems (ISCAS), October 2015.

# $\Sigma$ υνοπτική παρουσίαση της $\Delta$ ιδακτορικής $\Delta$ ιατριβής

### 1.1 Εισαγωγή

Η δραματική αύξηση της χωρητικότητας των μονάδων προγραμματιζόμενης λογικής Field Programmable Gate Array (FPGA) τα τελευταία χρόνια έχει αυξήσει σημαντικά και την πολυπλοκότητα των συστημάτων που μπορούν να υλοποιηθούν με τη χρήση τους. Η χρήση έτοιμων πυρήνων επεξεργαστών σε ένα σύστημα μπορεί να επιταχύνει σημαντικά τον απαιτούμενο χρόνο σχεδίασης, αλλά πρέπει επίσης η μεθοδολογία σχεδίασης να μπορεί να υποστηρίξει μία τέτοια αρχιτεκτονική. Σε αυτό το κεφάλαιο αναφέρονται τα κίνητρα τα οποία μας οδήγησαν στην ανάπτυξη του SysPy και επίσης η συνεισφορά του εργαλείου και της υποστηριζόμενης μεθοδολογίας στη σχεδίαση System on Chip με πυρήνα επεξεργαστή και χρήση FPGA. Στο τέλος του κεφαλαίου αναφέρουμε συνοπτικά το περιεχόμενο των κεφαλαίων που ακολουθούν.

### 1.1.1 Βασικοί στόχοι της διατριβής

Ο κύριος στόχος της έρευνας ήταν η ανάπτυξη ενός εργαλείου ψηφιακής σχεδίασης και προσομοίωσης κάνοντας χρήση περιγραφών υψηλού επιπέδου σε γλώσσα Python. Το SysPy στοχεύει ειδικότερα τη σχεδίαση ενσωματωμένων συστημάτων με πυρήνα επεξεργαστή διευκολύνοντας τη συσχεδίαση υλικού/λογισμικού. Τα μοναδικά χαρακτηριστικά της Python σε επίπεδο ανάπτυξης προγραμμάτων script σε περιβάλλον Linux σε συνδυασμό με τις δυνατότητες αντικειμενοστραφούς προγραμματισμού (ΟΟΡ: Object Oriented Programming) που επίσης παρέχει, μας βοήθησαν να αναπτύξουμε μεθόδους για την:

• δημιουργία μοντέλων υψηλού επιπέδου, π.χ. αριθμητικών μονάδων, στοιχείων μνήμης και λογικών μονάδων, διασύνδεση τους με τη χρήση περιγραφών Python και αυτόματη μετατροπή τους σε συνθέσιμες περιγραφές VHDL συμβατές με υλοποιήσεις σε FPGA.

- ανάπτυξη ενός μέσου το οποίο ελέγχει όλα τα υπόλοιπα εργαλεία που απαιτούνται για την ανάπτυξη υλικού και λογισμικού κατά της διαδικασία σχεδίασης ενός SoC με πυρήνα επεξεργαστή.

- επεξεργασία μεγάλου αριθμών αρχείων που παράγονται κατά τη διαδικασία ψηφιακής σχεδίασης, π.χ. αρχεία αναφορών, αρχεία ψηφιακών κυματομορφών κ.α.

Αντιλαμβανόμαστε ότι η σχεδίαση ενός πολύπλοχου ψηφιαχού ενσωματωμένου συστήματος δεν μπορεί να αυτοματοποιηθεί στο σύνολο της, προδιαγράψαμε όμως και αναπτύξαμε ένα λογισμικό σχεδίασης και προσομοίωσης το οποίο διασυνδέει τα περισσότερα εργαλεία σχεδίασης που απαιτούνται για την υλοποίηση ενός τέτοιους συστήματος. Με τη βοήθεια της Python και εργαλείων λεξικής ανάλυσης, καταφέραμε να υποστηρίξουμε περιγραφές υλιχού και λογισμικού σε υψηλό επίπεδο, οι οποίες όμως υποστηρίζουν και στοιχεία από τις ήδη υπάρχουσες γλώσσες περιγραφής υλικού, όπως είναι η VHDL και Verilog.

### 1.1.2 Συνεισφορά

Η συνεισφορά της έρευνας που διεξήχθει επιχεντρώνεται στο να αποδείξει ότι μία υψηλού επιπέδου γλώσσα όπως η Python μπορεί να χρησιμοποιηθεί για να σχεδιαστεί, να προσομοιωθεί και να υλοποιηθεί ένα ψηφιακό σύστημα. Οι δυνατότητες αυτές κρίνονται πολύ χρήσιμες, ειδικά στα αρχικά στάδια υλοποίησης, όταν πολλές μονάδες ενός συστήματος δεν έχουν ακόμα προδιαγραφεί πλήρως και επίσης δεν είναι γνωστός ο καταμερισμός των βασικών λειτουργιών ανάμεσα σε υλικό και λογισμικό. Όπως θα δούμε η Python είμαι μια ιδανική γλώσσα για να διαχειριστεί το πλήθος των εργαλείων που απαιτούνται για τη σχεδίαση ενός SoC. Δείξαμε ακόμα τον τρόπο με τον οποίο τα αντικειμενοστραφή και scripting χαρακτηριστικά της γλώσσας μπορούν εύκολα να διαχειριστούν την παραγωγή και επεξεργασία ASCII αρχείων, όπως VHDL, Tcl scripts, αρχεία XML κ.α. με στόχο τη γρήγορη προσομοίωση και διερεύνηση διαφορετικών αρχιτεκτονικών για την υλοποίηση ενός SoC.

Μελετώντας και συγκρίνοντας με τα εργαλεία σχεδίασης που ήδη υπάρχουν, θεωρούμε ότι μόνο το SysPy:

- 1. υποστηρίζει τη συσχεδίαση υλικού/λογισμικού με την δυνατότητα συνπροσομοίωσης μοντέλων υλικού σε Python και αλγορίθμων λογισμικού σε Python ή C.

- 2. κάνει χρήση μιας δημοφιλούς scripting γλώσσας για την περιγραφή της αρχιτεκτονικής ενός ψηφιακού συστήματος σε υψηλό επίπεδο (ADL: Architectural Description Language) [68]

και επιπλέον υποστηρίζει την προσομοίωση σε χαμηλό επίπεδο περιγραφών RTL αλλά και σε αλγοριθμικό επίπεδο συμπεριφοράς και αυτόματη παραγωγή αρχείων κυματομορφών Value Change Dump (VCD) για χρήση με δημοφιλή εργαλεία προσομοίωσης, όπως το ModelSim από την Mentor Graphics.

- 3. υποστηρίζει την *αυτόματη παραγωγή* συνθέσιμου κώδικα VHDL με χρήση παραμετροποιήσιμων συναρτήσεων Python.

- 4. υποστηρίζει σχεδίαση SoC με ενσωμάτωση δωρεάν διαθέσιμων πυρήνων επεξεργαστών, όπως ο Leon και ο OpenRISC.

- 5. διευκολύνει τη χρήση των εργαλείων σχεδίασης FPGA με την αυτόματη παραγωγή αρχείων script Tcl για την οδήγηση των εργαλείων λογικής σύνθεσης και φυσικής σχεδίασης και εκτέλεση τους σε περιβάλλον Linux για την παραγωγή αρχείων προγραμματισμού μονάδων FPGA της εταιρείας Xilinx.

Με αυτόν τον τρόπο το εργαλείο που σχεδιάσαμε κάνει χρήση των καλύτερων χαρακτηριστικών της Python για να περιγράψει την αρχιτεκτονική ενός SoC σε υψηλό επίπεδο, αλλά και για να αυτοματοποιήσει τα περισσότερα από τα βήματα σχεδίασης που απαιτούνται για την υλοποίηση του συστήματος στο υλικό.

### 1.1.3 Σύνοψη κεφαλαίων

Στην παρούσα διατριβή περιγράφουμε τη μεθοδολογία αλλά και τις δυνατότητες του εργαλείου που σχεδιάστηκε και επίσης παραθέτουμε ικανό αριθμό παραδειγμάτων σχεδίασης ώστε να γίνουν κατανοητά τα χαρακτηριστικά του, αλλά και να παρακινήσουμε τον μελλοντικό αναγνώστη να κάνει χρήση του εργαλείου που διατίθεται ελεύθερο. Για τους επεξεργαστές που χρησιμοποιούμε στα παραδείγματα σχεδίασης κάνουμε χρήση των περιγραφών τους για να τους υλοποιήσουμε (soft IP cores), σε αντίθεση με επεξεργαστές που είναι ήδη υλοποιημένοι στο υλικό μέσα σε μια μονάδα FPGA (hardwired cores). Οι επεξεργαστές που υποστηρίζονται στην τρέχουσα έκδοση του SysPy είναι α) ο μικροελεγκτής 8-bit AVR ATmega128 ATmega128 [76], ο οποίος παρέχεται μέσα από την κοινότητα του OpenCores [73] για τη σχεδίαση ενός συστήματος επεξεργασίας εικόνων και β) ο επεξεργαστής 32-bit Leon3 [11], από την Aeroflex Gaisler, για ένα σύστημα επεξεργασίας ήχου και ένα σύστημα επεξεργασίας βιολογικών δεδομένων. Δοκιμές σχεδίασης επίσης πραγματοποιήσαμε και με τη χρήση του επεξεργαστή 32-bit OpenRISC [29], επίσης από το OpenCores.

Το ελληνικό κείμενο αποτελεί μια ευρεία περίληψη του αγγλικού κειμένου της διατριβής. Η οργάνωση των κεφαλαίων της διατριβής στο ελληνικό κείμενο έχει ως εξής:

- στο Κεφάλαιο 2 γίνεται ανάλυση της σχετικής βιβλιογραφίας και συγκρίνονται οι δυνατότητες του SysPy με άλλα σχετικά εργαλεία ψηφιακής σχεδίασης. Γίνεται αναφορά επίσης στους βασικούς λόγους για τους οποίους κάναμε χρήση της Python.

- στο Κεφάλαιο 3 παρουσιάζονται τα κύρια χαρακτηριστικά και οι λειτουργίες του εργαλείου.

- στο Κεφάλαιο 4 αναλύεται η μεθοδολογία υλοποίησης των τριών παραδειγμάτων σχεδίασης και ο τρόπος με τον οποίο κάναμε χρήση των δυνατοτήτων που περιέχει σε κάθε περίπτωση. Αναφέρονται επίσης τα αποτελέσματα της υλοποίησης στη μονάδα FPGA που είχαμε στη διάθεση μας. Γίνεται αναφορά επίσης στη χρήση της μεθόδου BDTi για μία αρχική ποσοτική αξιολόγηση των χαρακτηριστικών και της χρηστικότητας του SysPy.

- στο Κεφάλαιο 5 συνοψίζουμε τα αποτελέσματα της διατριβής καθώς και πιθανές μελλοντικές

βελτιώσεις και επεκτάσεις στις ήδη υπάρχουσες δυνατότητες.

### 1.2 Σχετική βιβλιογραφία

Για την ανάπτυξη μιας εφαρμογής πρέπει κάθε φορά να επιλέγεται το κατάλληλο προγραμματιστικό περιβάλλον. Στην περίπτωση μας, η Python χρησιμοποιήθηκε για την ανάπτυξη του εργαλείου αλλά και σαν γλώσσα περιγραφής για την μοντελοποίηση στοιχείων υλικού και λογισμικού. Σε αυτό το κεφάλαιο αιτιολογούμε τη χρήση της Python για την ανάπτυξη ενός εργαλείου που στοχεύει τη σχεδίαση ψηφιακών συστημάτων. Επίσης κάνουμε αναφορά στον τρόπο με τον οποίο οι σύγχρονες διατάξεις FPGA υποστηρίζουν τη σχεδίαση με ενσωματωμένους πυρήνες επεξεργαστών. Επιπλέον γίνεται αναφορά σε εφαρμογές στις οποίες έχει χρησιμοποιηθεί η Python, έτσι ώστε να βοηθήσουμε τον αναγνώστη να εκτιμήσει τις δυνατότητες της γλώσσας, ενώ ειδική αναφορά γίνεται σε εργαλεία ψηφιακής σχεδίασης στα οποία χρησιμοποιείται η Python και γίνεται σύγκριση των χαρακτηριστικών τους με τα αντίστοιχα του SysPy.

### 1.2.1 Ενσωματωμένα συστήματα με πυρήνες επεξεργαστών

Στα περισσότερα ενσωματωμένα συστήματα που υλοποιούνται σε μονάδες προγραμματιζόμενης λογικής χρησιμοποιείται πλέον τουλάχιστον ένας πυρήνας προγραμματιζόμενου επεξεργαστή. Ο επεξεργαστής λειτουργεί σαν ελεγκτής των διαφόρων πρωτοκόλλων επικοινωνίας που διασυνδέουν το σύστημα με εξωτερικές μονάδες. Το λογισμικό που εκτελεί ο επεξεργαστής υλοποιεί τα υψηλά επίπεδα των πρωτοκόλλων επικοινωνίας, όπως π.χ. στην περίπτωση του Ethernet τον διαχωρισμό των δεδομένων σε πακέτα δεδομένων, η διαχείριση των οποίων είναι αρκετά δύσκολη αν πρέπει να γίνει στο υλικό με χρήση μηχανών καταστάσεων. Ο επεξεργαστής επίσης διαχειρίζεται και την ροή δεδομένων προς άλλους επεξεργαστές ειδικού σκοπού που συνδέονται σαν περιφερειακές μονάδες.

Οι πλέον πρόσφατες "οικογένειες" μονάδων FPGA, όπως η σειρά Virtex-7 από την Xilinx και η σειρά Arria-V από την Altera, ενσωματώνουν διπύρηνους επεξεργαστές ARM απευθείας στο υλικό (hardwire cores), οι οποίοι επικοινωνούν με το υπόλοιπα στοιχεία προγραμματιζόμενης λογικής στο FPGA μέσω ειδικών διαύλων ελέγχου και δεδομένων. Ο νέος αυτός τύπος FPGA αναφέρεται ως προγραμματιζόμενο SoC, όπου μπορούν να επαναπρογραμματιστούν ταυτόχρονα στοιχεία λογισμικού και υλικού. Επίσης οι απαραίτητες τροποποιήσεις έχουν γίνει και στο παρεχόμενο λογισμικό σχεδίασης από τις εταιρείες FPGA, ώστε να υποστηρίζει νέες μεθοδολογίες σχεδίασης βασισμένες στις νέες δυνατότητες των FPGAs. Το νέο λογισμικό σχεδίασης υποστηρίζει μεθόδους σχεδίασης χρησιμοποιώντας πληθώρα έτοιμων μονάδων (block oriented design) που είναι συμβατές και μπορούν να συνδεθούν εύκολα σαν περιφερειακές μονάδες του επεξεργαστή. Αυτό ο τρόπος σχεδίασης επιταχύνει σημαντικά τον χρόνο υλοποίησης ενός processor-centric SoC. Αν λάβουμε επίσης υπόψιν και τη μειωμένη κατανάλωση ισχύος που έχουν οι νέες μονάδες FPGA, μπορούμε πλέον να συγκρίνουμε μια υλοποίηση FPGA με την αντίστοιχη σε μονάδα Application Specific Integrated Circuit (ASIC). Αν βέβαια απαιτείται μαζική παραγωγή ενός ολοκληρωμένου κυκλώματος, τότε από άποψη κόστους η λύση του ASIC παραμένει η μόνη επιλογή.

Τα προγραμματιζόμενα SoC θα γίνονται όλο και πιο δημοφιλή, σε σχεδιαστές υλικού αλλά και λογισμικού, όσο το πλήθος των έτοιμων λογικών μονάδων που είναι διαθέσιμες στα εργαλεία σχεδίασης θα αυξάνεται. Εφαρμογές που απαιτούν μεγάλη επεξεργαστική ισχύ, όπως εφαρμογές επεξεργασίας ήχου, εικόνας ή ελεγκτές δικτύου δεδομένων έχουν ήδη υλοποιηθεί σε μονάδες FPGA, κάνοντας χρήση του μεγάλου πλήθους έτοιμων αριθμητικών μονάδων στο υλικό που χρησιμοποιούνται για να εκτελέσουν τους απαραίτητους υπολογισμούς. Βασικός παράγοντας προς αυτή την κατεύθυνση είναι η ευκολία που θα παρέχουν τα διαθέσιμα εργαλεία σχεδίασης στην σύνδεση του προγραμματιζόμενου επεξεργαστή με άλλους επεξεργαστές ειδικού σκοπού και τις περιφερειακές μονάδες που διαχειρίζονται τα πρωτόκολλα επικοινωνίας του SoC.

### 1.2.2 Σχεδίαση υλικού με χρήση της Python

Η γλώσσα Python [2] είναι μια γλώσσα ανοιχτού λογισμικού η οποία αναπτύχθηκε από τον Guido van Rossum. Είναι μια γλώσσα υψηλού επιπέδου που χαρακτηρίζεται από εύκολη αναγνωσιμότητα του κώδικα λόγω της εύκολης σύνταξης που έχουν οι εντολές της. Υποστηρίζει όλες τις γνωστές μεθόδους προγραμματισμού, όπως τη δημιουργία ακολουθιακών προγραμμάτων (όπως η C), προγραμμάτων script και αντικειμενοστραφή προγραμματισμό. Ένα πρόγραμμα Python μπορεί να εκτελεστεί σαν script σε περιβάλλον λειτουργικού συστήματος Linux ή ακόμα και να συνδυαστεί με την εκτέλεση προγραμμάτων C/C++. Η Python είναι εξαιρετικά δημοφιλής στους σχεδιαστές λογισμικού, κυρίως λόγω της απλής σύνταξης που υποστηρίζει και είναι διαθέσιμη σε όλες τις εκδόσεις του λειτουργικού συστήματος Linux. Παρέχει επίσης μέσω των βιβλιοθηκών της μεγάλο αριθμό έτοιμων μεθόδων για διάφορες λειτουργίες. Μερικές από τις πιο γνωστές βιβλιοθήκες της γλώσσας είναι: α) το NumPy και το SciPy [62] με τη χρήση των οποίων μπορεί να αναπτυχθεί κώδικας σε Python, με σύνταξη παρόμοια με της γλώσσας Matlab, για την εκτέλεση υπολογισμών διανυσματικής και γραμμικής άλγεβρας, β) το matplotlib [43] το οποίο επιτρέπει τη δημιουργία γραφικών παραστάσεων με τη βοήθεια του SciPy και γ) το Scrapy το οποίο παρέχει μεθόδους για την ανεύρεση και επεξεργασία πληροφοριών στο διαδίκτυο.

Η Python έχει χρησιμοποιεί στο παρελθόν για την ανάπτυξη δημοφιλών εργαλείων σχεδίασης λογισμικού και υλικού, ειδικότερα όπου απαιτείται παραγωγή και επεξεργασία αρχείων τύπου ASCII. Τα PyCells [22] είναι δομές γραμμένες σε Python που εκφράζουν τη λειτουργία ψηφιακών και αναλογικών μονάδων και χρησιμοποιούνται για σχεδίαση ASIC. Τα PyCells χρησιμοποιούνται ήδη σε εργαλεία σχεδίασης ολοκληρωμένων κυκλωμάτων από τις εταιρίες Cadence και Synopsys. Η Python επίσης χρησιμοποιήθηκε και στην ανάπτυξη της πλατφόρμας VIPER [90] που χρησιμοποιείται για τον προγραμματισμό ενσωματωμένων συστημάτων, όπως του συστήματος Arduino [12] [18], που χρησιμοποιείται για την υλοποίηση εφαρμογών ελέγχου.

Εφόσον ο τρόπος σύνταξης της Python ήταν ήδη δημοφιλής και αποδεκτός από ένα ευρύ κοινό, προσπαθήσαμε κατά την ανάπτυξη του SysPy να κάνουμε χρήση των πιο κοινά αποδεκτών και συμβατών χαρακτηριστικών της γλώσσας και να αποφύγουμε τρόπους περιγραφής και προγραμματισμού ασύμβατους με τη γλώσσα και τα κοινά αποδεκτά πρότυπα της. Τα δύο πιο σημαντικά χαρακτηριστικά της γλώσσας που μας ώθησαν στη χρήση της για την ανάπτυξη ενός εργαλείου ψηφιακής σχεδίασης είναι τα ακόλουθα:

• Ενσωμάτωση και χρήση μέσα από ένα κοινό προγραμματιστικό περιβάλλον όλων των διαφορετικών εργαλείων και προγραμμάτων που απαιτούνται για τη συσχεδίαση υλικού/λογισμικού κατά τη διαδικασία σχεδίασης ενός SoC.

• Υποστήριξη τρόπου σύνταξης με τον οποίο μπορεί να περιγραφεί η λειτουργικότητα μονάδων υλικού σε χαμηλό επίπεδο Register Transfer Level (RTL), αλλά και σε υψηλό επίπεδο με χρήση μεθόδων στην Python οι οποίες παράγουν αυτόματα τις απαιτούμενε περιγραφές υλικού σε γλώσσα VHDL.

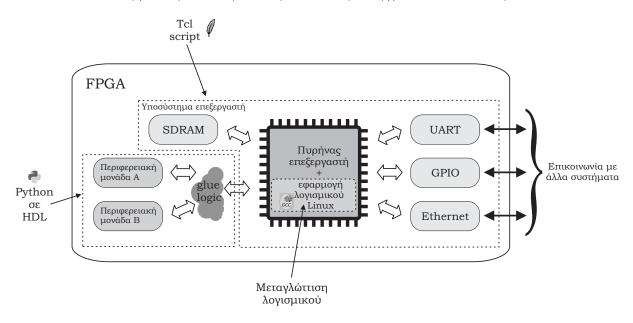

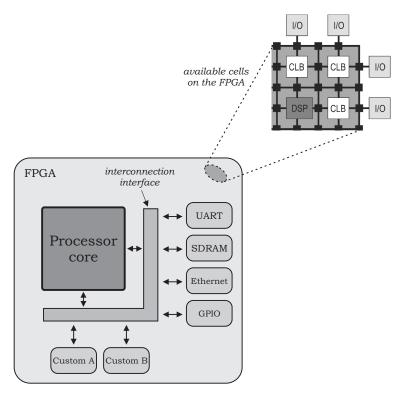

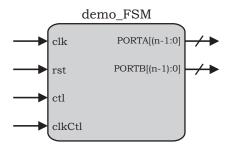

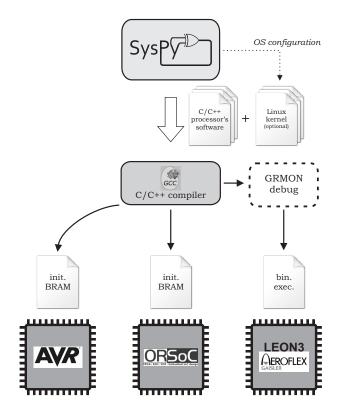

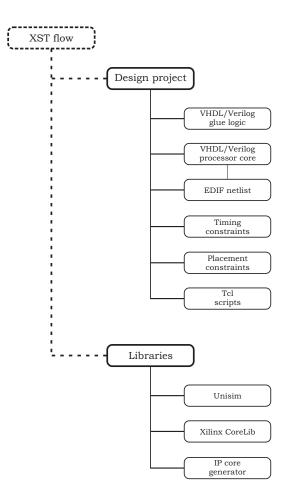

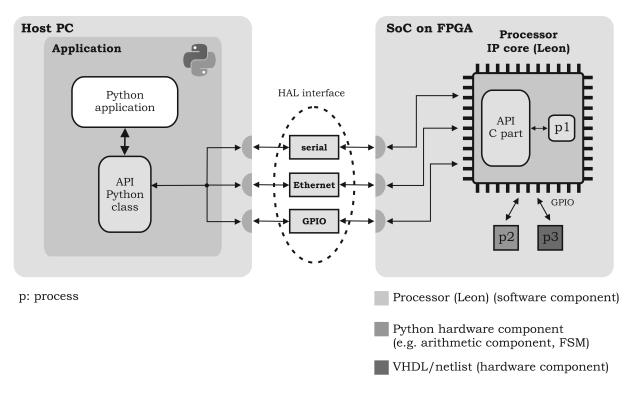

Στο Σχήμα Σ1.1 παρουσιάζουμε τον τρόπο με τον οποίο χρησιμοποιούμε την Python για να συνδέσουμε έτοιμους πυρήνες επεξεργαστών με άλλες μονάδες. Με χρήση μεθόδων στην Python παράγεται αυτόματα χώδικας VHDL που περιγράφει τη λειτουργικότητα επεξεργαστών ειδικού σκοπού χαθώς και τις απαραίτητες μονάδες διασύνδεσης με τον προγραμματιζόμενο επεξεργαστή. Το SysPy επίσης παράγει αυτόματα τα απαραίτητα Tcl scripts τα οποία εισάγουν όλα τα απαραίτητα αρχεία περιγραφής υλικού (HDL: Hardware Description Language) του επεξεργαστή και εκτελούν σε γραμμή εντολών τις διαδικασίες λογικής σύνθεση και φυσικής σχεδίασης με χρήση των κατάλληλων εργαλείων FPGA. Τα παραγόμενα script είναι συμβατά με το εργαλείο ISE της Xilinx για σχεδίαση υλικού με χρήση μονάδων FPGA. Επίσης εκτελείται αυτόματα η μεταγλώττιση των προγραμμάτων C που απαιτούνται για τον προγραμματισμό του επεξεργαστή με τη χρήση κατάλληλων GCC [1] μεταγλωττιστών, που είναι συμβατοί με τις περισσότερες διαθέσιμες αρχιτεκτονικές επεξεργαστών.

Σχήμα Σ1.1: Δομή συστήματος SoC με προγραμματιζόμενο επεξεργαστή.

### 1.2.3 Σύγκριση με άλλα εργαλεία ψηφιακής σχεδίασης

Αν και υπάρχουν ήδη διαθέσιμα εργαλεία που υποστηρίζουν σχεδίαση ψηφιακών συστημάτων σε υψηλό επίπεδο, τα περισσότερα από αυτά δεν υποστηρίζουν τη συνύπαρξη σε ένα σχέδιο μονάδων υλικού και πυρήνων προγραμματιζόμενων επεξεργαστών. Μία σωστή μεθοδολογία σχεδίασης πρέπει αν υποστηρίζει τη χρήση εργαλείων ανάπτυξης λογισμικού καθώς επίσης και τη σωστή διασύνδεση επεξεργαστών ειδικού σκοπού με τον προγραμματιζόμενο επεξεργαστή, που αποτελεί τον κεντρικό ελεγκτή του συστήματος. Τα περισσότερα εργαλεία σχεδίασης για FPGA [94], [87] αδυνατούν να διαχειριστούν με ενιαίο τρόπο την σχεδίαση υλικού και λογισμικού που απαιτείται για την υλοποίηση ενός SoC. Επίσης οι εταιρίες FPGA υποστηρίζουν την ενσωμάτωση μόνο εμπορικών πυρήνων επεξεργαστών συμβατών μόνο με τις μονάδες FPGA που παράγουν.

Στη διεθνή βιβλιογραφία υπάρχουν επίσης αναφορές και σε άλλα μη εμπορικά εργαλεία που κάνουν χρήση της Python για τη σχεδίαση ψηφιακών συστημάτων. Το εργαλείο PyHDL [39] υποστηρίζει τη σχεδίαση ενός συστήματος με χρήση περιγραφών δομής, όπου δομές σε C++ χρησιμοποιούνται για να περιγράψουν τη λειτουργία ψηφιακών μονάδων. Το PHDL [63] επίσης υποστηρίζει περιγραφές δομής σε Python και παράγει κώδικα RTL για υλοποίηση ενός συστήματος σε FPGA. Μειονέκτημα αποτελεί η χρήση έτοιμων βιβλιοθηκών σχετικά απλών λογικών μονάδων π.χ. λογικές πύλες, πολυπλέκτες, καταχωρητές κ.α.

Το PyMTL [58] χρησιμοποιεί την Python για να περιγράψει ψηφιαχές λειτουργίες σε χαμηλό επίπεδο περιγραφών RTL αλλά και πιο υψηλό αφηρημένο επίπεδο. Αν και υποστηρίζει την μετατροπή των περιγραφών σε γλώσσα Verilog, το PyMTL εστιάζει περισσότερο στην προσομοίωση ψηφιαχών συστημάτων, όπου η χρήση μεταγλωττιστών C++ επιταχύνει κατά πολύ τον χρόνο προσομοίωσης μια περιγραφής υψηλού επιπέδου Python. Οι παραγόμενες περιγραφές υλικού σε Verilog δεν είναι συμβατές για υλοποίηση σε FPGA ή ASIC. Επίσης τα μοντέλα προσομοίωσης που χρησιμοποιούνται δεν μοντελοποιούν την καθυστέρηση διέλευσης μέσα από τις λογικές μονάδες που παρατηρείται στο υλικό, όπως υποστηρίζεται στα μοντέλα του SysPy.

Αλλα εργαλεία όπως το MyHDL [23] [71] και το PDSDL [97] υποστηρίζουν λογικές περιγραφές δομής και περιγραφές συμπεριφοράς σε Python και μετατροπή σε γλώσσα HDL. Το MyHDL επίσης υποστηρίζει την προσομοίωση ψηφιακών μονάδων και παρέχει αποτελέσματα σε μορφή κειμένου και όχι με χρήση αρχείων κυματομορφών VCD όπως κάνουμε στο SysPy. Επίσης στο MyHDL δεν υποστηρίζεται η σχεδίαση με χρήση έτοιμων μονάδων σε VHDL ή Verilog όπως υποστηρίζεται στο SysPy, και όλες οι λογικές λειτουργίες πρέπει να περιγραφούν με τη χρήση της Python.

Συνοψίζοντας τις δυνατότητες του εργαλείου που σχεδιάσαμε σε σύγκριση με τα προαναφερόμενα

|          | Υποστηριζόμενες δυνατότητες |                                        |                            |                                 |                              |                                     |          |

|----------|-----------------------------|----------------------------------------|----------------------------|---------------------------------|------------------------------|-------------------------------------|----------|

| Εργαλεία | Python<br>σε RTL            | Παραγωγή συνθέσιμου<br>χώδικα για FPGA | Δυνατότητα<br>προσομοίωσης | Συσχεδίαση<br>υλικού-λογισμικού | Χρήση πυρήνων<br>επεξεργαστή | Χρήση εργαλείων<br>λογιχής σύνθεσης | Αναφορές |

| PyHDL    | x                           | -                                      | -                          | -                               | -                            | -                                   | [39]     |

| PHDL     | x                           | x                                      | -                          | -                               | -                            | -                                   | [63]     |

| MyHDL    | x                           | -                                      | x                          | -                               | -                            | -                                   | [23]     |

| PyMTL    | x                           | x                                      | x                          | -                               | -                            | -                                   | [58]     |

| PDSDL    | x                           | -                                      | -                          | -                               | -                            | -                                   | [97]     |

| SysPy    | x                           | x                                      | x                          | x                               | x                            | x                                   | [61]     |

Πίνακας Π1.1: Σύγκριση χαρακτηριστικών των εργαλείων σχεδίασης.

εργαλεία, μόνο το SysPy υποστηρίζει:

- 1. τη σχεδίαση processor-centric SoC και διαχείριση των απαραίτητων εργαλείων ανάπτυξης λογισμικού.

- 2. χρήση παραμετροποιήσιμων μεθόδων Python για αυτόματη μετατροπή τους σε περιγραφές VHDL.

- 3. προσομοίωση υψηλού επιπέδου με χρήση μεθόδων και κλάσεων Python για την περιγραφή της λειτουργία μονάδων του υλικού.

- 4. ταυτόχρονη προσομοίωση περιγραφών υλικού υψηλού επιπέδου και λογισμικού σε γλώσσα C

- 5. καταχώρηση κυματομορφών προσομοίωσης σε αρχεία τύπου VCD.

- 6. αυτόματη παραγωγή και χρήση Tcl scripts για τη διαχείριση όλων των απαραίτητων εργαλείων για τη συσχεδίαση υλικού/λογισμικού σε μονάδες FPGA.

Στον Πίνακα Π1.1 παρουσιάζουμε μία σύγκριση των προαναφερόμενων εργαλείων. Όπως φαίνεται όλα τα εργαλεία μπορούν να παράγουν κώδικα RTL από περιγραφές Python, αλλά μόνο το SysPy και το PHDL υποστηρίζουν την παραγωγή κώδικα συμβατό με υλοποιήσεις FPGA. Επίσης ενώ το MyHDL έχει δυνατότητες προσομοιώσεις ενός συστήματος στο επίπεδο μιας περιγραφής Python, μόνο το SysPy υποστηρίζει την παρουσίαση των αποτελεσμάτων προσομοίωσης μοντέλων Python με χρήση αρχείων VCD, που αποτελούν και τον πιο διαδεδομένο τρόπο καταχώρησης αρχείων ψηφιακών κυματομορφών και είναι συμβατά με όλα τα εργαλεία ψηφιακής προσομοίωσης. Τέλος μόνο το SysPy υποστηρίζει τη συσχεδίαση και συνπροσομοίωση στοιχείων υλικού και λογισμικού σε υψηλό επίπεδο,

δίνοντας τη δυνατότητα παράλληλης μοντελοποίησης του λογισμικού ενός ενσωματωμένου επεξεργαστή μαζί με τις διασυνδεδεμένες μονάδες υλικού.

### 1.3 Μεθοδολογία σχεδίασης

Σε αυτό το κεφάλαιο περιγράφεται η μεθοδολογία σχεδίασης που ακολουθείται στο SysPy. Περιγράφονται επίσης οι δυνατότητες για την προσομοίωση συστημάτων SoC με πυρήνα επεξεργαστή. Αναφέρονται επιπλέον τα χαρακτηριστικά εκείνα που υποστηρίζουν την προσομοίωση μονάδων υλικού και λογισμικού και τον τρόπο με τον οποίο συνδυάζονται τα αποτελέσματα της προσομοίωσης σε κοινά μοντέλα περιγραφής. Παρουσιάζεται επίσης και η δυνατότητα παραγωγής αριθμητικών και ψηφιακών κυματομορφών, οι οποίες χρησιμοποιούνται για τον καθορισμό βασικών παραμέτρων ενός συστήματος.

### 1.3.1 Μεθοδολογίας σχεδίασης

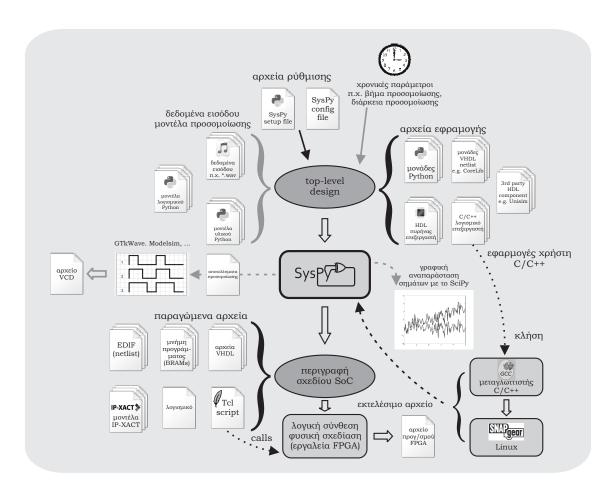

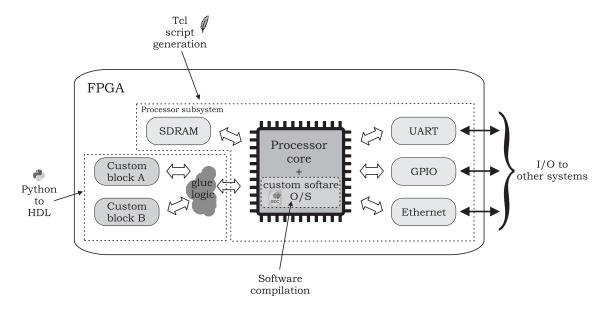

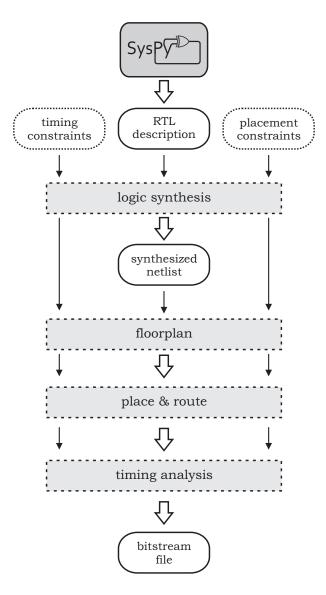

Η μεθοδολογία σχεδίασης παρουσιάζεται στο Σχήμα Σ1.2. Οι δυνατότητες της καλύπτουν έξι κύρια χαρακτηριστικά που θεωρούμε ότι είναι απαραίτητα για τη σχεδίαση ενός processor-centric SoC:

- 1. Περιγραφή σε HDL μονάδων υλικού, που συνδέονται σαν περιφερειακές μονάδες του πυρήνα επεξεργαστή.

- 2. Χρήση σε ένα σχέδιο έτοιμων μονάδων υλιχού από σχετιχές βιβλιοθήχες ή υλοποιημένες σε γλώσσα Verilog ή VHDL.

- 3. Προσομοίωση περιγραφών Python που προδιαγράφουν τη λειτουργικότητα μονάδων υλικού και λογισμικού που εκτελείται από τον επεξεργαστή.

- 4. Αυτόματη παραγωγή προγραμμάτων script για την κλήση εργαλείων ανάπτυξη λογισμικού, π.χ. κλήση μεταγλωττιστών C, αρχικοποίηση προγράμματος του επεξεργαστή σε μονάδες μνήμης (BRAM: Block RAM) στο FPGA.

- 5. Αυτόματη παραγωγή και εκτέλεση προγραμμάτων Tcl script για την οδήγηση των εργαλείων λογικής σύνθεσης και φυσικής σχεδίασης σε FPGA.

- 6. Παραγωγή μοντέλων ΧΜL, για την περιγραφή μονάδων υλικού, συμβατά με το πρότυπο IP-XACT [15].

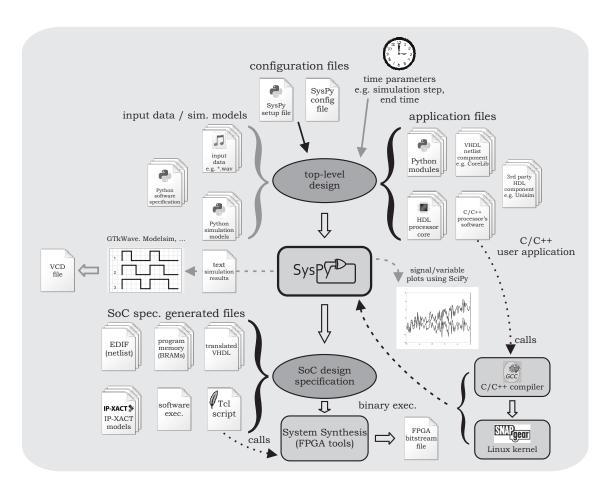

$\Sigma$ χήμα  $\Sigma 1.2$ : Μεθοδολογία σχεδίασης SoC με χρήση πυρήνων επεξεργαστών.

Σύμφωνα με την προτεινόμενη μεθοδολογία, η σχεδίαση ενός SoC ξεχινάει με τη δημιουργία μοντέλων περιγραφής του συστήματος. Τα μοντέλα περιγράφουν σε Python, με τη μορφή ψευδοχώδιχα. τη λειτουργία του λογισμιχού του επεξεργαστή, ενώ μπορεί να περιγράφουν χαι τη λειτουργία υλιχού, για τα οποία αχόμα δεν είναι αρχιχά διαθέσιμη η περιγραφή τους σε επίπεδο RTL. Το SysPy όμως υποστηρίζει χαι περιγραφές RTL σε επίπεδο Python, στις οποίες ο χρήστης μπορεί να μοντελοποιήσει χαι τις πιθανές χρονιχές χαθυστερήσεις που θα παρουσιάζουν μονάδες συνδυαστιχής λογιχής, π.χ. αριθμητιχές μονάδες, πολυπλέχτες χτλ. Όσες μονάδες του υλιχού περιγραφούν σε επίπεδο RTL, το εργαλείο μπορεί να μεταφράσει αυτόματα σε VHDL. Τα απαραίτητα σήματα χρονισμού επίσης μπορούν να μοντελοποιηθούν στο περιβάλλον προσομοίωσης του SysPy, π.χ. ένα σήμα ρολογιού 20MHz, δίνοντας την δυνατότητα να περιγραφούν συστήματα αχολουθιαχής λογιχής με σωλήνωση (pipelined datapath) όπου η ροή των δεδομένων ελέγχεται από το λογισμιχό του επεξεργαστή ή από μηχανές καταστάσεων στο υλιχό. Μία τέτοια περιγραφή ενός μοντέλου προσομοίωσης αντιχατοπτρίζει τη λειτουργία της πλειονότητας των ψηφιαχών συστημάτων. Στο Σχήμα Σ1.2 τα γχρίζα βέλη δείχνουν τα βήματα της διαδιχασίας προσομοίωσης, ενώ τα μαύρα βέλη δείχνουν τη διαδιχασία υλοποίησης του

συστήματος στη μονάδα FPGA.

Η δυνατότητα περιγραφής προσομοίωσης υψηλού επιπέδου, σε συνδυασμό με τη δυνατότητα προσομοίωσης συμβατή με τον χρονισμό ενός συστήματος σε επίπεδο περιγραφής RTL (cycle-accurate simulation) δίνει τη δυνατότητα στον χρήστη να πάρει αποφάσεις για κρίσιμες παραμέτρους ενός SoC, πριν ξεκινήσει τη διαδικασία υλοποίησης. Οι παραγόμενες κυματομορφές προσομοίωσης δίνουν τη δυνατότητα για την επίλυση προβλημάτων χρονισμού που μπορεί να παρουσιαστούν, ειδικά στη διασύνδεση του προγραμματιζόμενου επεξεργαστή με τις περιφερειακές του μονάδες και τους επεξεργαστές ειδικού σκοπού. Στις παραγράφους που ακολουθούν περιγράφονται αυτές οι δυνατότητες με μεγαλύτερη λεπτομέρεια.

Σχήμα Σ1.3: Εγκατάσταση και χρήση του SysPy σε περιβάλλον λειτουργικού συστήματος Linux.

Το SysPy αναπτύχθηκε και η λειτουργία του δοκιμάστηκε με χρήση του λειτουργικού συστήματος Debian Linux. Αρχεία εγκατάστασης (configuration files) χρησιμοποιούνται για να ορίσει ο χρήστης όλους τους απαραίτητους φακέλους που έχει γίνει η εγκατάσταση του εργαλείου και του απαραίτητου λογισμικού και των φακέλων όπου καταχωρούνται τα αρχεία σχεδίασης (working directory). Όλα τα εργαλεία που καλούνται μέσω του  $\operatorname{SysPy}$  καθώς και η δομή των φακέλων που δημιουργεί το εργαλείο κατά τη διαδικασία σχεδίασης, παρουσιάζονται στο  $\operatorname{\Sigmaχήμα} \operatorname{\Sigma}1.3$ .

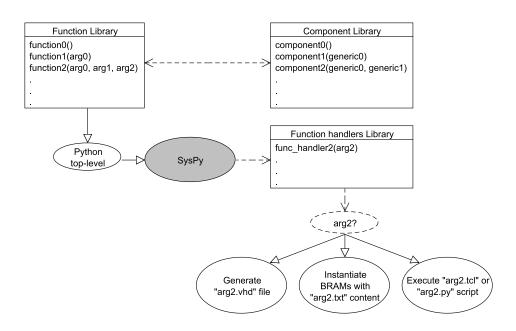

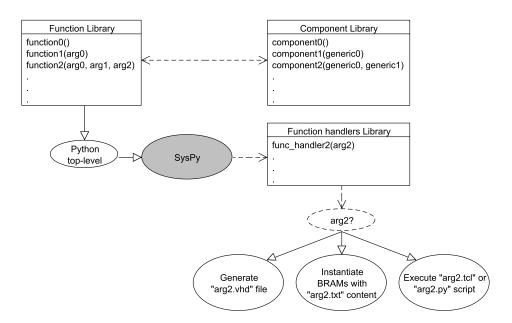

Σχήμα Σ1.4: Διάγραμμα UML για την απεικόνιση της χρήσης μεθόδων Python (function library και function handlers library) για την αυτόματη αρχικοποίηση μονάδων από τις βιβλιοθήκες του SysPy (component library).

Στο Σχήμα Σ1.4 απεικονίζεται μία αλληλουχία σε γλώσσα UML για την παρουσίαση της χρήσης των βιβλιοθηκών του SysPy και της αυτόματης παραμετροποίησης μονάδων υλικού με χρήση μεθόδων Python. Η χρήση της υψηλού επιπέδου παραμέτρου "arg2" στη συνάρτηση "function2" ενεργοποιεί την κλήση της αντίστοιχης μεθόδου "func\_handler2()", όπου η παράμετρος μπορεί να αντιπροσωπεύει την ονομασία ενός αρχείου ASCII (VHDL, text, Tcl script) το οποίο επεξεργάζεται ή καλείται αυτόματα για να αρχικοποιήσει τη σχετική μονάδα υλικού. Η χρήση των μεθόδων στην αρχικοποίηση μονάδων υλικού σε περιγραφές δομής καθιστά πιο σύντομες και συμπαγής αυτού του είδους τις περιγραφές σε γλώσσα Python. Η βιβλιοθήκη "function\_library" περιέχει δηλώσεις συναρτήσεων οι οποίες αρχικοποιούν αυτόματα τις μονάδες που περιέχονται στη βιβλιοθήκη "component\_library".

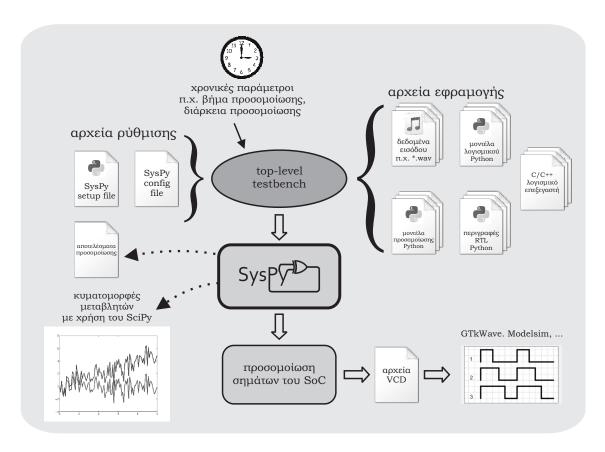

### 1.3.2 Δυνατότητες προσομοίωσης ενός SoC

Το SysPy μπορεί να χρησιμοποιηθεί για να προσομοιώσει ψηφιαχές μονάδες μέσω περιγραφών RTL σε γλώσσα Python. Το πιο ενδιαφέρον χαραχτηριστιχό όμως είναι η δυνατότητα προσομοίωσης αλγοριθμιχών περιγραφών συμπεριφοράς υλιχού και λογισμιχού, ειδιχότερα για μονάδες ενός SoC για τις οποίες πρέπει να καθοριστεί αν είναι απαραίτητη η υλοποίηση τους είτε στο υλιχό είτε με λογισμιχό που εχτελείται από τον επεξεργαστή του συστήματος. Τα χύρια χαραχτηριστιχά του μηχανισμού προσομοίωσης συνοψίζονται στα αχόλουθα σημεία:

- προσομοίωση περιγραφών Python, μονάδων υλικού σε επίπεδο RTL.

- προσομοίωση μονάδων υλιχού και λογισμιχού, π.χ. αριθμητιχές μονάδες, μονάδες ελεγκτών επιχοινωνίας κ.α., για τις οποίες δεν έχει υπάρχει πλήρης περιγραφή της λειτουργιχότητας στα αρχιχά στάδιο σχεδίασης.

- ανάπτυξη λογισμικού για τον επεξεργαστή ενός συστήματος σε γλώσσα C και προσομοίωση

του σε επίπεδο συστήματος μαζί με άλλες περιγραφές Python υλικού/λογισμικού.

- καταχώρηση των αποτελεσμάτων της προσομοίωσης σε αρχεία ψηφιακών κυματομορφών τύπου VCD και χρήση τους με δημοφιλή προγράμματα προσομοίωσης, όπως το ModelSim και το GTkWave.

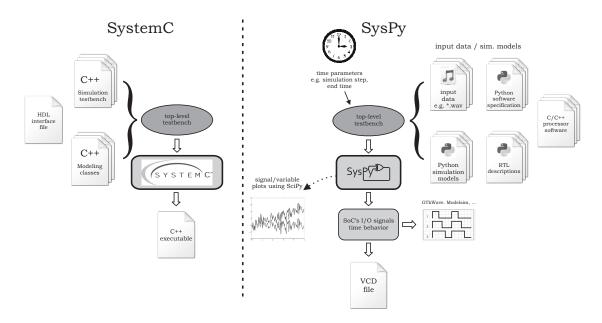

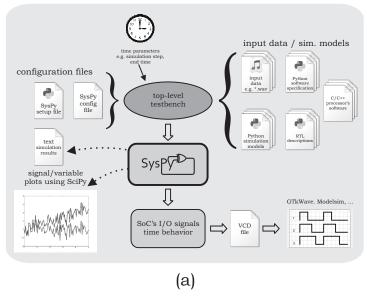

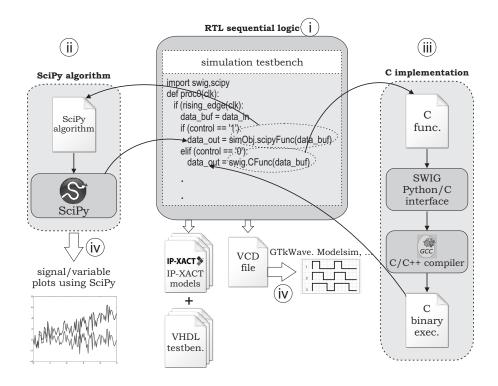

Σχήμα  $\Sigma 1.5$ : Λειτουργικότητα του μηχανισμού προσομοίωσης.

Ειδικά για την μοντελοποίηση σύνθετων αριθμητικών μονάδων, γίνεται χρήση της αριθμητικής βιβλιοθήκης SciPy στην Python. Αριθμητικοί αλγόριθμοι μπορούν να προσομοιωθούν κάνοντας χρήση έτοιμων μεθόδων, τα αποτελέσματα των οποίων μπορούν να επεξεργαστούν περαιτέρω από άλλες μονάδες υλικού, μέσω της διασύνδεσης που είναι εφικτή στο SysPy, μεταξύ μοντέλων υλικού RTL και μοντέλων συμπεριφοράς υψηλού επιπέδου. Με τη χρήση επίσης του SciPy είναι δυνατή η παραγωγή αριθμητικών κυματομορφών κατά την προσομοίωση ενός αλγορίθμου σε υψηλό επίπεδο, π.χ. επεξεργασία δεδομένων από ψηφιακά φίλτρα. Οι κυματομορφές αυτές μπορούν να χρησιμοποιηθούν για την ρύθμιση των παραμέτρων υλοποίησης ενός αλγορίθμου, ενώ αργότερα μετά την δημιουργία μοντέλων σε επίπεδο RTL, οι ψηφιακές κυματομορφές των σημάτων μιας μονάδας πιστοποιούν την σωστή λειτουργία του αλγορίθμου στο υλικό και την αριθμητική ακρίβεια των υπολογισμών. Στο Σχήμα Σ1.5 παρουσιάζονται τα βήματα που υποστηρίζονται κατά τη διαδικασία προσομοίωσης ενός SoC.

### 1.3.2.1 $\Sigma$ υνπροσομοίωση υλικού/λογισμικού με περιγραφές υψηλού επιπέδου

Ένας από τους βασικούς λόγους της επιλογής της Python ήταν και η δυνατότητα της γλώσσας να καλεί μεθόδους υλοποιημένες σε άλλες γλώσσες λογισμικού, όπως η C/C++. Η κλήση μεθόδων C μέσα από μοντέλα προσομοίωσης σε Python μαζί με τη χρήση του SciPy, μας δίνει τη δυνατότητα ταυτόχρονης προσομοίωσης αλγορίθμων λογισμικού με μονάδες υλικού, όπου η ανάπτυξη και προσομοίωση του λογισμικού μπορεί να γίνει με χρήση: α) αλγοριθμικών περιγραφών υψηλού επιπέδου με περιγραφές (Matlab-like) στο SciPy και β) με περιγραφές σε γλώσσα C, οι οποίες μπορούν εύκολα μετά να χρησιμοποιηθούν για τον προγραμματισμό του επεξεργαστή ενός συστήματος. Σύμφωνα με τη μελέτη της υπάρχουσας βιβλιογραφίας αυτό αποτελεί ένα από τα πιο καινοτόμα χαρακτηριστικά του SysPy.

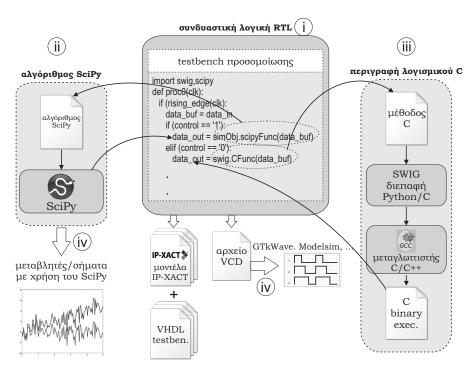

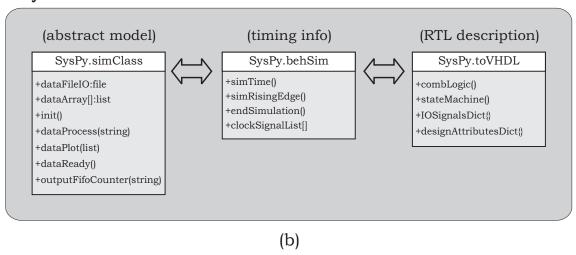

Σχήμα  $\Sigma 1.6$ : Μεθοδολογία προσομοίωσης με χρήση περιγραφών υλιχού RTL και αλγοριθμικών μοντέλων.

Στο Σχήμα Σ1.6 παρουσιάζομαι ένα τυπικό μοντέλο προσομοίωσης, όπου i) γίνεται χρήση της Python για την περιγραφή ενός διαύλου δεδομένων (pipelined datapath) ii) περιγραφές Python με τη χρήση του αριθμητικού πακέτου SciPy χρησιμοποιούνται για αλγοριθμικές περιγραφές μονάδων ενός συστήματος για τις οποίες δεν υπάρχει ακόμα υλοποίηση σε υλικό (HDL) ή λογισμικό (C/C++), iii) περιγραφές λογισμικού σε C χρησιμοποιούνται για την υλοποίηση αλγορίθμων των οποίων την εκτέλεση τους θα αναλάβει ο επεξεργαστής του συστήματος, ενώ iv) κατά τη διάρκεια της προσο-

μοίωσης παράγονται χυματομορφές των ψηφιαχών σημάτων του συστήματος μέσω του SciPy αλλά χαι σε μορφή αρχείων τύπου VCD, συμβατή με άλλα εργαλεία προσομοίωσης. Μέσω της χρήσης του μηχανισμού προσομοίωσης του SysPy, οι προγραμματιστές λογισμιχού μπορούν α) να αναπτύξουν αλγοριθμιχά μοντέλα με τη χρήση του SciPy και να ελέγξουν τη σωστή λειτουργιχότητα τους μέσω της συνπροσομοίωσης με τις μονάδες του υλιχού. β) Μπορούν επίσης να μετατρέψουν τις περιγραφές λογισμιχού από Python σε C και εχ νέου να ελέγξουν τη λειτουργιχότητα τους μέσω του SysPy, διευχολύνοντας έτσι και επιταχύνοντας τη διαδιχασία ανάπτυξης του λογισμιχού σε υψηλό επίπεδο.

### 1.3.3 Παράδειγμα προσομοίωσης

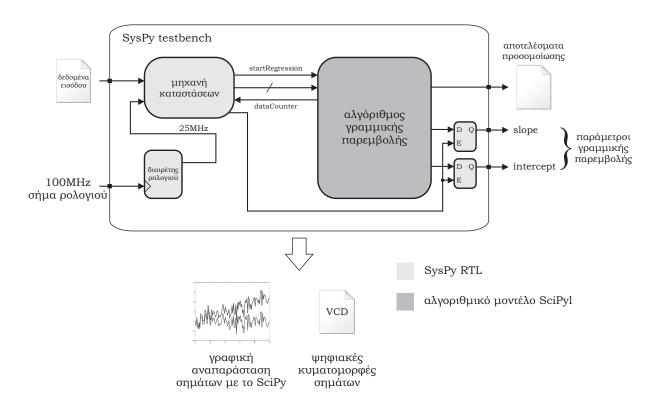

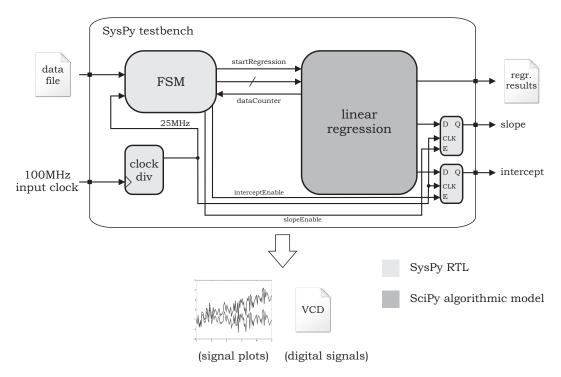

Για την καλύτερη κατανόηση των δυνατοτήτων προσομοίωσης που παρέχει το SysPy παρουσιάζουμε ένα παράδειγμα προσομοίωσης ενός αριθμητικού μοντέλου για τον υπολογισμό του αλγορίθμου εύρεσης πολυωνύμου γραμμικής παρεμβολής. Ο αλγόριθμος εφαρμόζεται πάνω σε δεδομένα εισόδου που παρέχονται σε μορφή αρχείων ASCII και υπολογίζει τις παραμέτρους μιας γραμμικής εξίσωσης που εκφράζει τα εισερχόμενα δεδομένα. Προδιαγράφοντας τη σύνθεση του συστήματος, χωρίσαμε τις λειτουργίες του στις ακόλουθες τρεις μονάδες: α) την μονάδα που εκτελεί τους αριθμητικούς υπολογισμούς του αλγορίθμου, β) μονάδες μνήμης για την καταχώρηση των αρχικών δεδομένων και των αποτελεσμάτων του αλγορίθμου και γ) μονάδες για την λήψη και την μετάδοση δεδομένων από και προς την αριθμητική μονάδα. Όλες οι αριθμητικές λειτουργίες υλοποιούνται σε μονάδες υλικού με στόχο την γρήγορη εκτέλεση του αλγορίθμου. Μία μηχανή καταστάσεων στο υλικό αναλαμβάνει τη διαχείριση διακίνησης των δεδομένων μέσα στο σύστημα, κάτω από τον έλεγχο του λογισμικού, το οποίο επίσης αναλαμβάνει την καταχώρηση των αρχικών δεδομένων και των αποτελεσμάτων επεξεργασίας σε μορφή αργείων. Η δομή του συστήματος παρουσιάζεται στο Σχήμα Σ1.7.

Σχήμα Σ1.7: Σχηματικό διάγραμμα του μοντέλου προσομοίωσης του αλγορίθμου γραμμικής παρεμβολής.

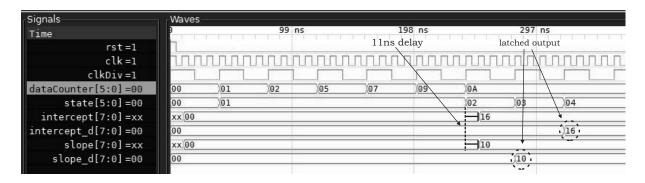

Για λόγους οικονομίας χώρου και έκτασης του κειμένου, παραθέτουμε αναφορές σε παραδείγματα κώδικα, όπως αυτά παρουσιάζονται στο Αγγλικό κείμενο. Στο Code Example 3.1 δηλώνονται όλα τα σήματα εισόδου/εξόδου του συστήματος. Στις γραμμές 4-9 παράγεται η κυματομορφή του βασικού συστήματος ρολογιού (100MHz, 50% duty cycle, διάρκεια προσομοίωσης 15us), ενώ στις γραμμές 19-21 ανατίθενται οι τιμές των σημάτων εισόδου κατά τη διάρκεια της προσομοίωσης, π.χ. στη γραμμή 19 ορίζεται ότι το σήμα rst ενεργοποιείται για 5ns στην αρχή της προσομοίωσης. Για τη μηχανή καταστάσεων γίνεται χρήση περιγραφών RTL σε Python, όπως παρουσιάζεται στα Code Examples 3.2 και 3.3. Οι απαραίτητες βιβλιοθήκες και η κλάση του μοντέλου προσομοίωσης καλούνται στις γραμμές 1-4. Η συνάρτηση στη γραμμή 6 περιγράφει συνδυαστική λογική με τη χρήση των σημάτων ασύγχρονου reset και ρολογιού που χρησιμοποιούνται για την οδήγηση όλων των μονάδων του συστήματος. Το αρχείο που περιέχει τα δεδομένα εισόδου δηλώνεται στη γραμμή 19 και στη γραμμή 20 δηλώνεται η μορφή αναπαράστασης των αριθμών τύπου fixed-point (5 ακέραια ψηφία και 3 ψηφία στο δεκαδικό μέρος που θα χρησιμοποιηθούν στους υπολογισμούς. Η λειτουργία της μηχανής καταστάσεων βασίζεται στις ανερχόμενες ακμές του σήματος ρολογιού (γραμμή 26). Εφόσον γίνει η ανάγνωση των δεδομένων εισόδου (κατάσταση 1, γραμμή 38), εκτελείται η κατάσταση 2 όπου ενεργοποιείται η εκτέλεση του αλγορίθμου στην αντίστοιχη μονάδα, ενώ στην κατάσταση 3 (γραμμή

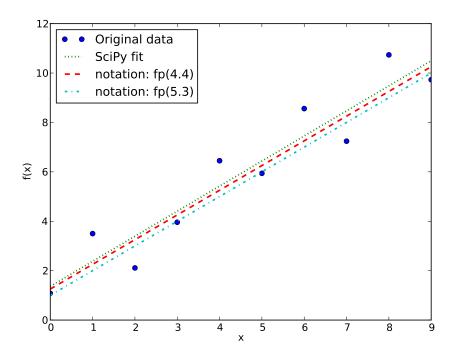

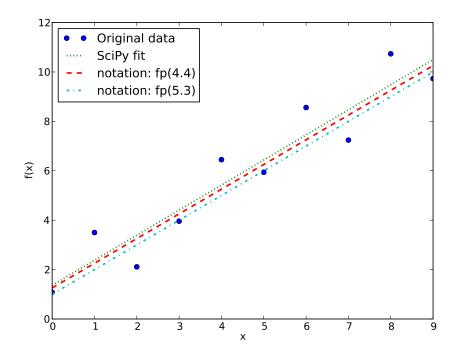

13) τα αποτελέσματα του αλγορίθμου (παράμετροι 'α': slope και 'β': intercept) παρουσιάζονται στις αντίστοιχες εξόδου του συστήματος. Στην κατάσταση 4 ενεργοποιείται στο SciPy η απεικόνιση των δεδομένων εισόδου και ο τρόπος με τον οποίο η γραμμική εξίσωση που υπολογίστηκε, όπως παρουσιάζεται στο Σχήμα  $\Sigma 1.8$ , χρησιμοποιώντας διαφορετικές μορφές αναπαράστασης για τους δεκαδικούς αριθμούς fixed-point.  $\Omega$ ς "original data" χαρακτηρίζονται τα δεδομένα εισόδου από το μουσικό αρχείο.

Σχήμα  $\Sigma 1.8$ : Γραμμική παρεμβολή δεδομένων εισόδου, με χρήση διαφορετικών αναπαραστάσεων fixed-point.

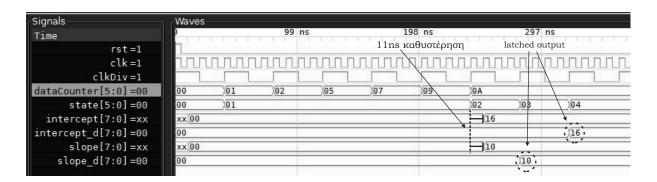

Κατά τη διάρχεια της προσομοίωσης, οι χυματομορφές των σημάτων εισόδου/εξόδου του συστήματος καταχωρήθηκαν στο παραγόμενο αρχείο VCD και το πρόγραμμα GTKWave [38] χρησιμοποιήθηκε για την αναπαράσταση των χυματομορφών. Στις χυματομορφές παρουσιάζεται η συμπεριφορά των ψηφιαχών σημάτων σε σχέση με το σήμα ρολογιού και επίσης λαμβάνονται υπόψιν οι λογιχές καθυστερήσεις που παρουσιάζονται στα σήματα εξόδου, σύμφωνα με τον τρόπο που αυτές μοντελοποιούνται στο Code Example 3.1 (γραμμή 16, παράμετρος "del", ορισμός 11ns λογιχή καθυστέρηση για τα σήματα εξόδου "slope" και "intercept"). Στο Σχήμα Σ1.9 παρουσιάζεται το σήμα ρολογιού 100MHz (clk), το οποίο διαιρείται μέσω της κατάλληλης λογιχής στα 25MHz (clkDiv). Το σύστημα επεξεργάζεται δύο τιμές δεδομένων εισόδου και παράγει τις παραμέτρους slope και intercept της

Σχήμα Σ1.9: Ψηφιακές κυματομορφές σημάτων εισόδου/εξόδου του συστήματος εφαρμογής του αλγορίθμου γραμμικής παρεμβολής.

γραμμικής εξίσωσης που παρεμβάλει τα δεδομένα.

Με εύχολο τρόπο μπορεί ο χρήστης να τροποποιήσει τις συχνότητες των σημάτων ρολογιού, τις τιμές των σημάτων εισόδου και τον χρόνο των λογικών καθυστερήσεων, με στόχο τη διερεύνηση της σωστής λειτουργίας ενός ψηφιακού συστήματος. Με τον τρόπο που προσεγγίζουμε τη σχεδίαση και προσομοίωση ενός ψηφιακού SoC, κάθε λογική μονάδα αντιμετωπίζεται ως ένα μαύρο κουτί στο οποίο ο χρήστης αλλάζοντας τις τιμές των σημάτων εισόδου και τις χρονικές παραμέτρους μπορεί να διερευνήσει τη σωστή λειτουργικότητα ενός συστήματος σε αλγοριθμικό επίπεδο συμπεριφοράς αλλά και σε λογικό επίπεδο RTL της ψηφιακής υλοποίησης. Μέσω του SysPy επίσης είναι δυνατή η χρήση των αλγοριθμικών μοντέλων που αναπτύσσει ο χρήστης με τη χρήση της βιβλιοθήκης SciPy και η μετατροπή τους σε συναρτήσεις σε γλώσσα C, η λειτουργικότητα των οποίων μπορεί να προσομοιωθεί στο επίπεδο των περιγραφών Python. Η δυνατότητα αυτή κρίνεται ιδιαίτερα χρήσιμη εφόσον τα υψηλού επιπέδου μοντέλα του λογισμικού μπορούν εύκολα να μετατραπούν από Python σε γλώσσα C και να χρησιμοποιηθούν για την προσομοίωση του λογισμικού και τον προγραμματισμό του επεξεργαστικού πυρήνα ενός συστήματος.

### 1.4 Παραδείγματα σχεδίασης SoCs

Το SysPy χρησιμοποιήθηκε για τη σχεδίαση τριών σύνθετων σχεδίων SoC με προγραμματιζόμενο επεξεργαστή. Τα παραδείγματα σχεδίασης υλοποιούν SoC: α) επεξεργασίας εικόνων, β) επεξεργασίας βιολογικών δεδομένων και γ) επεξεργασίας ήχου. Μέσω της υλοποίησης των τριών αυτών σχεδίων προσπαθήσαμε να βελτιώσουμε τα χαρακτηριστικά του SysPy και ειδικότερα τις μεθοδολογίες ανάπτυξης και περιγραφής σε υψηλό επίπεδο, χρησιμοποιώντας την Python για την περιγραφή της

λειτουργικότητας ενός ψηφιακού συστήματος. Επίσης κατά τη διαδικασία ανάπτυξης κάθε σχεδίου κάναμε χρήση των δυνατοτήτων του SysPy που ήταν κάθε φορά διαθέσιμες, εφόσον η εξέλιξη του εργαλείου ήταν μια παράλληλη διαδικασία με την ανάπτυξη των τριών συστημάτων που χρησιμοποιήθηκαν ως παραδειγμάτων σχεδίασης. Στόχος επίσης ήταν να εκτιμήσουμε την αξία των εργαλείων που παρέχονται μέσω του SysPy, κυρίως ως προς την μείωση του χρόνου σχεδίασης και τη δυνατότητα χρήσης περιγραφών υψηλού επιπέδου για την υλοποίηση ψηφιακών συστημάτων με πυρήνες προγραμματιζόμενων επεξεργαστών σε μονάδες FPGA.

### 1.4.1 SoC επεξεργασίας εικόνων

Το πρώτο παράδειγμα που υλοποιήσαμε για να εξακριβώσουμε την ορθή λειτουργία του SysPy και να εκτιμήσουμε τις δυνατότητες του εργαλείου ήταν ένα σύστημα επεξεργασίας εικόνων [60], βασισμένο στον μικροελεγκτή 8-bit AVR ATmega128 [45]. Συγκεκριμένα χρησιμοποιήσαμε τον πυρήνα του επεξεργαστή σε περιγραφή VHDL, διαθέσιμο από την ιστοσελίδα του OpenCores [76]. Για τη σχεδίαση του συστήματος κάναμε χρήση της μεθοδολογίας που υποστηρίζετε στο SysPy, ξεκινώντας από την περιγραφή του συστήματος με χρήση της Python, μέχρι τη χρήση αρχείων Τcl για την παραγωγή του αρχείου προγραμματισμού του FPGA. Το SysPy χρησιμοποιήθηκε για να παράγει όλα τα απαιτούμενα, συμβατά με τα εργαλεία λογικής σύνθεσης για FPGA, αρχεία VHDL. Τα αρχεία περιγράφουν το σύστημα καθώς και τη διασύνδεση του επεξεργαστή ειδικού σκοπού που χρησιμοποιήθηκε με τον επεξεργαστή ΑVR, ενώ το SysPy διαχειρίστηκε επίσης την μεταγλώττιση του απαραίτητου λογισμικού του επεξεργαστή και την αρχικοποίηση της διαθέσιμης μνήμης προγράμματος.

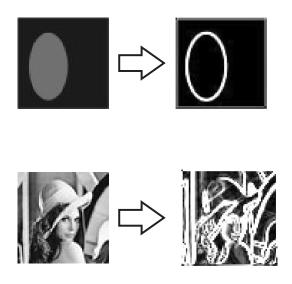

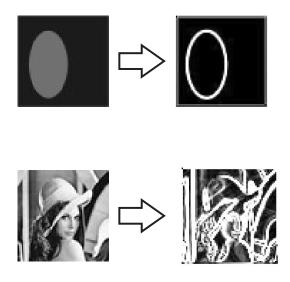

Το σύστημα που υλοποιήσαμε εφαρμόζει τον αλγόριθμο Sobel [37] για την ανεύρεση ακμών σε μία ασπρόμαυρη εικόνα. Ο αλγόριθμος παράγει για κάθε ασπρόμαυρη εικόνα δύο νέες εικόνας όπου ανιχνεύει ακμές σε οριζόντια και κάθετη κατεύθυνση. Υπολογίζοντας την Ευκλείδεια απόσταση μεταξύ των αντίστοιχων εικονοστοιχείων (pixel) σε κάθε μία από τις δύο νέες εικόνας παράγεται μία τρίτη εικόνα που αποτελεί και την τελική επεξεργασμένη εικόνα όπου εντοπίζονται όλες οι ακμές της αρχικής. Η ανίχνευση ακμών πολλές φορές αποτελεί το αρχικό στάδιο επεξεργασίας μίας εικόνας σε άλλους αλγορίθμους που χρησιμοποιούνται για την ανίχνευση αντικειμένων ή προσώπων και επίσης για συμπίεση εικόνων.

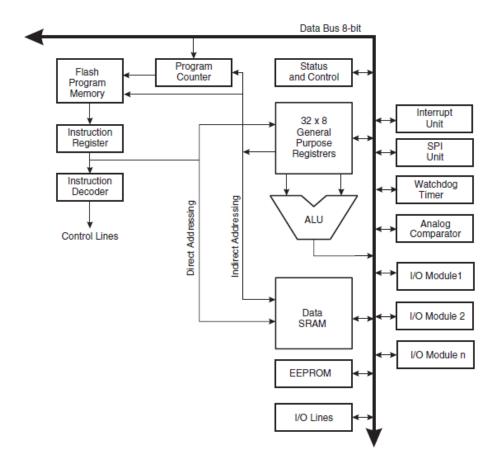

Η επιλογή του ATmega128, ως πρώτου πυρήνα επεξεργαστή που ενσωματώθηκε στο SysPy έγινε επειδή ο εν λόγω πυρήνας είναι σχετικά απλός και διέθετε αρκετή μνήμη προγράμματος (128kb) και πόρτες εισόδου/εξόδου γενικού σκοπού που χρησιμοποιήσαμε για τη διασύνδεση του μέσα στο FPGA. Ο επεξεργαστής ενσωματώνει μονάδα σειριακής επικοινωνίας Universal Asynchronous Re-

ceiver Transmitter (UART), μέσω της οποίας συνδέεται με ένα H/Y, ο οποίος αποστέλλει τις προς επεξεργασία εικόνας στο FPGA της οικογένειας VIrtex-5 της Xilinx το οποίο χρησιμοποιήσαμε. Επίσης η αρχιτεκτονική AVR είναι μία από τις γρηγορότερες αρχιτεκτονικές 8-bit, όπου οι περισσότερες εντολές του επεξεργαστή απαιτούν ένα κύκλο ρολογιού για την εκτέλεση τους.

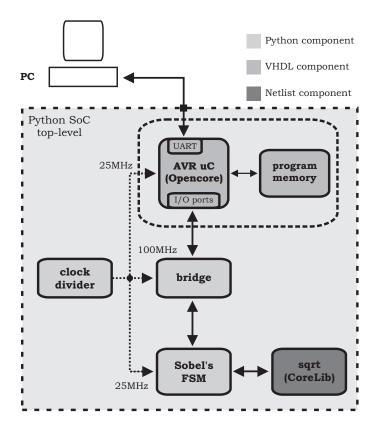

Σχήμα Σ1.10: Διάγραμμα του SoC επεξεργασίας εικόνας.

Στο Σχήμα Σ1.10 δείχνουμε τις μονάδες που διασυνδέονται για την υλοποίηση του συστήματος επεξεργασίας εικόνας. Στο σύστημα περιλαμβάνονται ο επεξεργαστής ΑVR και ο επεξεργαστής ειδικού σκοπού που αποτελείται από μία μηχανή καταστάσεων που υλοποιεί τα βήματα επεξεργασίας του αλγορίθμου και μία αριθμητική μονάδα που εκτελεί τον υπολογισμό της τετραγωνική ρίζας για την εύρεση της Ευκλείδειας απόστασης. Ο αλγόριθμος του Sobel εφαρμόζει δύο φίλτρα σε μορφή πινάκων μεγέθους 3x3 για την ανίχνευση των οριζόντιων και κάθετων ακμών μιας εικόνας. Για τον υπολογισμό των εικονοστοιχείων της τελικής επεξεργασμένης εικόνας, γίνεται χρήση του αλγορίθμου COordinate Rotation Digital Computer (CORDIC) [91], [92], για τον υπολογισμό της τετραγωνικής ρίζας και την εύρεση της Ευκλείδειας απόστασης μεταξύ των αντίστοιχων εικονοστοιχείων των εικόνων που δημιουργήθηκαν με τη χρήση των δύο εφαρμοζόμενων φίλτρων. Η τελική εικόνα αποστέλλεται στον Η/Υ μέσω της σειριακής σύνδεσης.

Η υλοποίηση του αλγορίθμου CORDIC γίνεται με τη χρήση έτοιμης μονάδας από την βιβλιοθήκη CoreLib της Xilinx [48]. Όπως φαίνεται και στο Σχήμα Σ1.10 η μονάδα του αλγορίθμου CORDIC

μαζί με τη μηχανή καταστάσεων που εκτελεί τον αλγόριθμο του Sobel επικοινωνούν με τον επεξεργαστή AVR μέσω μίας γέφυρας δεδομένων. Η μονάδα CORDIC χρησιμοποιείται σε μορφή αρχείου netlist από τη βιβλιοθήκη της Xilinx και αρχικοποιείται μέσω της ενσωμάτωσης της μονάδας στις σχετικές βιβλιοθήκες του SysPy.

Στα Code Examples 6.1, 6.2 και 6.3 παρουσιάζεται η περιγραφή σε Python του συστήματος επεξεργασίας εικόνας. Ο επεξεργαστής AVR συνδέεται με τις υπόλοιπες μονάδες κάνοντας χρήση τριών εισόδων/εξόδων γενικού σκοπού (GPIO: General Purpose Input Output), χρησιμοποιώντας την PORTE σαν δίαυλο ελέγχου και τις PORTA και PORTB σαν διαύλους δεδομένων. Για την υλοποίηση του συστήματος κάναμε χρήση της πλακέτας FPGA ML509 [25], της Digilent, η οποία διαθέτει την μεσαία μεγέθους μονάδα FPGA Virtex-5 XC5VLX110T-1. Μία μονάδα διαιρέτη ρολογιού χρησιμοποιείται για να παράγει το βασικό σήμα ρολογιού των 25MHz, από το σήμα των 100MHz που παρέχει η γεννήτρια ρολογιού στην πλακέτα. Το σήμα ρολογιού χρησιμοποιείται για τον χρονισμό του επεξεργαστή AVR και της μονάδας επεξεργαστή ειδικού σκοπού του αλγορίθμου Sobel.

Στην περιγραφή Python αναφέρονται επίσης τα αρχεία C που χρησιμοποιούνται για τον προγραμματισμό του επεξεργαστή. Με χρήση του εργαλείου avr-gcc, που καλείται αυτόματα από το SysPy, γίνεται η μεταγλώττιση του προγράμματος και το SysPy αντιγράφει τον δεκαεξαδικό (hex code) του προγράμματος στις σχετικές μνήμης BRAM που υλοποιούν τη μνήμη προγράμματος του πυρήνα AVR. Όλα τα αρχεία Python που περιγράφουν το σύστημα, καθώς και τα παραγόμενα VHDL αρχεία, υπάρχουν στην ιστοσελίδα [88] που υπάρχει για την περιγραφή των δυνατοτήτων και χαρακτηριστικών του SysPy.

Σχήμα  $\Sigma 1.11$ : Επεξεργασμένες εικόνες μεγέθους 64x64 εικονοστοιχείων.

Κατά τη χρονική περίοδο σχεδίασης του SoC δεν ήταν ακόμα διαθέσιμα οι δυνατότητες προσομοίωσης υψηλού επιπέδου που παρέχει το SysPy και συνεπώς η προσομοίωση των λειτουργιών του SoC, πριν την υλοποίηση του στο FPGA, έγινε μόνο με χρήση των προσομοιωτών Modelsim [66] και Xilinx ISE (ISim) [50]. Ο έλεγχος της σωστής λειτουργίας έγινε και στο επίπεδο υλοποίησης του συστήματος στη πλακέτα του FPGA, με χρήση εικόνων μεγέθους 64x64 εικονοστοιχείων. Η αποστολή των εικόνων και η λήψη των επεξεργασμένων αποτελεσμάτων έγινε με χρήση προγράμματος διεπαφής που αναπτύχθηκε με τη γλώσσα Matlab και εκτελείται στον H/Y που συνδέεται με την πλακέτα FPGA. Στο Σχήμα Σ1.11 παρουσιάζονται τα αποτελέσματα επεξεργασίας εικόνων μεγέθους 64x64 εικονοστοιχείων, όπου έχει γίνει ανίχνευση των ακμών με χρήση του SoC.

Τα αποτελέσματα δέσμευσης των πόρων του FPGA από το σύστημα επεξεργασίας εικόνων παρουσιάζονται στον Πίνακα Π1.2. ΓΙα την εκτέλεση του αλγορίθμου CORDIC καταλαμβάνονται οχτώ DSP48 μονάδες, η οποία περιλαμβάνει υλοποιήσεις πολλαπλασιαστών. Μονάδες μνήμης BRAM καταλαμβάνονται για την υλοποίηση των μνημών προγράμματος και δεδομένων του επεξεργαστή. Συνολικά για την υλοποίηση όλου του συστήματος χρησιμοποιήθηκαν 367 μονάδες προγραμματιζόμενη λογικής (CLB: Configurable Logic Block). Κάθε CLB περιέχει οχτώ μονάδες Look Up Table (LUT) των έξι εισόδων, ενώ η μονάδες BRAM έχουν μέγεθος 36kbit. Σύμφωνα με τις αναφορές σχεδίασης μετά τη φυσική σχεδίαση του συστήματος (Placement and Routing), το σύστημα μπορεί να

χρονιστεί σε συχνότητα 190MHz. Σύμφωνα επίσης με μετρήσεις στο FPGA με τη βοήθεια της μονάδα logic analyzer ChipScope Pro [52] της Xilinx, το σύστημα μπορεί να επεξεργαστεί 10 εικόνες/sec. μεγέθους 64x64 εικονοστοιχείων, όπου ο χρόνος επεξεργασίας μετρήθηκε από τη στιγμή που ξεκινάει η αποστολή της εικόνας από τον Η/Υ μέχρι να καταχωρηθεί επίσης στον Η/Υ η τελική επεξεργασμένη εικόνα.

| Components               | CLBs | BRAMs | DSP48 |

|--------------------------|------|-------|-------|

| Sobel accelerator + sqrt | 47   | 0     | 8     |

| AVR Processor soft core  | 267  | 48    | 0     |

| Bridge                   | 3    | 0     | 0     |

| Clock divider            | 5    | 0     | 0     |

Πίνακας Π1.2: Αποτελέσματα δέσμευσης λογικών πόρων στη μονάδα FPGA Virtex-5 LX110T (CLB: δύο slices, Slice: τέσσερα 6- εισόδων LUTs, BRAM: 36Kb, DSP48: 25x18-bit).

Μέσω της σχεδίασης του συστήματος επεξεργασίας σήματος δοχιμάσαμε τις βασιχές λειτουργίες σχεδίασης του SysPy. Πιο συγχεχριμένα ελέγξαμε την ορθή λειτουργία των μηχανισμών: α) μετατροπής περιγραφών Python σε VHDL σε επίπεδο περιγραφής RTL, β) χρήση πυρήνων επεξεργαστών και διασύνδεση τους με λογιχές μονάδες ειδιχού σχοπού, γ) χρήση ψηφιαχών μονάδων πολλαπλών μορφών (Python, VHDL, netlist) και δ) χρήση μέσω του SysPy εργαλείων ανάπτυξης λογισμιχού. Μετά την επιτυχή σχεδίαση του συστήματος επεξεργασίας ειχόνας, όσον αφορά την ανάπτυξη του SysPy, προχωρήσαμε στη ενσωμάτωση στο εργαλείο της δυνατότητας χρήσης επεξεργαστών 32-bit, με απώτερο στόχο τη σχεδίαση πολυπλοχότερων συστημάτων. Προδιαγράψαμε επίσης τις δυνατότητες προσομοίωσης που θέλαμε να υποστηρίζει το SysPy και τον τρόπο υλοποίησης τους με χρήση της Python.

## 1.4.2 SoC προσομοίωσης βιολογικών δικτύων

Η πρώτη προσθήκη στο SysPy, μετά την ανάπτυξη του SoC επεξεργασίας εικόνας, ήταν η χρήση του πυρήνα επεξεργαστή 32-bit Leon3 και των εργαλείων ανάπτυξης λογισμικού που υποστηρίζει. Με τη χρήση του Leon3 ήταν δυνατή η επίτευξη ταχύτερης μεταφοράς δεδομένων μεταξύ του επεξεργαστή και άλλων λογικών μονάδων στο FPGA. Επίσης μέσω κατάλληλων προγραμμάτων οδήγησης (drivers) κατέστη εφικτή α) η διασύνδεση του επεξεργαστή με μονάδες μνήμης τύπου SDRAM διαθέσιμες στην πλακέτα που χρησιμοποιήσαμε και β) η επικοινωνίας του επεξεργαστή με τον Η/Υ μέσω δικτύου Ethernet με χρήση του κατάλληλου ελεγκτή δικτύου στην πλακέτα του FPGA. Για την επίδειξη των

νέων δυνατοτήτων σχεδίασης υλοποιήθηκε ένα SoC που προσομοιώνει στο υλικό μοντέλα δικτύων βιοχημικών αντιδράσεων (biochemical reaction networks: BioModels [57], [17]). Η επιτάχυνση της προσομοίωσης τέτοιων μοντέλων στο υλικό είναι πολύ χρήσιμη στον τομέα της υπολογιστικής βιολογίας (computational biology), όπου έως τώρα η προσομοίωση μοντέλων γίνεται σχεδόν αποκλειστικά με τη χρήση λογισμικού.

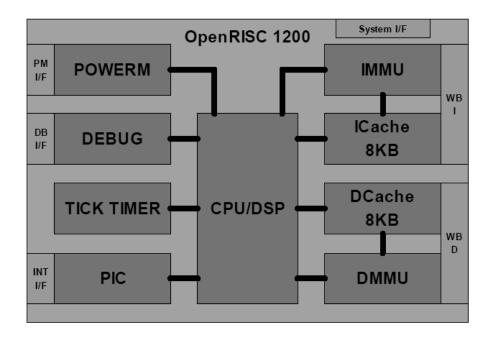

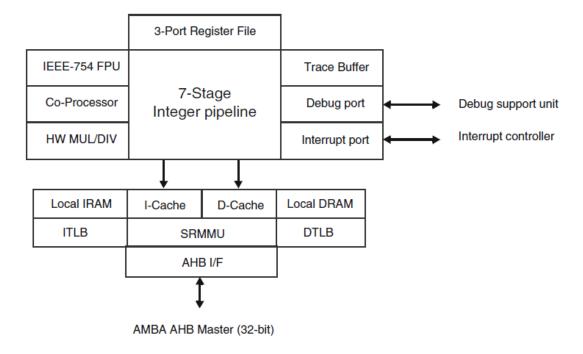

Ο Leon3 είναι ένας αρχετά δημοφιλής πυρήνας επεξεργαστή 32-bit και παρέχεται σε περιγραφή VHDL από την εταιρεία Aeroflex Gaisler. Ο επεξεργαστής υποστηρίζει την αρχιτεκτονική SPARC V8, η υλοποίηση του σε VHDL υποστηρίζει μεγάλο βαθμό παραμετροποίησης ενώ παρέχεται μαζί με εργαλεία προσομοίωσης και αποσφαλμάτωσης (debugger) λογισμικού. Ο επεξεργαστής αποτελεί πυρήνα της βιβλιοθήκης GRLIB IP [33], στην οποία συγκαταλέγεται πλήθος παραμετροποιήσιμων πυρήνων, που μπορούν να συνδεθούν στον Leon σαν περιφερειακές μονάδες, κάνοντας χρήση του πρωτοκόλλου επικοινωνίας Advanced Microcontroller Bus Architecture (AMBA) [13] που υποστηρίζει ο επεξεργαστής. Ο Leon3 έχει υλοποιηθεί σε αρκετές οικογένειες FPGA (μεταξύ αυτών σε FPGA των εταιρειών Altera και Xilinx) καθώς και σε ολοκληρωμένα κυκλώματα τύπου ASIC. Μία τυπική υλοποίηση του επεξεργαστή απαιτεί περίπου 25k-30k λογικές πύλες. Τα κύρια χαρακτηριστικά του επεξεργαστή αναφέρονται στη λίστα που ακολουθεί:

- Σωλήνωση διαύλου δεδομένων 7-σταδίων.

- Ενσωμάτωση μονάδων διαιρέτη και πολλαπλασιαστή, με χρήση αντίστοιχων εντολών.

- Υποστήριξη αρχιτεκτονικής Harvard.

- Χρονισμός λειτουργίας στα 125MHz και στα 400MHz σε υλοποίηση FPGA και ASIC 0.13μm αντίστοιγα.

- Συμβατότητα με το πρωτόκολλο ΑΜΒΑ-2.0 ΑΗΒ για τη σύνδεση περιφερειακών μονάδων.

- Διάθεση πλήθους εργαλείων για την ανάπτυξη λογισμικού στον επεξεργαστή: μεταγλωττιστές,

προσομοιωτές και εργαλεία για την αποσφαλμάτωση λογισμικού.

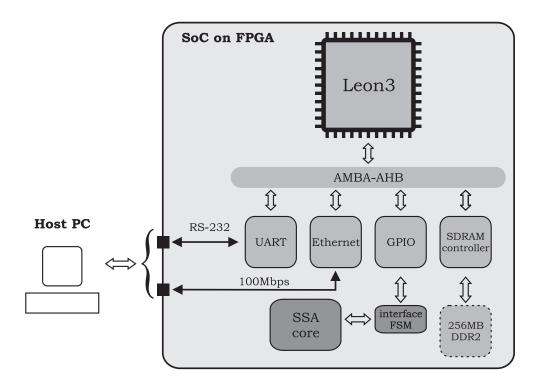

Το απαραίτητο λογισμικό για τον Leon αναπτύχθηκε σε γλώσσα C, με χρήση του μεταγλωττιστή sparc-elf-gcc. Για την υλοποίηση του Soc έγινε χρήση της αναπτυξιακής πλακέτας ML509 της Digilent. Για τη μνήμη προγράμματος και τη μνήμη δεδομένων έγινε χρήση της διαθέσιμης στην πλακέτα 256MB SDRAM DDR2 μνήμης. Επίσης χρησιμοποιήθηκε ο σχετικός ελεγκτής στην πλακέτα για τη σύνδεση του επεξεργαστή με H/Y μέσω δικτύου Ethernet με ταχύτητα μετάδοσης δεδομένων στα 100Mbps. Η υποστήριξη από τον επεξεργαστή Leon δικτύωσης Ethernet και πρόσβασης σε μεγάλου μεγέθους

μνήμες τύπου SDRAM, μας έδωσε τη δυνατότητα σχεδίασης ενός SoC το οποίο είναι σε θέση να συνδυάσει ένα επεξεργαστή γενικού και έναν επεξεργαστή ειδικού σκοπού με στόχο την γρήγορη επεξεργασία μεγάλου όγκου δεδομένων.

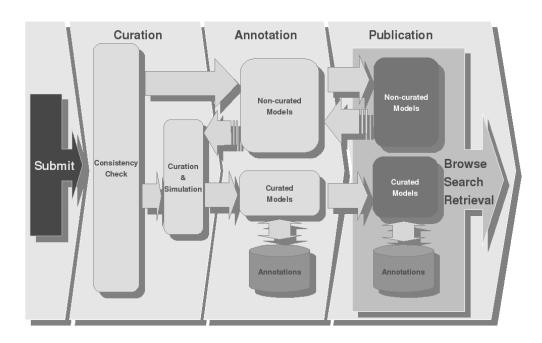

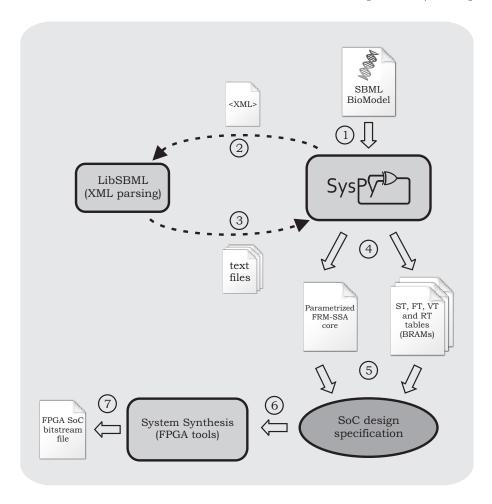

Συστήματα επεξεργασίας υψηλών επιδόσεων έχουν χρησιμοποιηθεί την τελευταία δεκαετία σε πολλά επιστημονικά πεδία, ειδικά για την επιτάχυνση της προσομοίωσης πολύπλοκων φυσικών φαινομένων π.χ. μετεωρολογικά και βιολογικά μοντέλα. Η υπολογιστική και συστημική βιολογία είναι επιστημονικά πεδία που επωφελήθηκαν από τη χρήση των νέων υπολογιστικών τεχνικών υψηλών επιδόσεων για την επεξεργασία δεδομένων από βιολογικές βάσεις δεδομένων. Η συστημική βιολογία ερευνά τη δυναμική των βιολογικών συστημάτων σαν ένα σύνολο επιμέρους συστημάτων, εντοπίζοντας έτσι τις αλληλεπιδράσεις μεταξύ των επιμέρους μονάδων και πώς αυτές καθορίζουν τα χαρακτηριστικά ολόκληρου του συστήματος. Προσομοιώνοντας τις αλληλεπιδράσεις διαφορετικών μοριακών ειδών, μπορεί να μελετηθεί η συμπεριφορά τους in silico (με τη χρήση υπολογιστών) και να εξαχθούν συμπεράσματα για την συμπεριφορά ενός κυττάρου ή ενός συνόλου κυττάρων. Η στοχαστική προσομοίωση βιοχημικών δικτύων αντιδράσεων που ονομάζονται βιολογικά μοντέλα ή βιομοντέλα (BioModels) [57], [17], μπορεί να οδηγήσει σε συμπεράσματα για τις ιδιότητες ενός βιολογικού συστήματος. Για την αναπαράσταση των μοντέλων γίνεται χρήση της γλώσσας ΧΜL και του προτύπου Systems Biology Markup Language (SBML) [42].

Η εξέλιξη ενός βιολογικού συστήματος μπορεί να προσομοιωθεί χρησιμοποιώντας συνήθης διαφορικές εξισώσεις. Η λύση όμως διαφορικών εξισώσεων δεν είναι ο ενδεδειγμένος τρόπος, ειδικά όταν οι ποσότητες των μοριακών ειδών που εμπλέκονται είναι μικρές [69]. Σε αυτή την περίπτωση είναι πολύ δύσκολο να προσομοιωθεί η συμπεριφορά του συστήματος και η χρονική εξέλιξη των χημικών αντιδράσεων. Για την αντιμετώπιση αυτών των προβλημάτων, αντί για διαφορικές εξισώσεις, μπορεί να γίνει χρήση στοχαστικών μοντέλων για την προσομοίωση δικτύων βιοχημικών αντιδράσεων. Η προσομοίωση με χρήση στοχαστικών μοντέλων μπορεί να περιγραφεί ως μίας διαδικασία Markov [36], όπου η επόμενη κατάσταση ενός συστήματος εξαρτάται μόνο από την αμέσως προηγούμενη κατάσταση. Ο D. T. Gillespie πρότεινε έναν βελτιωμένο αλγόριθμο για τη στοχαστική προσομοίωση βιολογικών μοντέλων, ο οποίος ονομάζεται First Reaction Method (FRM) [35].

Το σύστημα το οποίο σχεδιάσαμε δέχεται αρχεία βιολογικών μοντέλων σαν δεδομένα εισόδου και χρησιμοποιεί τον αλγόριθμο FRM για την προσομοίωση των χημικών αντιδράσεων που περιγράφονται στα μοντέλα. Το SoC υλοποιεί την πρωταρχική υλοποίηση του αλγορίθμου FRM, όπως αυτή διατυπώθηκε από τον Gillespie, χωρίς να γίνεται χρήση αριθμητικών προσεγγίσεων στο υλικό, κάτι που συνηθίζεται στις υλοποιήσεις του αλγορίθμου σε λογισμικό και μειώνει την ακρίβεια των αποτελεσμάτων της προσομοίωσης. Έτσι επιταχύνεται σημαντικά η εκτέλεση στοχαστικής προσο-

μοίωσης στο υλικό, με τη χρήση μεθόδων παράλληλης επεξεργασίας, χωρίς να μειώνεται η ακρίβεια των αριθμητικών αποτελεσμάτων.

Με τη χρήση του SysPy για τη σχεδίαση του συστήματος επεξεργασίας βιολογικών δικτύων προσπαθήσαμε να εκτιμήσουμε τις δυνατότητες του εργαλείου και να εμπλουτίσουμε τις ακόλουθες δυνατότητες σχεδίασης που παρέχει:

- αυτόματη παραμετροποίηση και σύνδεση μονάδων υλικού (επεξεργαστής ειδικού σκοπού για την υλοποίηση του αλγορίθμου FRM).

- χρήση των δυνατοτήτων της Python για την επεξεργασία του περιεχομένου αρχείων κειμένου τύπου ASCII (επεξεργασία αρχείων βιομοντέλων XML).

- χρήση της Python για την ανάπτυξη λογισμικού διεπαφής Η/Υ με την υλοποίηση SoC σε μονάδα FPGA (ανάπτυξη λογισμικού HAL: Hardware Abstraction Layer).

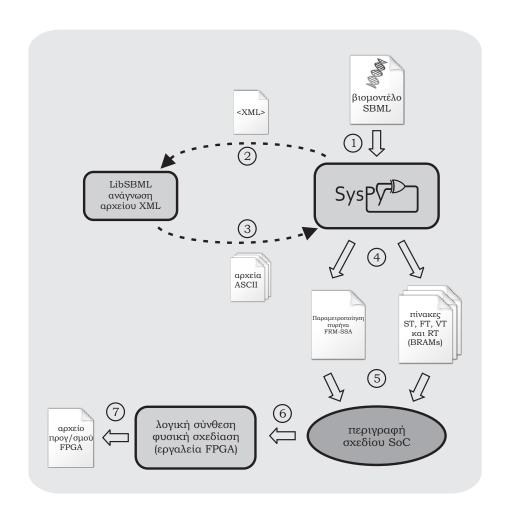

Χρησιμοποιώντας τις δυνατότητες του SyPy υλοποιήσαμε ένα σχέδιο SoC [61] το οποίο συνδυάζει τον πυρήνα του επεξεργαστή Leon3 με τον επεξεργαστή ειδικού σκοπού που σχεδιάστηκε από την ερευνητική μας ομάδα μας [40] και υλοποιεί τον αλγόριθμο FRM. Οι δυνατότητες του SysPy ήταν ιδιαίτερα χρήσιμες στην αρχικοποίηση και σύνδεση του επεξεργαστή ειδικού σκοπού, ειδικά στην επεξεργασία των αρχείων XML των βιομοντέλων σε μορφή SBML και στην αρχικοποίηση του μοντέλου στις διαθέσιμες μονάδες μνήμης του SoC.

Η λίστα των διαθέσιμων παραμέτρων του επεξεργαστή FRM παρουσιάζεται στον Πίναχα Π1.3. Υλοποιήσαμε τρεις διαφορετικές εκδόσεις του επεξεργαστή, με έναν (FRM1X), δύο (FRM2X) και τέσσερις (FRM4X) επεξεργαστές (PE: Processing Element) που λειτουργούν παράλληλα (N=1 ή 2 ή 4). Ο αριθμός των χημικών αντιδράσεων m και το πλήθος των χημικών ειδών n εξάγονται αυτόματα από το αρχείο του βιομοντέλου, ενώ οι υπόλοιπος παράμετροι που αναφέρονται στον πίνακα παρέχονται από τον χρήστη. Για κάθε επεξεργαστή FRM απαιτείται η αρχικοποίηση της τυχαίας γεννήτριας αριθμού ( $r_j$ ) που περιέχουν και χρησιμοποιείται από τον αλγόριθμο FRM. Το σύστημα μπορεί να επεξεργαστεί βιομοντέλα με δύο διαφορετικούς τρόπους: α) προσομοίωση m/N από κάθε επεξεργαστή ειδικού σκοπού (SSIP: Single Simulation In Parallel) και β) προσομοίωση όλων των αντιδράσεων m παράλληλα από όλους του επεξεργαστές N (MSIP: Multiple Simulations In Parallel).

| Parameter | Name                                         | Range                |

|-----------|----------------------------------------------|----------------------|

| m         | Πλήθος αντιδράσεων                           | $2^e, e \in [0, 12]$ |

| n         | Πλήθος χημικών ειδών                         | $2^e, e \in [0, 12]$ |

| q         | Πλήθος αντιδρώντων (βαθμός αντίδρασης)       | [1 - 3]              |

| $N_{rep}$ | Πλήθος επαναλήψεων προσομοίωσης              |                      |

| RNGseed   | Αρχικές τιμές της γεννήτριας τυχαίων αριθμών | [0 - 255]            |

| K         | Τρόπος λειτουργίας                           | [0 = SSIP, 1 = MSIP] |

| $T_{sim}$ | $\Delta$ ιάρχεια προσομοίωσης (sec.)         |                      |

Πίναχας Π1.3: Παράμετροι του επεξεργαστή ειδιχού σχοπού υλοποίησης του αλγορίθμου FR.M.

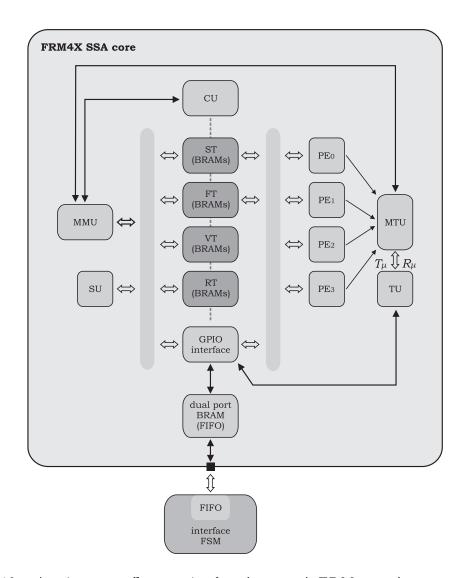

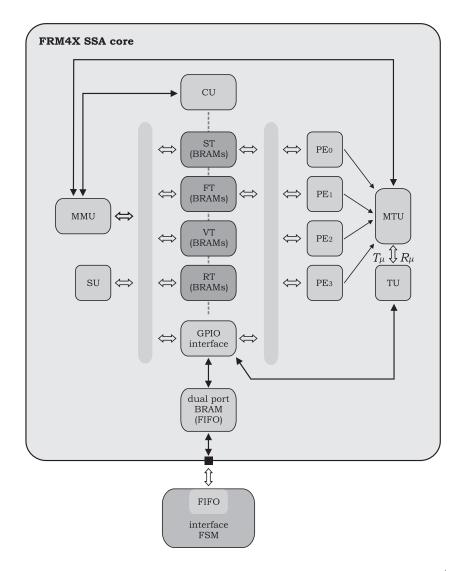

Στο Σχήμα Σ1.12 παρουσιάζουμε τη δομή του επεξεργαστή ειδικού σκοπού FRM με τέσσερις επεξεργαστές (FRM4X). Τα βήματα επεξεργασίας του αλγορίθμου υλοποιούνται από την μονάδα ελέγχου (CU: Control Unit). Σε μία σειρά από μονάδες μνήμης καταχωρούνται οι παράμετροι του δικτύου χημικών αντιδράσεων, όπως αυτό περιγράφεται στο αρχείο του βιομοντέλου. Οι μονάδες μνήμης είναι ο πίνακας αντιδράσεων (RT: Reaction Table), ο πίνακας στοιχειομετρίας (VT: Stoichiometry Table), ο πίνακας χημικών ειδών (ST: Species Table) και ο πίνακας χρονοπρογραμματισμού που περιέχει τις τιμές διαφόρων σημάτων ελέγχου (FT: Flags Table). Η μονάδα διαχείρισης μνήμης (MMU: Memory Management Unit) διαχειρίζεται και συγχρονίζει την πρόσβαση σε όλες τις μονάδες μνήμης.

Σχήμα  $\Sigma 1.12$ : Δομή του επεξεργαστή ειδικού σκοπού FRM με τέσσερα επεξεργαστικά στοιχεία.

Η επίδοση της επεξεργαστικής ισχύς του επεξεργαστή FRM μετράται σε κύκλους προσομοίωσης ανά δευτερόλεπτο (RC: Reaction Cycles/sec.). Σε κάθε κύκλο προσομοίωσης επεξεργάζονται 10x32-bit=320-bit, ενώ υποστηρίζονται βιομοντέλα με μέγιστο αριθμό τριών αντιδρώντων στοιχείων και πέντε παραγώγων αντίδρασης. Με τη χρήση της Python γίνεται δυνατή η επεξεργασία των βιομοντέλων σε μορφή αρχείων XML και η χρήση των δεδομένων που περιέχουν για την αρχικοποίηση μονάδων υλικού, όπως αυτή περιγράφεται και στο Σχήμα  $\Sigma 1.4$ . Η διαδικασία εξαγωγής πληροφοριών από τα μοντέλα XML παρουσιάζεται και στο Σχήμα  $\Sigma 1.13$ .

Σχήμα  $\Sigma 1.13$ : Επεξεργασία βιομοντέλων SBML με στόχο την εξαγωγή πληροφοριών για την αρχικοποίηση του πυρήνα υλοποίησης του αλγορίθμου FRM.

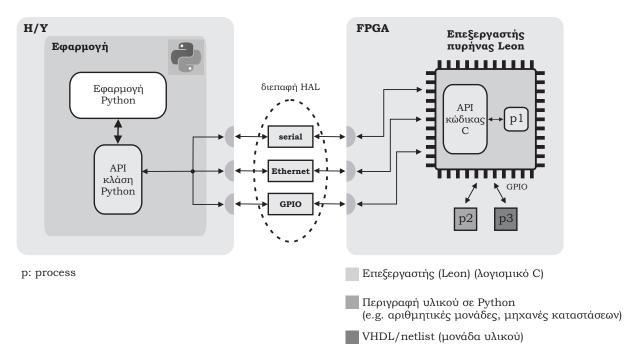

Η δημιουργία της διεπαφής HAL, με λογισμικό C να εκτελείται στον επεξεργαστή Leon στο SoC το οποίο επικοινωνεί μέσω σύνδεσης Ethernet με λογισμικό Python που εκτελείται στον H/Y, ήταν απαραίτητη για: α) να διαχειρίζεται τη ροή των δεδομένων από τον H/Y στο SoC και αντίστροφα και β) να ελέγχει την πρόσβαση του SoC στη μνήμη SDRAM στην πλακέτα του FPGA. Το λογισμικό HAL διαχειρίζεται την ανταλλαγή πληροφοριών στα κανάλια δεδομένων Ethernet (H/Y - SoC), GPIO (Leon - επεξεργαστής FRM ειδικού σκοπού) και στο σειριακό κανάλι ελέγχου μέσω του οποίου χρονίζεται η εκτέλεση του λογισμικού HAL στον Leon και στον H/Y.

Σχήμα Σ1.14: Σύνδεση του Η/Υ με την πλακέτα FPGA και το SoC επεξεργασία βιολογικών δεδομένων, μέσω της χρήσης του λογισμικού HAL.

Στο Σχήμα Σ1.14 παρουσιάζεται η σύνδεση του Η/Υ με την πλαχέτα FPGA και το SoC επεξεργασία βιολογικών δεδομένων, μέσω της χρήσης του λογισμικού HAL. Στο σχήμα παρουσιάζεται ο διαχωρισμός του HAL στην υλοποίηση Python στον Η/Υ και στην υλοποίηση C που εκτελεί ο επεξεργαστής Leon. Η υλοποίηση του HAL παρέχει μεθόδους για την ανταλλαγή δεδομένων και στα τρία διαθέσιμα κανάλια επικοινωνίας του SoC (Ethernet, GPIO, serial connection). Η εκτέλεση των διαθέσιμων μεθόδων στην Python, έχει ως αποτέλεσμα την εκτέλεση των αντίστοιχων μεθόδων C στον επεξεργαστή. Η ανταλλαγή των δεδομένων στο κανάλι Ethernet γίνεται με χρήση πακέτων δεδομένων τύπου MAC με ταχύτητα 100Mbps, ενώ με συχνότητα λειτουργίας του επεξεργαστή στα 160MHz, η ανταλλαγή δεδομένων στο κανάλι GPIO γίνεται με ταχύτητα 25Mbps.

Με την ανάπτυξη του λογισμικού HAL παρουσιάσαμε μία ολοκληρωμένη μεθοδολογία χρήσης μιας αντικειμενοστραφούς γλώσσας όπως η Python για την διαχείριση επεξεργασίας δεδομένων από ένα ενσωματωμένο σύστημα. Με τη χρήση κλάσεων και μεθόδων γίνεται εφικτή η δέσμευση επεξεργαστικών στοιχείων και η δέσμευση καναλιών επικοινωνίας στην πλακέτα του FPGA. Προσπάθεια χρήσης αντικειμενοστραφούς γλώσσας για δέσμευση πόρων σε ενσωματωμένο σύστημα έχει γίνει και στο παρελθόν με τη χρήση της γλώσσας Java [82]. Η ανάπτυξη του HAL για τις ανάγκες χρήσης του SysPy, είναι η πρώτη προσπάθεια να χρησιμοποιηθεί μια ευέλικτη και δημοφιλής γλώσσα όπως η Python για την διαχείριση της επεξεργασίας δεδομένων σε ένα ενσωματωμένο SoC. Η χρήση της

|           | Leon3       | Leon+FRM1X  | Leon+FRM2X   | Leon+FRM4X   |

|-----------|-------------|-------------|--------------|--------------|

| Slices    | 5,436 (31%) | 9,244 (53%) | 13,214 (76%) | 16,594 (96%) |

| BRAMs     | 17 (11%)    | 56 (37%)    | 78 (52%)     | 132 (89%)    |

| MULs      | 0 (0%)      | 16 (25%)    | 26 (41%)     | 48 (75%)     |

| Power (W) | 0.6         | 4.1         | 4.8          | 5.9          |

Πίναχας Π1.4: Αποτελέσματα δέσμευσης λογικών πόρων στη μονάδα FPGA Virtex-5 LX110T (CLB: δύο slices, Slice: τέσσερα 6- εισόδων LUTs, BRAM: 36Kb, DSP48: 25x18-bit)

Python δίνει ευελιξία στην διαχείριση των λειτουργιών ενός SoC και επίσης δίνει δυνατότητα για προεπεξεργασία των δεδομένων που αποστέλλονται στο ενσωματωμένο σύστημα και χρονισμό των βημάτων επεξεργασίας τους στην πλακέτα του FPGA, με χρήση προγραμμάτων Python script στον H/Y.

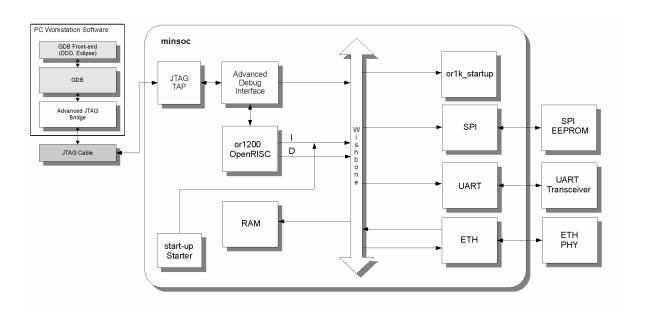

$\Sigma$ χήμα  $\Sigma 1.15$ :  $\Sigma$ ύνδεση του επεξεργαστή Leon με τον επεξεργαστή FRM ειδιχού σχοπού.

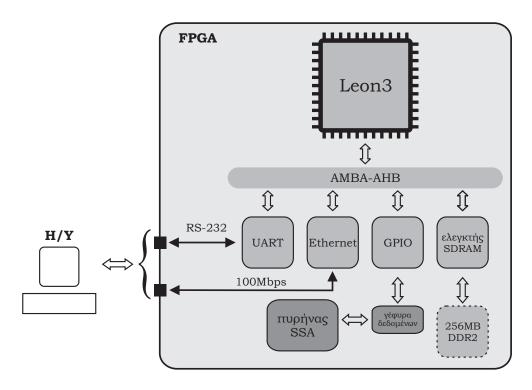

Στο Σχήμα Σ1.15 παρουσιάζεται η τοπολογία του SoC με χρήση της πλακέτα FPGA ML509. Ο ελεγκτής Ethernet και η μνήμη SDRAM χρονίζονταν στα 190MHz, ενώ για τον επεξεργαστή Leon έγινε χρήση σήματος ρολογιού στα 160MHz. Τα σήματα ρολογιού παρήχθησαν με χρήση

του διαθέσιμου ταλαντωτή των 100ΜΗz στην πλακέτα και μονάδας διαχείρισης σημάτων ρολογιού (DCM: Digital Clock Manager) στο FPGA. Η σύνδεση του Η/Υ και της πλακέτας FPGA έγινε μέσω σειριαχού χαλωδίου RS-232 και χαλωδίου διχτύου Ethernet. Για τον έλεγχο της λειτουργίας του συστήματος έγινε χρήση ενός πολύπλοκου βιομοντέλου [78], το οποίο περιγράφει ένα βιοχημικό δίκτυο με n=93 είδη και m=136 αντιδράσεις. Το συγκεκριμένο μοντέλο περιγράφει την συμπεριφορά της πρωτεΐνης Α-συνουκλεΐνης, η οποία σχετίζεται με τη νόσο του Πάρκινσον. Τα αποτελέσματα της δέσμευσης πόρων στο FPGA μετά την υλοποίηση του SoC με ένα (FRM1X), δύο (FRM2X) και τέσσερα (FRM4X) επεξεργαστικά στοιχεία, παρουσιάζονται στον Πίνακα Π1.4. Όσο αυξάνεται η πολυπλοκότητα ενός βιομοντέλου (μεγαλύτερο πλήθος στοιχείων και αντιδράσεων) τόσο αυξάνονται και οι απαιτήσεις στο υλικό, ειδικά σε σχέση με τον αριθμό των διαθέσιμων μονάδων ΒRAM στο FPGA. Παρατηρούμε επίσης ότι ο επεξεργαστής Leon δεσμεύει έναν σχετικά μικρό αριθμό λογικών πόρων (περίπου το 1/3 των λογικών μονάδων και το 11% των μονάδων μνήμης). Επίσης ο επεξεργαστής καταναλώνει μόλις το 10% της συνολικής ισχύος του κυκλώματος, ενώ την μεγαλύτερη ισχύ καταναλώνουν οι αριθμητικές μονάδες και οι μονάδες μνήμης. Συνεπώς η χρήση του επεξεργαστή, βοηθάει πάρα πολύ στη δέσμευση και χρήση μονάδων επικοινωνίας (Ethernet) και μονάδων μνήμης (SDRMA), ενώ ταυτόχρονα καταλαμβάνει μικρό μέρος των διαθέσιμων πόρων και καταναλώνει επίσης μιχρό μέρος της ισχύος ενός FPGA.

Για να εκτιμήσουμε τις επεξεργαστικές δυνατότητες του SoC, συγκρίναμε το ρυθμό επεξεργασίας και προσομοίωσης δεδομένων που καταγράψαμε στο υλικό με αυτόν που αντίστοιχα καταγράψαμε κάνοντας χρήση δημοφιλών εργαλείων λογισμικού προσομοίωσης δικτύων βιοχημικών αντιδράσεων. Τα εργαλεία λογισμικού που χρησιμοποιήσαμε είναι το iBioSim [70] και το StochPy [85] και εκτελέσαμε προσομοιώσεις με χρήση σύγχρονων υπολογιστικών μονάδων (64-bit PC, 6GB RAM, Intel i7, 2.6GHz, quad-core CPU). Εκτελώντας πλήθος προσομοιώσεων καταγράψαμε 0.35MReactions/sec. ρυθμός προσομοίωσης στο υλικό, απόδοση που είναι περίπου 50 φορές μεγαλύτερη από την απόδοση των iBioSim και StochPy. Εκτός του ότι η υλοποίηση στο FPGA επιταχύνει δραματικά την προσομοίωση των βιομοντέλων, παρέχει επίσης μια πλατφόρμα προσομοίωσης πολύ μικρότερου μεγέθους και με πολύ χαμηλή κατανάλωση ισχύος, σε σύγκριση με υλοποιήσεις λογισμικού που απαιτούν τη χρήση μεγάλων υπολογιστικών μονάδων για να επιτύχουν συγκρίσιμους ρυθμούς επεξεργασίας δεδομένων.

## 1.4.3 SoC επεξεργασίας ήχου

Με τη χρήση του SysPy και του επεξεργαστή Leon καταφέραμε να σχεδιάσουμε ένα αρκετά πολύπλοκο SoC και να αναδείξουμε τις δυνατότητες του εργαλείου στη χρήση σε ένα ενσωματωμένο σύστημα ενός

επεξεργαστή 32-bit σαν πύλη επιχοινωνίας με άλλες μονάδες στην πλαχέτα του FPGA αλλά χαι εχτός αυτής. Ειδιχότερα η χρήση του Leon μας επέτρεψε να συνδέσουμε το SoC και την πλαχέτα FPGA σε δίχτυο Ethernet όπου λειτουργούσε σαν συνεπεξεργαστής του H/Y που επιχοινωνούσε μέσω διχτύου. Στα πλαίσια της σχεδίασης ενός SoC επεξεργασία ήχου, δύο σημαντιχές προσθήκες έγιναν στο SysPy. Αναπτύχθηκε ο μηχανισμός προσομοίωσης που δίνει τη δυνατότητα προσομοίωσης ενός SoC με χρήση περιγραφών υψηλού επιπέδου. Επίσης ενσωματώθηκε η χρήση λειτουργιχού συστήματος Linux για την ανάπτυξη εφαρμογών σε γλώσσα C στον επεξεργαστή Leon. Η χρήση του λειτουργιχού συστήματος δίνει τη δυνατότητα επιχοινωνίας του FPGA με τον H/Y και ανταλλαγής δεδομένων σε επίπεδο αρχείων, μέσω του πρωτοχόλλου μεταφοράς δεδομένων File Transfer Protocol (FTP). Επίσης δίνεται η δυνατότητα σύνδεσης του FPGA στο διχτύου Ethernet με χρήση διεύθυνσης IP, δίνοντας πρόσβαση στη μονάδα του FPGA σε πλήθος εφαρμογών που χρησιμοποιούν τη συγχεχριμένη μέθοδο διευθυνσιοδότησης.

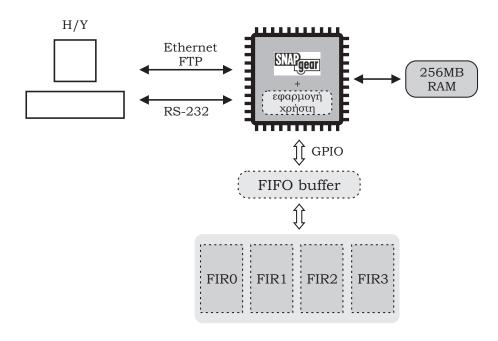

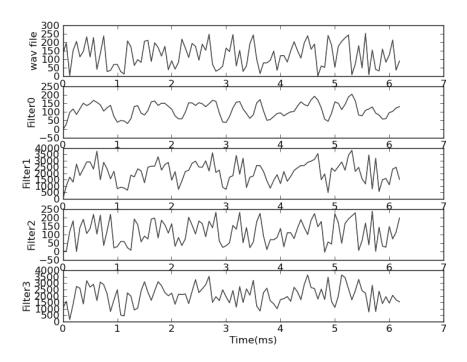

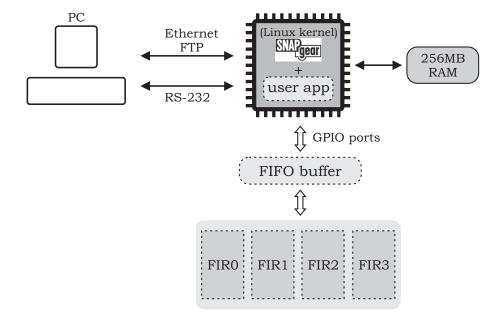

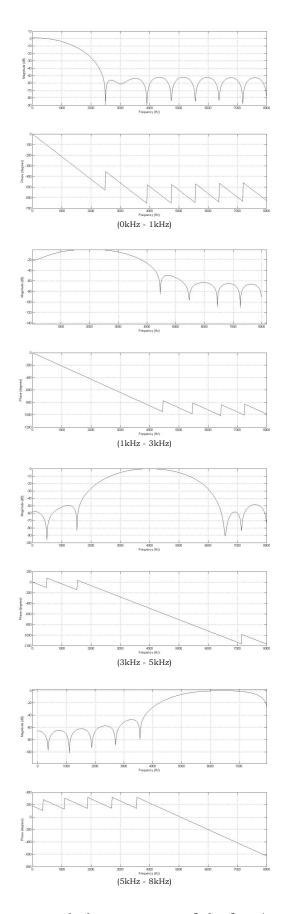

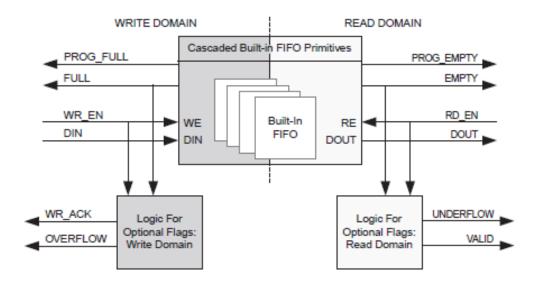

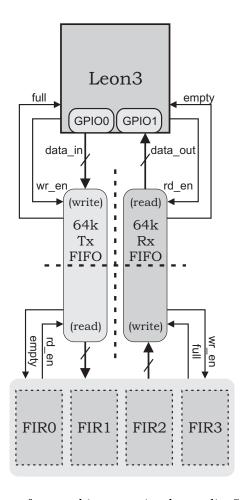

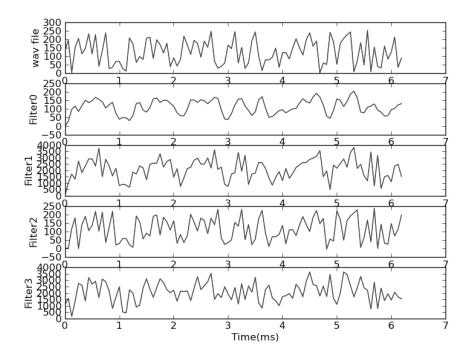

Το διάγραμμα του νέου σχεδίου SoC παρουσιάζεται στο Σχήμα Σ1.16. Ο επεξεργαστής Leon λειτουργεί ως FTP client, όπου εκτελείται επίσης η εφαρμογή του χρήστη που επεξεργάζεται τα μουσικά αρχεία που λαμβάνονται από τον H/Y. Με τη χρήση του λειτουργικού συστήματος οι εφαρμογές του χρήστη μεταγλωττίζονται μαζί με τον πυρήνα του λειτουργικού Snapgear Linux. Ο στόχος της σχεδίασης του SoC είναι η ταξινόμηση των μουσικών αρχείων σε διαφορετικές κατηγορίες, σύμφωνα με τον τον τύπο της μουσικής που περιέχουν (π.χ. ηλεκτρονική, ροκ ή κλασσική μουσική). Η ταξινόμηση γίνεται σύμφωνα με το συχνοτικό περιεχόμενο των αρχείων, το οποίο εκτιμάται μέσω τεσσάρων ζωνοπερατών (bandpass) φίλτρων τύπου Finite Impulse Response (FIR), τα οποία είναι συνδεδεμένα σαν περιφερειακές μονάδες του επεξεργαστή. Τα αρχεία καταχωρούνται στη μνήμη SDRAM στην πλακέτα του FPGA και από εκεί προωθούνται προς τις μονάδες των φίλτρων οι οποίες συνδέονται μέσω θυρών GPIO με τον επεξεργαστή. Σειριακή σύνδεση μεταξύ του Η/Υ και της πλακέτας FPGA χρησιμοποιείται για να παρέχει πρόσβαση στη γραμμή εντολών του λειτουργικού συστήματος Linux, από όπου ο χρήστης ελέγχει την εκτέλεση της εφαρμογής του και την ανταλλαγή δεδομένων μέσω του πρωτοκόλλου FTP.

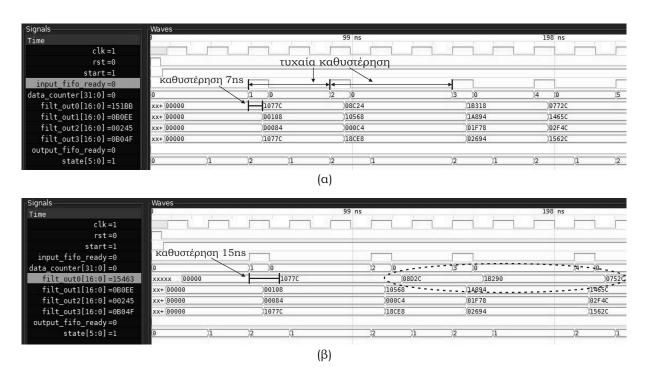

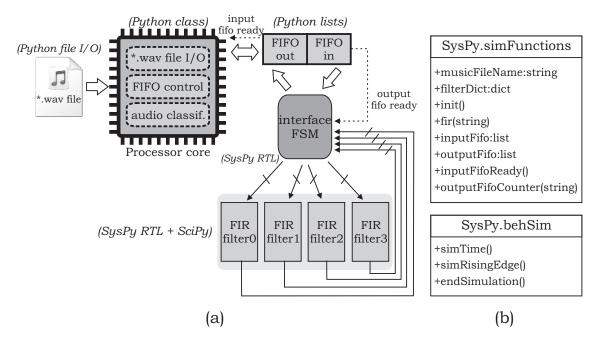

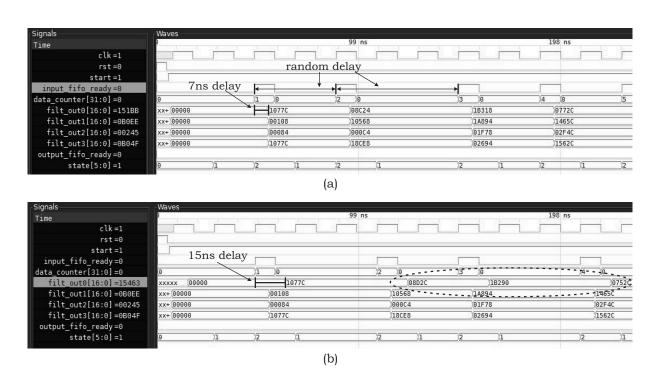

Ξεχινήσαμε τη σχεδίαση του συστήματος με την προδιαγραφή μοντέλων για την προσομοίωση του συστήματος, συμβατά με τον μηχανισμό προσομοίωσης που αναπτύχθηκε στο SysPy και τα χαρακτηριστικά του περιγράφονται στο Κεφάλαιο. Στο Σχήμα Σ1.16 παρουσιάζονται με διακεκομμένες γραμμές τα στοιχεία εκείνα του λογισμικού και του υλικού για τα οποία δημιουργήσαμε μοντέλα προσομοίωσης στο SysPy.Τα αποτελέσματα της προσομοίωσης σε υψηλό επίπεδο με τη χρήση μοντέλων του συστήματος σε γλώσσα Python, βοήθησαν στο να πάρουμε σημαντικές αποφάσεις σχετικά με την αρχιτεκτονική του συστήματος όπως: α) τις παραμέτρους των φίλτρων, π.χ. βαθμός φίλτρων,

Σχήμα Σ1.16: Διάγραμμα μονάδων του SoC επεξεργασίας ήχου.

μορφή αναπαράστασης αριθμών κτλ., β) το μέγεθος των μνημών FIFO (First In First Out) προσωρινής καταχώρησης δεδομένων (data buffers) μεταξύ του επεξεργαστή και των φίλτρων και γ) την ανάπτυξη του λογισμικού ελέγχουν που εκτελείται στον επεξεργαστή.