### NATIONAL AND KAPODISTRIAN UNIVERSITY OF ATHENS

### SCHOOL OF SCIENCES DEPARTMENT OF INFORMATICS AND TELECOMMUNICATIONS

### **PROGRAM OF POSTGRADUATE STUDIES**

PhD THESIS

# Design and Synthesis of Efficient Circuits for Quantum Computers

Archimedes D. Pavlidis

ATHENS

DECEMBER 2016

### ΕΘΝΙΚΟ ΚΑΙ ΚΑΠΟΔΙΣΤΡΙΑΚΟ ΠΑΝΕΠΙΣΤΗΜΙΟ ΑΘΗΝΩΝ

### ΣΧΟΛΗ ΘΕΤΙΚΩΝ ΕΠΙΣΤΗΜΩΝ ΤΜΗΜΑ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΤΗΛΕΠΙΚΟΙΝΩΝΙΩΝ

### ΠΡΟΓΡΑΜΜΑ ΜΕΤΑΠΤΥΧΙΑΚΩΝ ΣΠΟΥΔΩΝ

ΔΙΔΑΚΤΟΡΙΚΗ ΔΙΑΤΡΙΒΗ

# Σχεδίαση και Σύνθεση Αποδοτικών Κυκλωμάτων για Κβαντικούς Υπολογιστές

Αρχιμήδης Δ. Παυλίδης

AOHNA

ΔΕΚΕΜΒΡΙΟΣ 2016

#### **PhD THESIS**

Design and Synthesis of Efficient Circuits for Quantum Computers

#### Archimedes D. Pavlidis

SUPERVISOR: Dimitris Gizopoulos, Professor

#### THREE-MEMBER ADVISORY COMMITTEE:

Dimitris Gizopoulos, Professor Antonis Paschalis, Professor Dimitris Syvridis, Professor

#### SEVEN-MEMBER EXAMINATION COMMITTEE

(Signature)

#### Dimitris Gizopoulos, Professor NKUA

(Signature)

(Signature)

#### Antonis Paschalis, Professor NKUA

(Signature)

#### Dimitris Syvridis, Professor NKUA

(Signature)

### Manolis Floratos, Professor Emeritus NKUA

Angela Arapoyanni, Professor NKUA

(Signature)

#### Kiamal Pekmestzi, Professor NTUA

(Signature)

#### Dimitris Soudris, Associate Professor NTUA

Examination Date 20/12/2016

#### ΔΙΔΑΚΤΟΡΙΚΗ ΔΙΑΤΡΙΒΗ

Σχεδίαση και Σύνθεση Αποδοτικών Κυκλωμάτων για Κβαντικούς Υπολογιστές

Αρχιμήδης Δ. Παυλίδης

ΕΠΙΒΛΕΠΩΝ ΚΑΘΗΓΗΤΗΣ: Δημήτρης Γκιζόπουλος, Καθηγητής ΕΚΠΑ

ΤΡΙΜΕΛΗΣ ΕΠΙΤΡΟΠΗ ΠΑΡΑΚΟΛΟΥΘΗΣΗΣ: **Δημήτρης Γκιζόπουλος**, Καθηγητής ΕΚΠΑ Αντώνης Πασχάλης, Καθηγητής ΕΚΠΑ **Δημήτρης Συβρίδης**, Καθηγητής ΕΚΠΑ

#### ΕΠΤΑΜΕΛΗΣ ΕΞΕΤΑΣΤΙΚΗ ΕΠΙΤΡΟΠΗ

(Υπογραφή)

#### Δημήτρης Γκιζόπουλος, Καθηγητής ΕΚΠΑ

#### Αγγελική Αραπογιάννη, Καθηγήτρια ΕΚΠΑ

(Υπογραφή)

#### Κιαμάλ Πεκμεστζή, Καθηγητής ΕΜΠ

(Υπογραφή)

Μανώλης Φλωράτος,

Ομότιμος Καθηγητής ΕΚΠΑ

#### Δημήτρης Σούντρης, Αναπληρωτής Καθηγητής ΕΜΠ

Ημερομηνία Εξέτασης 20/12/2016

(Υπογραφή)

Δημήτρης Συβρίδης,

Καθηγητής ΕΚΠΑ

(Υπογραφή)

(Υπογραφή)

Αντώνης Πασχάλης,

Καθηγητής ΕΚΠΑ

(Υπογραφή)

### ABSTRACT

The recent advances in the field of experimental construction of quantum computers with increased fidelity components shows that large-scale machines based on the principles of guantum physics are likely to be realized in the near future. As the size of the future quantum computers will be increased, efficient quantum circuits and design methods will gradually gain practical interest. The contribution of this thesis towards the design of efficient quantum circuits is two-fold. The first is the design of novel efficient quantum arithmetic circuits based on the Quantum Fourier Transform (QFT), like multiplier-withconstant-and-accumulator (MAC) and divider by constant, both of linear depth (or speed) with respect with the bits number of the integer operands. These circuits are effectively combined so as they can perform modular multiplication by constant in linear depth and space and consequently modular exponentiation in quadratic time and linear space. Modular exponentiation and modular multiplication operations are integral parts of the important quantum factorization algorithm of Shor and other quantum algorithms of the same family, known as Quantum Phase Estimation algorithms. Important implementation problems like the required high accuracy of the employed rotation quantum gates and the local communications between the gates are effectively addressed. The second contribution of this thesis is a generic hierarchical synthesis methodology for arbitrary complex and large quantum and reversible circuits. The methodology can handle more easily larger circuits relative to the flat synthesis methods. The proposed method offers advantages over the standard hierarchical synthesis which uses Bennett's method of "compute-copyuncompute".

SUBJECT AREA: Quantum Computing

**KEYWORDS:** Quantum Computer Architectures, Quantum Arithmetic Circuits, Quantum Fourier Transform, Quantum Circuits Synthesis, Reversible Circuits Synthesis

### ΠΕΡΙΛΗΨΗ

Οι πρόσφατες εξελίξεις στον τομέα της πειραματικής κατασκευής κβαντικών υπολογιστών με εξαρτήματα αυξημένης αξιοπιστίας δείχνει ότι η κατασκευή τέτοιων μεγάλων μηχανών βασισμένων στις αρχές της κβαντικής φυσικής είναι πιθανή στο κοντινό μέλλον. Καθώς το μέγεθος των μελλοντικών κβαντικών υπολογιστών θα αυξάνεται, η σχεδίαση αποδοτικότερων κβαντικών κυκλωμάτων και μεθόδων σχεδίασης θα αποκτήσει σταδιακά πρακτικό ενδιαφέρον. Η συνεισφορά της διατριβής στην κατεύθυνση της σχεδίασης αποδοτικών κβαντικών κυκλωμάτων είναι διττή: Η πρώτη είναι η σχεδίαση καινοτόμων αποδοτικών αριθμητικών κβαντικών κυκλωμάτων βασισμένων στον Κβαντικό Μετασχηματισμό Fourier (QFT), όπως πολλαπλασιαστής-με-σταθερά-συσσωρευτής (MAC) και διαιρέτης με σταθερά, με γραμμικό βάθος (ή ταχύτητα) ως προς τον αριθμό ψηφίων των ακεραίων. Αυτά τα κυκλώματα συνδυάζονται αποτελεσματικά ώστε να επιτελέσουν την πράξη του modulo πολλαπλασιασμού με σταθερά με γραμμική πολυπλοκότητα χρόνου και χώρου και συνεπώς μπορούν να επιτελέσουν την πράξη της modulo εκθετικοποίησης (modular exponentiation) με τετραγωνική πολυπλοκότητα χρόνου και γραμμική πολυπλοκότητα χώρου. Οι πράξεις της modulo εκθετικοποίησης και του modulo πολλαπλασιασμού είναι αναπόσπαστα μέρη του σημαντικού κβαντικού αλγορίθμου παραγοντοποίησης του Shor, αλλά και άλλων κβαντικών αλγορίθμων της ίδιας οικογένειας, γνωστών ως κβαντική εκτίμηση φάσης (Quantum Phase Estimation). Αντιμετωπίζονται με αποτελεσματικό τρόπο σημαντικά προβλήματα υλοποίησης, που σχετίζονται με την απαίτηση χρήσης κβαντικών πυλών περιστροφής υψηλής ακρίβειας, καθώς και της χρήσης τοπικών επικοινωνιών. Η δεύτερη συνεισφορά της διατριβής είναι μία γενική μεθοδολογία ιεραρχικής σύνθεσης κβαντικών και αντιστρέψιμων κυκλωμάτων αυθαίρετης πολυπλοκότητας και μεγέθους. Η ιεραρχική μέθοδος σύνθεσης χειρίζεται καλύτερα μεγάλα κυκλώματα σε σχέση με τις επίπεδες μεθόδους σύνθεσης. Η προτεινόμενη μέθοδος προσφέρει πλεονεκτήματα σε σχέση με τις συνήθεις ιεραρχικές συνθέσεις που χρησιμοποιούν την μέθοδο "υπολογισμός-αντιγραφήαντίστροφος υπολογισμός" του Bennett.

#### ΘΕΜΑΤΙΚΗ ΠΕΡΙΟΧΗ: Κβαντική Υπολογιστική

**ΛΕΞΕΙΣ ΚΛΕΙΔΙΑ:** Αρχιτεκτονικές Κβαντικών Υπολογιστών, Κβαντικά Αριθμητικά Κυκλώματα, Κβαντικός Μετασχηματισμός Fourier, Σύνθεση Κβαντικών Κυκλωμάτων, Σύνθεση Αντιστρέψιμων Κυκλωμάτων

Στην μνήμη των γονιών μου Δήμου και Ιφιγένειας, στην Κατερίνα και στους Δημοσθένη και Φίλιππο.

Ἐἀν ταῖς γλώσσαις τῶν ἀνθοώπων λαλῶ καὶ τῶν ἀγγέλων, ἀγάπην δὲ μὴ ἔχω, γέγονα χαλκὸς ἠχῶν ἢ κύμβαλον ἀλαλάζον. Καὶ ἐἀν ἔχω ποοφητείαν καὶ εἰδῶ τὰ μυστήοια πάντα καὶ πᾶσαν τὴν γνῶσιν, καὶ ἐἀν ἔχω πᾶσαν τὴν πίστιν, ὥστε ὄοῃ μεθιστάνειν, ἀγάπην δὲ μὴ ἔχω, οὐδέν εἰμι. καὶ ἐἀν ψωμίσω πάντα τὰ ὑπάοχοντά μου, καὶ ἐἀν παοαδῶ τὸ σῶμά μου ἵνα καυθήσομαι, ἀγάπην δὲ μὴ ἔχω, οὐδὲν ὦφελοῦμαι.

### ΕΥΧΑΡΙΣΤΙΕΣ

Τη σημερινή εποχή του μεγάλου ανταγωνισμού μεταξύ των ερευνητικών ομάδων για δημοσίευση αποτελεσμάτων αλλά και αναζήτησης χρηματοδοτούμενων ερευνητικών προγραμμάτων, απαιτείται η στόχευση σε εξειδικευμένες περιοχές όπου η ερευνητική ομάδα έχει αποκτήσει σημαντική εμπειρία αλλά και η δημιουργία κρίσιμης μάζας απασχολούμενων ερευνητών. Με αυτήν την έννοια η ερευνητική ενασχόληση με θέματα σχετικά αλλά όχι και στο κύριο ρεύμα ενδιαφερόντων της ομάδας θεωρείται πολλές φορές σπατάλη χρόνου.

Γι'αυτό το λόγο ευχαριστώ τον Καθηγητή του Τμήματος Πληροφορικής και Τηλεπικοινωνιών κο Δημήτρη Γκιζόπουλο για την εμπιστοσύνη που μου έδειξε και δέχθηκε να επιβλέψει την παρούσα διατριβή. Η εμπιστοσύνη αυτή συνεχίστηκε καθ'όλη τη διάρκεια της διατριβής όπου μου άφησε πολλούς βαθμούς ελευθερίας κινήσεων ως προς την κατεύθυνση της διατριβής, ακόμα και όταν υπήρχαν πρόσκαιρα προβλήματα σχετικά με την αποδοχή των δημοσιεύσεων. Η εμπειρία, η επιμονή και η αφιέρωση χρόνου από μέρους του ήταν κρίσιμα στοιχεία για την σωστή παρουσίαση των αποτελεσμάτων ώστε να γίνουν αποδεκτά από τους κριτές των περιοδικών και συνεδρίων όπου αποστάλθηκαν για δημοσίευση. Ο ενθουσιασμός του, συχνά μεγαλύτερος από τον δικό μου, έδινε θάρρος για την συνέχεια της προσπάθειας. Το σημαντικότερο όμως στοιχείο που συνέβαλε στην ολοκλήρωση της διατριβής ήταν η προσωπικότητά του, η οποία επέτρεψε να υπάρχει αγαστή συνεργασία μεταξύ μας και μετέτρεψε την διαδικασία εκπόνησης της διατριβής σε μία ευχάριστη ενασχόληση.

Ευχαριστίες οφείλονται και στον Καθηγητή του Τμήματος Φυσικής κο Μανώλη Φλωράτο. Η συνεργασία που ξεκίνησε μαζί του περίπου στο μέσο της εκπόνησης της διατριβής άνοιξε νέες κατευθύνσεις για την εκμετάλλευση των μεθοδολογιών που αναπτύχθηκαν και συνεισέφερε στην ψυχολογική ενθάρρυνση για την περάτωσή της.

Επίσης, ευχαριστώ τους Επίκουρους Καθηγητές του Πανεπιστημίου Πειραιώς Μιχάλη Ψαράκη και Γιώργο Πιτσέλη για την κριτική ανάγνωση τμημάτων της διατριβής.

Η διατριβή αυτή ολοκληρώθηκε χάρη στην υπομονή και ανοχή που έδειξε η οικογένειά μου, Κατερίνα, Δημοσθένης και Φίλιππος, όλα αυτά τα χρόνια και για αυτό θέλω να τους ευχαριστήσω, ιδιαίτερα όμως την Κατερίνα που επωμίστηκε το μεγαλύτερο βάρος.

### **PUBLICATIONS LIST**

- A. Pavlidis and D. Gizopoulos, "Fast Quantum Modular Exponentiation Architecture for Shor's Factoring Algorithm," *Quantum Information & Computation*, vol. 14, no 7&8, pp. 649-682, May 2014 (also in https://arxiv.org/abs/1207.0511)

- A. Pavlidis and D. Gizopoulos, "Hierarchical Synthesis of Quantum and Reversible Architectures," *Proc. 12th ACM International Conference on Computing Frontiers (CF'15)*, Ischia, Italy, May 2015, pp. 13:1-13:8 (*Best Paper Award Runner-up*)

- A. Pavlidis and D. Gizopoulos, "Hierarchical Synthesis of Quantum and Reversible Architectures," *International Journal of Parallel Programming*, vol. 44, no 5, pp. 1028-1053, October 2016 (*Special Issue; Extended version of the previous work*)

### ΣΥΝΟΠΤΙΚΗ ΠΑΡΟΥΣΙΑΣΗ

Η Θεωρία Κβαντικής Πληροφορίας και η Κβαντική Υπολογιστική είναι διακλαδικά ερευνητικά πεδία που συνδυάζουν με διαφορετικά βάρη τις επιστήμες της Φυσική, της Πληροφορική και των Μαθηματικών, ανάλογα με την οπτική γωνία που θέλει κάποιος να τα προσεγγίσει. Η Κβαντική Υπολογιστική θεωρείται σχετικά πρόσφατο ερευνητικό πεδίο, αν και η Θεωρία Κβαντικής Πληροφορίας έχει ξεκινήσει να αναπτύσσεται εδώ και 40 χρόνια, μετά από σημαντικά αποτελέσματα σύνδεσης της κλασικής Θεωρίας Πληροφορίας με την Κβαντική Μηχανική (ανισότητες κβαντικών εντροπιών [1, 2, 3], φράγματα Holevo για χωρητικότητα καναλιών κβαντικής πληροφορίας [4, 5], φράγμα Bekenstein [6], κ.α.).

Η θεωρητική σύνδεση Κβαντικής Μηχανικής με τη Θεωρία Υπολογισμού έγινε τη δεκαετία του 1980 [7, 8], και επιπλέον ώθηση δόθηκε τη δεκαετία του 1990 με την επινόηση αποδοτικών Κβαντικών Αλγορίθμων [9, 10, 11], δηλαδή αλγορίθμων που εκτελούνται σε υπολογιστικές μηχανές (Κβαντικούς Υπολογιστές) που εκμεταλλεύονται βασικές κβαντικές ιδιότητες της φύσης όπως η υπέρθεση (superposition), και ο εναγκαλισμός ή διεμπλοκή (entanglement). Οι αποδοτικοί κβαντικοί αλγόριθμοι μπορούν να επιφέρουν σημαντική μείωση της χρονικής πολυπλοκότητας, ώστε σε αρκετές περιπτώσεις, προβλήματα που δεν επιδέχονται λύση σε πολυωνυμικό χρόνο με τους ως τώρα γνωστούς αλγορίθμους για κλασικούς υπολογιστές, να επιλύονται σε πολυωνυμικό χρόνο από έναν κβαντικό υπολογιστή που εκτελεί έναν κβαντικό αλγόριθμο. Ένα γνωστό παράδειγμα με σημαντικές εφαρμογές στην Κρυπτογραφία είναι η παραγοντοποίηση ενός σύνθετου ακεραίου στους πρώτους παράγοντές του (αλγόριθμος παραγοντοποίησης του Shor) [10]. Άλλα σημαντικά παραδείγματα είναι η αποδοτική προσομοίωση της συμπεριφοράς κβαντικών φυσικών συστημάτων με αρκετούς βαθμούς ελευθερίας (όπως ένα σύνθετό χημικό μόριο), υπολογισμός που είναι πρακτικά ανέφικτος με συμβατικούς υπολογιστές [12].

Η φυσική υλοποίηση ενός κβαντικού υπολογιστή, ενώ θεωρητικά είναι εφικτή, απαιτεί μία πολυσύνθετη τεχνολογική προσπάθεια που οφείλει να αντιμετωπίσει διάφορα πρακτικά προβλήματα. Ένα σημαντικό πρόβλημα είναι ότι οι φορείς της κβαντικής πληροφορίας, τα qubits (quantum bits), είναι πολύ ευαίσθητα στην επίδραση του περιβάλλοντος και είναι πολύ δύσκολο να διατηρηθούν σε μία δεδομένη κατάσταση για ένα αξιοποιήσιμο χρονικό διάστημα. Οι φυσικοί φορείς της πληροφορίας μπορεί να είναι φωτόνια, άτομα, ιόντα, πυρήνες και γενικά μικροσκοπικά θεμελιώδη συστήματα στα οποία μπορούν να παρατηρηθούν κβαντικά φαινόμενα<sup>1</sup>. Το πρόβλημα της ευαισθησίας των φορέων στην επίδραση του περιβάλλοντος είναι γνωστό ως αποσυμφωνία (decoherence) που ουσιαστικά μπορεί να θεωρηθεί σαν το αποτέλεσμα θορύβου του περιβάλλοντος. Το πρόβλημα της αποσυμφωνίας εντείνεται όσο αυξάνεται το πλήθος των gubits της μνήμης του κβαντικού υπολογιστή. Επίσης, οι βασικές μονάδες επεξεργασίας των gubits, γνωστές και ως κβαντικές πύλες (quantum gates), εισάγουν έναν επιπλέον παράγοντα αλλοίωσης της κβαντικής πληροφορίας διότι η λειτουργία τους πολλές φορές προσεγγίζει την ιδανική θεωρητική συμπεριφορά τους με σφάλμα που δεν επιτρέπει την κατασκευή κβαντικών υπολογιστών μεγάλου πλήθους qubits. Το σφάλμα αυτό μπορεί να θεωρηθεί επιπλέον θόρυβος που εισάγεται από το περιβάλλον και μετατρέπει τις ιδανικές πύλες σε «θορυβώδεις». Έτσι, παρ' όλο που από τα τέλη της δεκαετίας του 1990 μέχρι και σήμερα έχουν επιδειχθεί πραγματικοί κβαντικοί υπολογιστές χρησιμοποιώντας διάφορες τεχνολογίες (φωτόνια, παγίδες ιόντων, επαφές Josephson κ.α.), αυτοί περιορίζονται σε περίπου 10 qubits [15, 16, 17, 18].

Το πρόβλημα της αποσυμφωνίας έχει αντιμετωπιστεί θεωρητικά από την δεκαετία του 1990 εφαρμόζοντας και επεκτείνοντας ιδέες από την κλασική Θεωρία Κωδίκων Διόρθω-

<sup>&</sup>lt;sup>1</sup>Τα πιο ελπιδοφόρα από αυτά είναι οι παγίδες ιόντων (ion traps) [13] και οι μικροσκοπικοί υπεραγωγοί Josephson [14]

σης Σφαλμάτων και αποτέλεσμα την επινόηση Κβαντικών Κωδίκων Διόρθωσης Σφαλμάτων [19, 20, 21]. Τέτοιοι κώδικες μπορούν να χρησιμοποιηθούν έτσι ώστε να συνδυαστούν πολλές «θορυβώδεις» φυσικές κβαντικές πύλες για να συνθέσουν μία ιδανική κβαντική λογική πύλη, δηλαδή να επιτρέψουν τη δημιουργία κβαντικών πυλών ανθεκτικών σε σφάλματα (fault tolerant gates). Αυτό μπορεί να γίνει κάτω από κάποιες προϋποθέσεις, σημαντικότερη από τις οποίες είναι ότι το ποσοστό του θορύβου που εισάγει η λειτουργία της κάθε φυσικής πύλης πρέπει να είναι κάτω από ένα κατώφλι (Κβαντικό Θεώρημα Κατωφλίου – Quantum Threshold Theorem) [22]. Σε μία τέτοια περίπτωση με τη χρήση πλεονασμού χώρου (spatial redundancy), δηλαδή με χρήση πολλών φυσικών κβαντικών πυλών, μπορεί να κατασκευαστεί μία ιδανική λογική κβαντικών πυλών υψηλής αξιοπιστίας, τέτοιας που να επιτρέψει την κατασκευή κβαντικών υπολογιστών ικανοποιητικού μεγέθους στο κοντινό μέλλον. Τα αποτελέσματα αυτών των προσπαθειών είναι πολύ ενθαρρυντικά.

Η διδακτορική συνεισφέρει σε δύο σημαντικά θέματα της Κβαντικής Υπολογιστικής:

- Σχεδίαση καινοτόμων και αποδοτικών κβαντικών κυκλωμάτων (συστοιχίες διασυνδεδεμένων κβαντικών λογικών πυλών), για βασικές αριθμητικές πράξεις ακεραίων καθώς και τον συνδυασμό τους σε υψηλότερο επίπεδο ιεραρχίας για την υλοποίηση κυκλωμάτων πιο σύνθετων αριθμητικών πράξεων. Η καινοτομία των κυκλωμάτων που προτάθηκαν έγκειται στην επεξεργασία των ακεραίων αφού έχει προηγηθεί κατάλληλος κβαντικός μετασχηματισμός Fourier (QFT), επιτυγχάνοντας έτσι βελτιωμένη απόδοση σε όρους ταχύτητας (ή ισοδύναμα βάθους του κυκλώματος). Προβλήματα που σχετίζονται με τη χρήση του QFT σε αριθμητικά κυκλώματα όπως η απαίτηση για πύλες υψηλής ακρίβειας και η έλλειψη τοπικότητας στις επικοινωνίες μεταξύ των qubits, επίσης αντιμετωπίζονται αποτελεσματικά με τις μεθόδους που προτάθηκαν στα πλαίσια της διατριβής.

- Πλήρης και αποδοτική μεθοδολογία ιεραρχικής σύνθεσης κβαντικών και αντιστρέψιμων αρχιτεκτονικών. Η πλειονότητα των μεθόδων αυτοματοποιημένης σύνθεσης είναι επίπεδες, δηλαδή λειτουργούν στο χαμηλότερο επίπεδο των λογικών πυλών και έχουν το μειονέκτημα ότι δεν είναι κατάλληλες για μεγάλα κυκλώματα αφού έχουν εκθετικές απαιτήσεις μνήμης και χρόνου εκτέλεσης της σύνθεσης. Η ενσωμάτωση ιεραρχικής σύνθεσης σε εργαλεία που χρησιμοποιούν επίπεδες μεθόδους σύνθεσης χρησιμοποιεί τη συνήθη μεθοδολογία του Bennett. Η μέθοδος του Bennett εφαρμόζει διαδοχικά κανονικούς υπολογισμούς, αντιγραφή των επιθυμητών αποτελεσμάτων σε ξεχωριστούς καταχωρητές και κατόπιν αντίστροφους υπολογισμούς που επαναφέρουν όλους τους καταχωρητές, εκτός από αυτούς της αντιγραφής, στις αρχικές τους καταστάσεις. Με αυτόν τον τρόπο τα τυχόν ενδιάμεσα αποτελέσματα έχουν μηδενιστεί με αντιστρέψιμο τρόπο. Η μέθοδος του Bennett επιφέρει επιβάρυνση στην χρησιμοποιούμενη μνήμη και την ταχύτητα του τελικού κυκλώματος. Η προτεινόμενη μέθοδος ιεραρχικής σύνθεσης κβαντικών και αντιστρέψιμων κυκλωμάτων προσφέρει πλεονεκτήματα σε όρους ταχύτητας και απαιτούμενης μνήμης του παραγόμενου κυκλώματος, έναντι αυτών της βιβλιογραφίας που χρησιμοποιούν τη μέθοδο Bennett. Σε κάποιες περιπτώσεις το πλεονέκτημα είναι περίπου μισή μνήμη και διπλάσια ταχύτητα.

Στο πλαίσιο της διατριβής, οι πύλες που χρησιμοποιούνται θεωρούνται αξιόπιστες (λογικό επίπεδο) που έχουν προκύψει από βασικές φυσικές πύλες με χρήση οποιασδήποτε τεχνικής διόρθωσης σφαλμάτων. Επομένως, η διατριβή αφορά το λογικό επίπεδο και όχι το χαμηλότερο φυσικό επίπεδο της κατασκευής των βασικών κβαντικών πυλών σε μία συγκεκριμένη τεχνολογία. Συνεπώς οι μέθοδοι που προτείνονται στη διδακτορική διατριβή μπορούν να εφαρμοστούν σε οποιαδήποτε φυσική τεχνολογία κατασκευής.

Ως βασικό κριτήριο της απόδοσης των μεθόδων που προτάθηκαν στη διδακτορική διατριβή χρησιμοποιείται η ταχύτητα του υπολογισμού, γνωστή και ως βάθος του κυκλώματος (circuit depth), δηλαδή ο αριθμός των βημάτων που απαιτούνται για να ολοκληρωθεί ο κβαντικός υπολογισμός. Αυτό είναι ένα σημαντικό κριτήριο απόδοσης όταν μελλοντικά θα είναι εφικτή η κατασκευή κβαντικών υπολογιστών μεγάλου μεγέθους σε όρους μνήμης. Στην περίπτωση της προτεινόμενης μεθόδου ιεραρχικής σύνθεσης πλεονεκτήματα σε όρους μνήμης, εκτός της ταχύτητας, επίσης επιτυγχάνονται.

Τα προτεινόμενα κβαντικά υποσυστήματα αφορούν βασικές αριθμητικές πράξεις ακεραίων, όπως πολλαπλασιασμό σταθεράς με ακέραιο και συσσώρευση (multiply-and-accumulate – MAC) και διαίρεση ακεραίου με σταθερά (εύρεση πηλίκου και υπολοίπου) που χρησιμοποιούνται σε σημαντικούς κβαντικούς αλγορίθμους. Η υλοποίηση επιτυγχάνεται χρησιμοποιώντας εναλλακτικές αναπαραστάσεις των ακεραίων στο πεδίο Fourier (δηλαδή με χρήση του Κβαντικού μετασχηματισμού Fourier – QFT), αντί της συνήθους αναπαράστασης στην υπολογιστική βάση. Κβαντικά κυκλώματα που χρησιμοποιούν μετασχηματισμό Fourier είναι γνωστά στη βιβλιογραφία, αλλά περιορίζονται μόνο σε αθροιστές διαφόρων τύπων [23], ενώ η προφανής υλοποίηση ενός MAC με αναπαράσταση Fourier χρησιμοποιώντας τέτοιους αθροιστές [24] είχε τετραγωνικό βάθος ως προς το μέγεθος των ακεραίων. Αντίθετα, ο προτεινόμενος ΜΑC έχει μόνο γραμμικό βάθος, ιδιαίτερα σημαντική ιδιότητα για μεγάλους (άρα και πρακτικά χρήσιμους) κβαντικούς αριθμούς. Ως προς τα κυκλώματα διαίρεσης, ελάχιστοι διαιρέτες εμφανίζονται στη βιβλιογραφία και κυρίως είναι περιορισμένοι για ειδικές περιπτώσεις (π.χ. για σώματα Galois  $GF(2^m)$ , δηλαδή διαιρέτες πολυωνύμων με συντελεστές 0 και 1). Ένας διαιρέτης βασισμένος σε μετασχηματισμό Fourier που είναι γνωστός [25], έχει κυβικό βάθος ενώ αν η διαίρεση γίνει με σταθερά τότε το βάθος ελαττώνεται σε τετραγωνικό. Ο προτεινόμενος στην διδακτορική διατριβή διαιρέτης με σταθερά έχει και πάλι μόνο γραμμικό βάθος.

Τα δύο παραπάνω κυκλώματα, κατάλληλα συνδυασμένα, μπορούν να χρησιμοποιηθούν για κατασκευή άλλων πιο σύνθετων κυκλωμάτων χρήσιμων σε διάφορους σημαντικούς κβαντικούς αλγορίθμους. Στην παρούσα διατριβή καταδεικνύεται ότι είναι δυνατή η κατασκευή πολλαπλασιαστή modulo N ο οποίος είναι βασικό συστατικό για την πράξη της ύψωσης σε δύναμη modulo N ή αλλιώς εκθετικοποίησης modulo N (modular exponentiation). Η ύψωση σε δύναμη είναι η πιο χρονοβόρα πράξη σε έναν από τους πιο σημαντικούς κβαντικούς αλγορίθμους, τον αλγόριθμο παραγοντοποίησης του Shor, αλλά και σε αλγορίθμους της ίδιας οικογένειας. Η προτεινόμενη σχεδίαση επιτυγχάνει βάθος  $O(n^2)$  ενώ η πλειοψηφία των κυκλωμάτων της βιβλιογραφίας βρίσκεται στην περιοχή μεταξύ  $O(n^2 \log n)$  και  $O(n^3)$  και συνεπώς η προτεινόμενη σχεδίαση προσφέρει ιδιαίτερα μεγάλα πλεονεκτήματα ταχύτητας για μεγάλους κβαντικούς αριθμούς. Κάποια κυκλώματα τετραγωνικού βάθους ή μικρότερου έχουν το μειονέκτημα είτε της αύξησης της απαιτούμενης μνήμης κατά τάξη μεγέθους, είτε του υπολογισμού κατά προσέγγιση ενώ η σχεδίαση της διατριβή στον μοιολογισμό.

Για την εκτίμηση της αποδοτικότητας ενός κυκλώματος (είτε ως προς το χρόνο είτε ως προς το χώρο) πρέπει να λαμβάνονται υπ' όψιν και τα χαρακτηριστικά της φυσικής υλοποίησής του στο χαμηλότερο επίπεδο. Ένα τέτοιο χαρακτηριστικό είναι η ύπαρξη δυνατότητας για καθολική αλληλεπίδραση μεταξύ των qubits που συμμετέχουν στον υπολογισμό ή αντίθετα ο περιορισμός της αλληλεπίδρασης σε γειτονικά qubits μόνο, για παράδειγμα σε υλοποίηση μονοδιάστατης γραμμικής συστοιχίας qubits όπου το κάθε ένα μπορεί να αλληλεπιδράσει μόνο με τα δύο γειτονικά του (1D-LNN,1D Linear Nearest Neighbourhood). Η προτεινόμενη αρχιτεκτονική για τον αλγόριθμο του Shor, παρ' όλο που εκ πρώτης όψεως φαίνεται να απαιτεί καθολικές επικοινωνίες μεταξύ των qubits, αποδεικνύεται ότι μπορεί να προσαρμοστεί σε φυσικές μηχανές τοπικής αλληλεπίδρασης με σταθερή επιβάρυνση στο βάθος, δηλαδή δεν υπάρχει αύξηση του αρχικά υπολογισμένου τετραγωνικού βάθους. Αντίθετα, οι περισσότερες αρχιτεκτονικές χαμηλού βάθους  $O(n^2 \log n)$  όταν περιοριστούν σε μηχανή που απαιτεί γειτονικές επικοινωνίες αυξάνουν το βάθος (π.χ.  $O(n^3)$  σε 1D-LNN ή  $O(n^2\sqrt{n})$  σε 2D-LNN [26].

Η επεξεργασία στο πεδίο Fourier που εφαρμόζουν τα προτεινόμενα κυκλώματα έχουν σαν αποτέλεσμα τη χρήση ελεγχόμενων κβαντικών πυλών περιστροφής (controlled rotation quantum gates) με συγκεκριμένες γωνίες. Ένα γνωστό μειονέκτημα τέτοιων πυλών είναι ότι δεν ανήκουν στην κατηγορία των πυλών που μπορούν να γίνουν ανθεκτικές στα σφάλματα, εκτός και αν αποδομηθούν σε ακολουθία πυλών που είναι ανθεκτικές σε σφάλματα (π.χ. σε πύλες H, T). Μία τέτοια αποδόμηση όμως θα συνεπαγόταν σημαντική επιβάρυνση στο βάθος του συνολικού κυκλώματος εκθετικοποίησης κατά μία τάξη μεγέθους, δηλαδή από  $O(n^2)$  σε  $O(n^3)$ . Μπορεί όμως, όπως δείχνει η διατριβή, η επιβάρυνση να γίνει πολύ μικρότερη με ένα τελικό βάθος  $O(n^2 \log n)$ , με τη διαφορά όμως ότι οι υπολογισμοί θα γίνονται προσεγγιστικά, αλλά επιτρέποντας στην εφαρμογή (αλγόριθμος του Shor) να λειτουργήσει με ελάχιστη υποβάθμιση ως προς την πιθανότητα επιτυχίας. Έτσι, η προτεινόμενη αρχιτεκτονική είναι μία από τις πιο ανταγωνιστικές ως προς το βάθος, ιδιαίτερα αν εφαρμοστεί σε 1D-LNN φυσικές μηχανές, που είναι και πιο πιθανό να υλοποιηθούν στο μέλλον.

Η σχεδίαση κβαντικών κυκλωμάτων υιοθετεί ιδέες από τη σχεδίαση κλασικών λογικών κυκλωμάτων που μπορούν να συνδυαστούν μεταξύ τους. Μικρά κυκλώματα ή κυκλώματα που έχουν επαναληπτικές μικρές δομές μπορούν να σχεδιαστούν είτε κατά περίπτωση (ad hoc) είτε με συστηματικές μεθόδους σύνθεσης με βάση τις προδιαγραφές λειτουργίας (π.χ. πίνακες αλήθειας). Στην περίπτωση των κβαντικών κυκλωμάτων υπάρχουν ανάλογες μέθοδοι κατασκευής με βάση προδιαγραφές που στη γενική περίπτωση είναι τετραγωνικοί μοναδιαίοι πίνακες [27, 28]. Σε ειδικές περιπτώσεις όπου ένα κβαντικό κύκλωμα περιγράφεται από πίνακα με στοιχεία αποκλειστικά 0 και 1, μπορούν να χρησιμοποιηθούν μέθοδοι σύνθεσης αντιστρέψιμων<sup>2</sup> (reversible) λογικών κυκλωμάτων [30]. Τέτοιες περιπτώσεις κβαντικών κυκλωμάτων συναντώνται όταν το κύκλωμα υπολογίζει μία αριθμητική ή λογική συνάρτηση στην υπολογιστική βάση (π.χ. πρόσθεση).

Σε όλες αυτές τις περιπτώσεις οι μεθοδολογίες αυτές είναι κατάλληλες για μικρά κυκλώματα μόνο, γιατί η υπολογιστική ισχύς και η μνήμη που απαιτείται για την εφαρμογή τους αυξάνεται εκθετικά με το μέγεθος του προβλήματος. Η προφανής λύση είναι η ιεραρχική σχεδίαση που εφαρμόζεται και σε κλασικά κυκλώματα. Στην ιεραρχική σχεδίαση, εφ' όσον η επιθυμητή λειτουργία μπορεί να περιγραφεί σαν συναρμογή απλούστερων λειτουργιών, η σχεδίαση ξεκινάει από το χαμηλότερο επίπεδο και προχωράει προς το υψηλότερο. Η εφαρμογή μίας τέτοιας μεθόδου σε κβαντικά κυκλώματα είναι δυνατή αλλά απαιτεί ιδιαίτερη μεταχείριση των ενδιάμεσων αποτελεσμάτων του υπολογισμού τα οποία δε χρειάζονται στο τέλος. Η ιδιαιτερότητα οφείλεται στο γεγονός του ότι τα ενδιάμεσα αποτελέσματα δεν μπορούν απλώς να αγνοηθούν στο τέλος διότι γενικά βρίσκονται σε κβαντική διεμπλοκή με τα επιθυμητά αποτελέσματα. Αυτό που πρέπει να γίνει είναι να επανέλθουν στην αρχική τους κατάσταση μέσω αντίστροφου υπολογισμού. Η μέθοδος του Bennett [31] είναι μία γνωστή μέθοδος τέτοιου αντίστροφου υπολογισμού που διατηρεί τα επιθυμητά αποτελέσματα μέσω αντιγραφής. Το κύριο χαρακτηριστικό της είναι ότι διπλασιάζει

<sup>&</sup>lt;sup>2</sup>Στα αντιστρέψιμα λογικά κυκλώματα από κάθε πιθανή έξοδο είναι δυνατή η εξαγωγή της αντίστοιχης εισόδου, δηλαδή δεν υπάρχει απώλεια πληροφορίας [29].

τα βήματα υπολογισμού (ευθύς υπολογισμός, αντίστροφος υπολογισμός) και απαιτεί επιπλέον μνήμη, όση απαιτούν τα τελικά αποτελέσματα, λόγω της αντιγραφής.

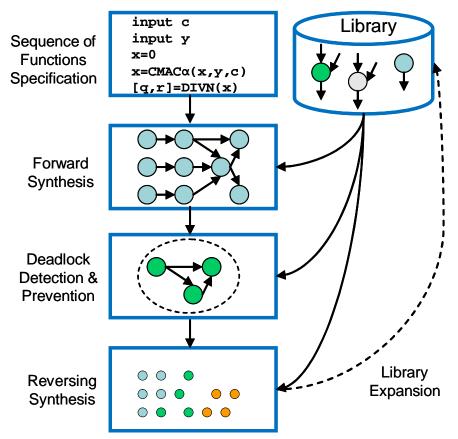

Η μέθοδος ιεραρχικής σχεδίασης που προτάθηκε στη διδακτορική διατριβή προσφέρει πλεονεκτήματα σε σχέση με τη μέθοδο Bennett σε όρους τόσο ταχύτητας όσο και μνήμης του τελικού κυκλώματος. Οι προδιαγραφές του κυκλώματος που πρόκειται να συντεθεί παρέχονται σαν μία ακολουθία συναρτήσεων (αριθμητικών ή λογικών). Οι συναρτήσεις αποτελούν μέρος μία βιβλιοθήκης κβαντικών υπο-κυκλωμάτων. Η βιβλιοθήκη αυτή μπορεί να δημιουργηθεί με χρήση άλλων μεθόδων σύνθεσης χαμηλότερου επίπεδου (πύλης), να περιέχει γνωστά από την βιβλιογραφία παραμετροποιημένα ως προς το μέγεθος κυκλώματα (π.χ. αθροιστές) ή να εμπλουτιστεί με νέα κυκλώματα από την ίδια ιεραρχική μέθοδο. Επίσης, η βιβλιοθήκη περιέχει και τα αντίστροφα κυκλώματα για τις ανάγκες που περιγράφηκαν νωρίτερα. Το τελικό αποτέλεσμα της σύνθεσης σε μορφή κατευθυντικού ακυκλικού γράφου περιγράφει το επιθυμητό κύκλωμα, όπου οι κόμβοι του γράφου αναπαριστούν τα έτοιμα υποκυκλώματα της βιβλιοθήκης και οι ακμές περιγράφουν τις διασυνδέσεις μεταξύ των υποκυκλωμάτων. Η μέθοδος σύνθεσης απαιτεί πολυωνυμικό χρόνο και μνήμη σε σχέση με τον αριθμό των συναρτήσεων που χρησιμοποιούνται και σε κάθε περίπτωση παράγει κυκλώματα καλύτερης ή ίδιας απόδοσης βάθους και μνήμης σε σχέση με τη βασική μέθοδο του Bennett.

Η δομή της διδακτορικής διατριβής είναι η ακόλουθη: Το Κεφάλαιο 2 είναι μία εισαγωγή στην περιοχή της Κβαντικής Υπολογιστικής ενώ το Κεφάλαιο 3 συνοδευόμενο από το Παράρτημα Α είναι η αναλυτική περιγραφή του αλγορίθμου του Shor. Η συνεισφορά της διατριβής ξεκινάει στο Κεφάλαιο 4 όπου περιγράφονται τα γρήγορα κβαντικά αριθμητικά κυκλώματα που βασίζονται σε αναπαράσταση ακεραίων με χρήση του κβαντικού μετασχηματισμού Fourier. Το Κεφάλαιο 5 περιγράφει τη μεθοδολογία προσέγγισης αυτών των κυκλωμάτων με κβάντιση γωνίας καθώς και την προσαρμογή τους σε φυσική μηχανή μονοδιάστατης διάταξης γειτονικών επικοινωνιών. Το Κεφάλαιο 6 περιγράφει την μεθοδολογία προσέγγισης αυτών των κυκλωμάτων και πιθανές μελλοντικές κατευθύνσεις έρευνας στα συγκεκριμένα θέματα της διατριβής.

## TABLE OF CONTENTS

| PF | PREFACE |                                                         | 37 |

|----|---------|---------------------------------------------------------|----|

| 1  | EX      |                                                         | 39 |

| 2  | INT     |                                                         | 43 |

|    | 2.1     | Classical Computing                                     | 43 |

|    |         | 2.1.1 Complexity Classes                                | 43 |

|    |         | 2.1.2 Irreversible and Reversible Computing             | 45 |

|    | 2.2     | Quantum Mechanics and Computation                       | 47 |

|    |         | 2.2.1 State of a closed quantum system                  | 48 |

|    |         | 2.2.2 Unitary evolution of a closed quantum system      | 50 |

|    |         | 2.2.3 Projective Measurement                            | 50 |

|    |         | 2.2.4 Composition of closed systems                     | 51 |

|    |         | 2.2.5 Entanglement                                      | 52 |

|    |         | 2.2.6 Quantum Turing Machine                            | 53 |

|    | 2.3     | Quantum Circuit Model and Quantum Gates                 | 53 |

|    |         | 2.3.1 Single Qubit Gates                                | 54 |

|    |         | 2.3.2 Two-Qubit Gates                                   | 55 |

|    |         | 2.3.3 Three-Qubit Gates                                 | 57 |

|    |         | 2.3.4 Measurement                                       | 58 |

|    |         | 2.3.5 Universal Gates and Synthesis of Quantum Circuits | 58 |

|    |         | 2.3.6 Quantum Circuit Characterization                  | 60 |

|    | 2.4     | Quantum Algorithms                                      | 60 |

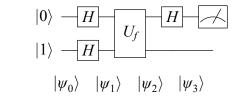

|    |         | 2.4.1 Deutsch's algorithm                               | 60 |

|    |         | 2.4.2 Generalizations - Phase Estimation Algorithms     | 62 |

|    |         | 2.4.3 Other quantum algorithms and applications         | 64 |

|    |         | 2.4.4 Quantum Complexity                                | 67 |

|    | 2.5     | Physical Implementations                                | 68 |

| 3  | SH      | OR'S ALGORITHM                                          | 75 |

|    | 3.1     | Preprocessing: Reduction of Factoring to Period Finding | 75 |

|    | 3.2     | Quantum Fourier Transform                               | 76 |

|    | 3.3     | Discrete Fourier Transform and Periods                  | 77 |

|    | 3.4     | Quantum Period Estimation                               | 82 |

|    | 3.5     | Post-Processing: Retrieval of the exact period          | 85 |

|    | 3.6     | Decomposition of Quantum Modular Exponentiation         | 86 |

|   | 3.7 | Generalizations and the Hidden Subgroup problem                     |

|---|-----|---------------------------------------------------------------------|

| 4 | FAS | ST QUANTUM MODULAR EXPONENTIATION                                   |

|   | 4.1 | Background and related work                                         |

|   |     | 4.1.1 Modulo adder, constant adder and controlled constant adder 90 |

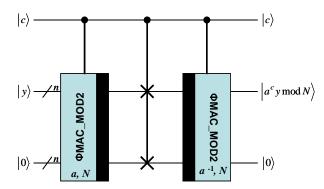

|   |     | 4.1.2 Controlled modulo multiplier                                  |

|   |     | 4.1.3 Prior Work                                                    |

|   |     | 4.1.4 QFT adders                                                    |

|   |     | 4.1.5 Fourier Multiplier/Accumulator - ΦΜΑC                         |

|   | 4.2 | Depth-Optimized Fourier Multiplier/Accumulator - ΦΜΑC               |

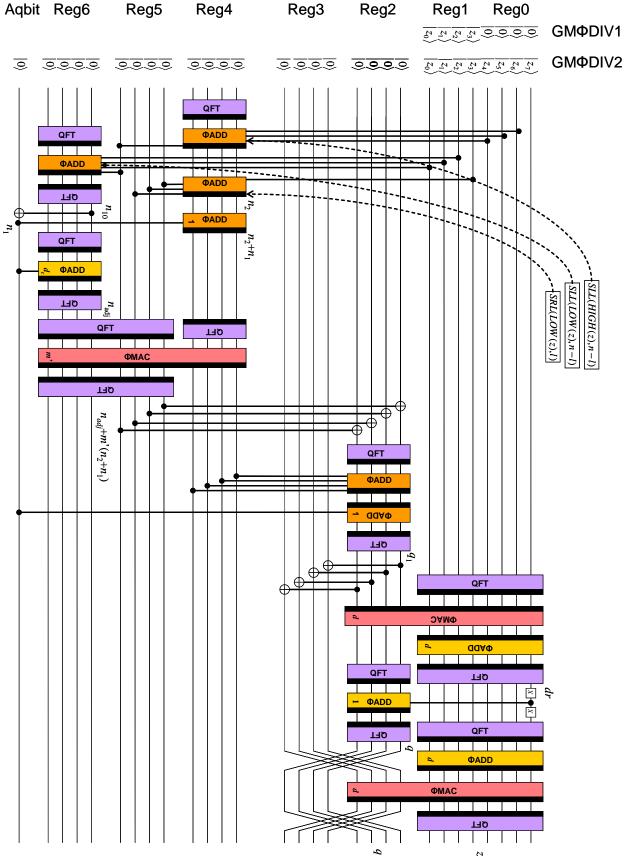

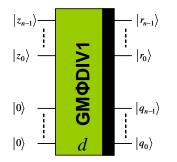

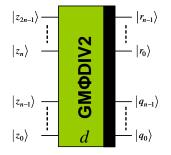

|   | 4.3 | QFT Divider by constant - GMΦDIV                                    |

|   |     | 4.3.1 Building blocks and registers of the quantum divider          |

|   |     | 4.3.2 Forward computations of the quantum divider                   |

|   |     | 4.3.3 Ancilla Resetting                                             |

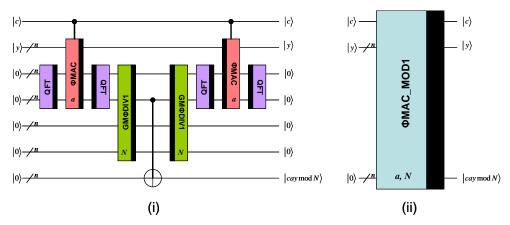

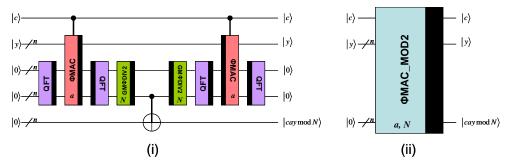

|   | 4.4 | Generic Modular Multipler/Accumulator and Modular Multiplier        |

|   |     | 4.4.1 Generic QFT Modular Multiplier/Accumulator - ΦMAC_MOD1 112    |

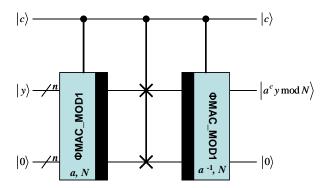

|   |     | 4.4.2 Generic QFT Modular Multiplier - ΦMUL_MOD1                    |

|   | 4.5 | Optimized Modular Multipler/Accumulator and Modular Multiplier      |

|   | 4.6 | Complexity Analysis                                                 |

|   | 4.7 | Divider Improvement and Extension                                   |

| 5 | IMP | LEMENTATION ISSUES OF QFT BASED ARITHMETIC CIRCUITS 125             |

|   | 5.1 | Angle Quantization of Rotation Gates                                |

|   |     | 5.1.1 Definitions and basic properties                              |

|   |     | 5.1.2 Approximation of the multiplier/accumulator ΦMAC              |

|   |     | 5.1.3 Approximation of the Fourier adders and QFT                   |

|   |     | 5.1.4 Approximation of the whole modular exponentiation             |

|   | 5.2 | Communications Localization                                         |

| 6 |     | RARCHICAL SYNTHESIS OF QUANTUM AND REVERSIBLE ARCHITEC-             |

|   |     | RES                                                                 |

|   |     | Background and related work                                         |

|   | 6.2 | Methodology Basics                                                  |

|   |     | 6.2.1 Initial Specifications and Library                            |

|   | • - | 6.2.2 Quantum Dependence Graph                                      |

|   | 6.3 | Forward QDG Synthesis                                               |

|   |     | 6.3.1 Representation of Classical Algorithm                         |

|    |      | 6.3.2 Forward Synthesis Algorithm             |

|----|------|-----------------------------------------------|

|    | 6.4  | Reversible QDG Synthesis                      |

|    |      | 6.4.1 Node Inversion                          |

|    |      | 6.4.2 Global Considerations                   |

|    |      | 6.4.3 Deadlocks Resolution                    |

|    |      | 6.4.4 Reversing Algorithm                     |

|    | 6.5  | Synthesis Examples                            |

|    | 6.6  | Features and Comparison                       |

|    | 6.7  | Conclusions                                   |

| 7  | со   | NCLUSIONS AND FUTURE WORK                     |

|    | 7.1  | QFT based arithmetic circuits                 |

|    | 7.2  | Hierarchical Synthesis                        |

|    | 7.3  | Future Directions                             |

| A  | AP   | PENDIX ON SHOR'S ALGORITHM                    |

|    | A.1  | Factorization reduction to order finding      |

|    | A.2  | Continued Fraction Expansion                  |

|    | A.3  | Success Probability of Quantum Period Finding |

|    | A.4  | Quantum Fourier Transform Circuit             |

|    | A.5  | Quantum Phase Estimation                      |

| RI | EFEI | RENCES                                        |

# LIST OF FIGURES

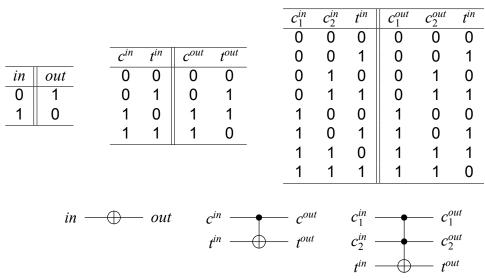

| 2.1  | Symbols for NOT, CNOT and Toffoli reversible gates                                                                                                                                                                                                                                                                                          | 46 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

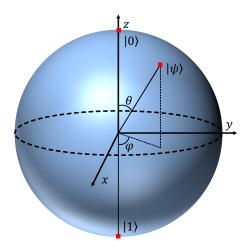

| 2.2  | Representation of a qubit on the Bloch sphere                                                                                                                                                                                                                                                                                               | 49 |

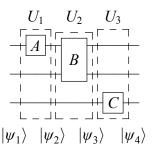

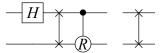

| 2.3  | An example of quantum circuit model                                                                                                                                                                                                                                                                                                         | 54 |

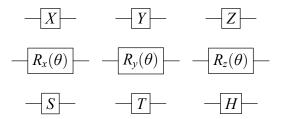

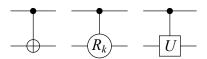

| 2.4  | Symbols for various single qubit gates                                                                                                                                                                                                                                                                                                      | 54 |

| 2.5  | Symbols for CNOT gate, controlled rotation gate and general controlled gate.                                                                                                                                                                                                                                                                | 56 |

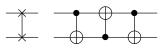

| 2.6  | SWAP gate and an implementation using three CNOT gates                                                                                                                                                                                                                                                                                      | 56 |

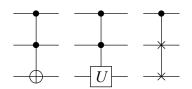

| 2.7  | Symbols for Toffoli gate, general $c^2$ - $U$ gate and Fredkin (controlled SWAP) gate                                                                                                                                                                                                                                                       | 57 |

| 2.8  | Symbol for the computational basis measurement gate.                                                                                                                                                                                                                                                                                        | 58 |

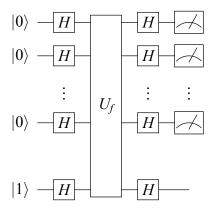

| 2.9  | Quantum circuit for Deutsch's algorithm                                                                                                                                                                                                                                                                                                     | 61 |

| 2.10 | Quantum circuit for Deutsch-Josza algorithm                                                                                                                                                                                                                                                                                                 | 63 |

| 2.11 | Quantum circuit for Simons's algorithm                                                                                                                                                                                                                                                                                                      | 64 |

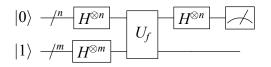

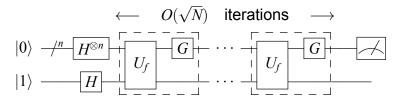

| 2.12 | Quantum circuit for Grover's algorithm. Dashed boxes are the Grover oper-<br>ator while $G$ is the Grover diffusion operator.                                                                                                                                                                                                               | 65 |

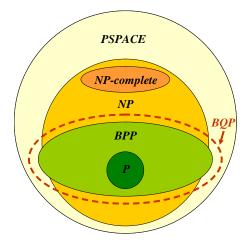

| 2.13 | The suspected relations among various classical complexity classes and BQP                                                                                                                                                                                                                                                                  | 67 |

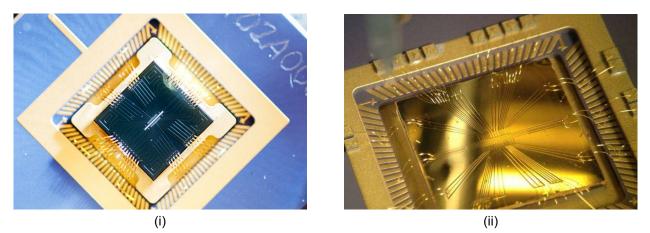

| 2.14 | Ions Trap microfabricated chips: (i) Sandia National Laboratories. [89], (ii) Department of Physics, Oxford University. [90]                                                                                                                                                                                                                | 71 |

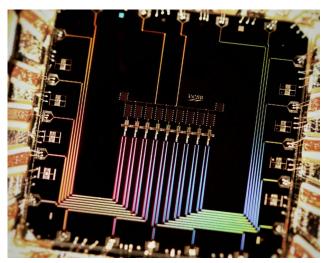

| 2.15 | Nine superconducting qubits integrated circuit fabricated at University of California - Santa Barbara [100].                                                                                                                                                                                                                                | 72 |

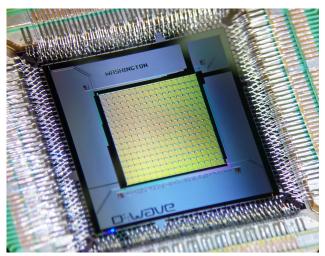

| 2.16 | D-Wave Systems 1000 qubits quantum annealing processor                                                                                                                                                                                                                                                                                      | 74 |

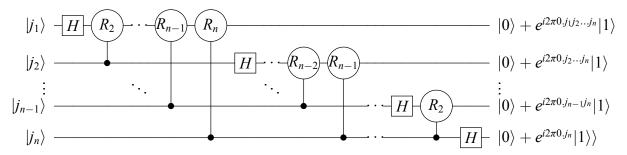

| 3.1  | Quantum Fourier Transform circuit on <i>n</i> qubits. The normalization factor $\frac{1}{\sqrt{2}}$ is not shown at the output states. The order of the qubits must be reversed at the end                                                                                                                                                  | 77 |

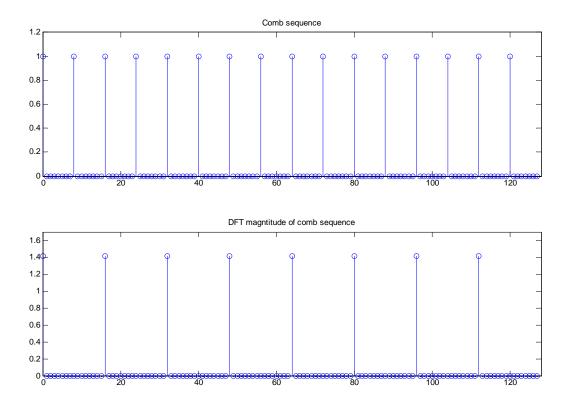

| 3.2  | Comb sequence of length $L = 128$ and period $r = 8$ (top), magnitude of the corresponding DFT (bottom).                                                                                                                                                                                                                                    | 78 |

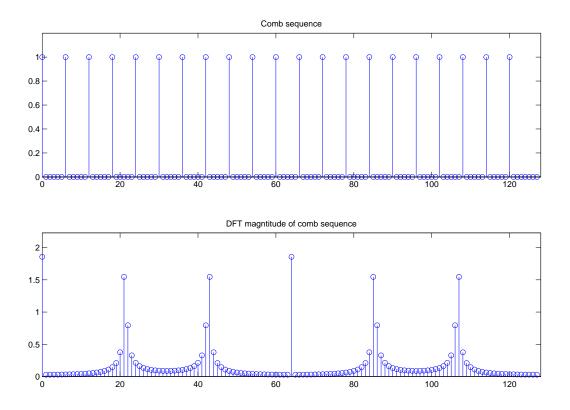

| 3.3  | Comb sequence of length $L = 128$ and period $r = 6$ (top), DFT of magnitude sequence (bottom).                                                                                                                                                                                                                                             | 80 |

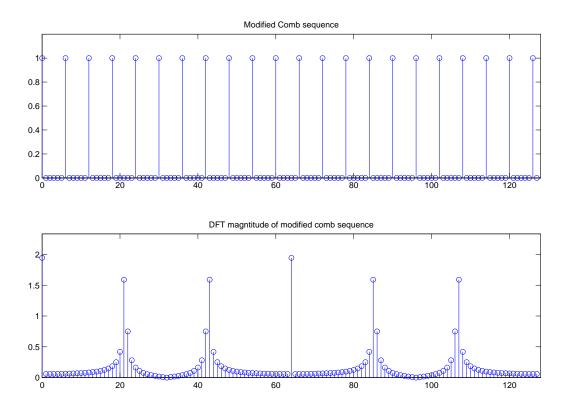

| 3.4  | Modified Comb sequence of length $L = 128$ and period $r = 6$ (top), DFT of magnitude sequence (bottom).                                                                                                                                                                                                                                    | 81 |

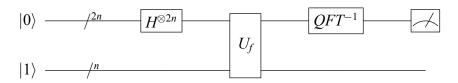

| 3.5  | Quantum circuit for period finding algorithm                                                                                                                                                                                                                                                                                                | 82 |

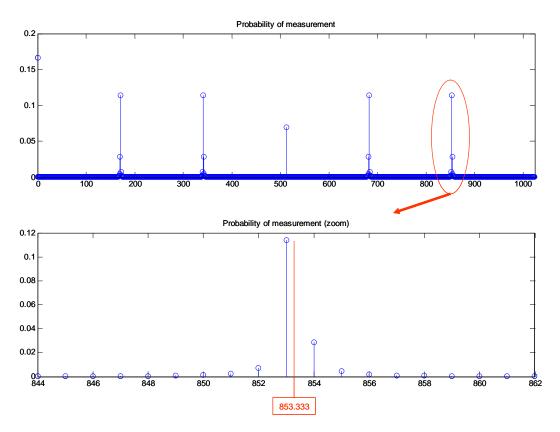

| 3.6  | Measurement probabilities of period finding algorithm for $L = 1024$ and period $r = 6$ (top), zoom in the range $k = 844 \dots 862$ (bottom).                                                                                                                                                                                              | 84 |

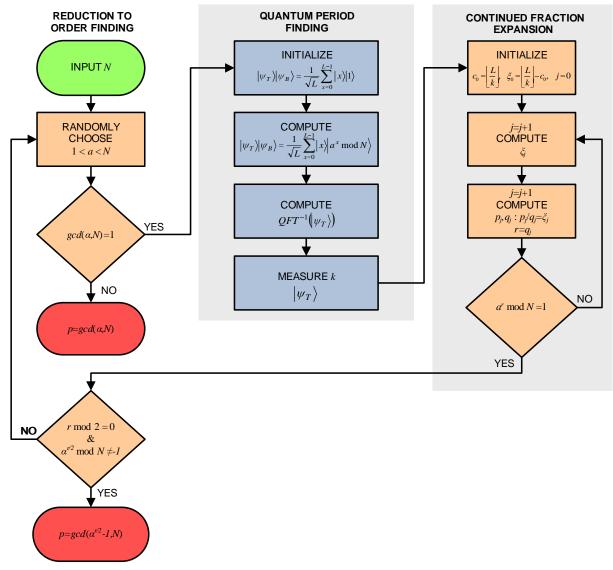

| 3.7  | Shor's integer factoring algorithm flowchart. The algorithm is divided into the three grayed shades submodules; the probabilistic reduction of the factoring problem to period finding, the quantum computation for the period finding and the exact extraction of the period using the continued fraction expansion method (Appendix A.2). | 85 |

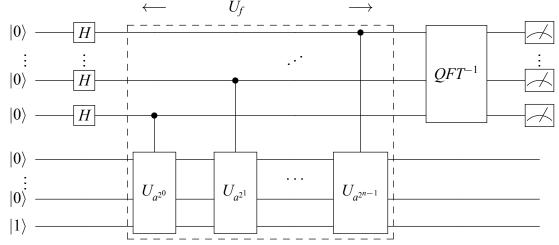

| 3.8  | Decomposition of the quantum modular exponentiation into quantum mod-<br>ular multiplication in Shor's algorithm.                                                                                                                                                                                                                                                          | 87  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

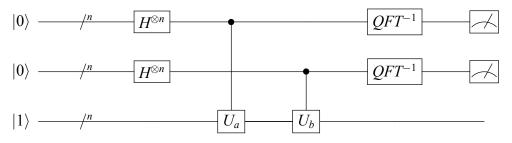

| 3.9  | Quantum circuit of the discrete logarithm algorithm                                                                                                                                                                                                                                                                                                                        | 88  |

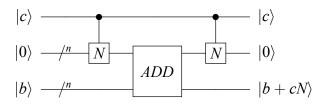

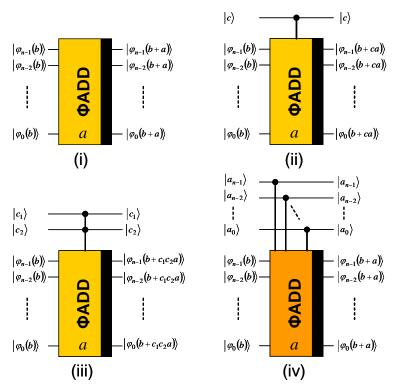

| 4.1  | Quantum circuit for controlled constant addition.                                                                                                                                                                                                                                                                                                                          | 91  |

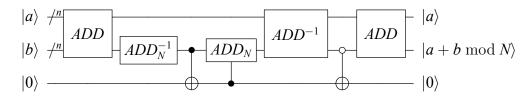

| 4.2  | Quantum circuit for modular addition. The white circle of the second CNOT gate denotes inversion of its target qubit iff the control qubit is $ 0\rangle$ . Control qubits of both CNOT gates emerge from the most significant qubit of the register on which they are attached. Ancilla qubits of the various adders used in this figure are hidden inside their symbols. | 91  |

| 4.3  | Quantum circuit for controlled accumulation of modular multiplication. An-<br>cilla qubits of the modular adders used in this figure are hidden inside their<br>symbols.                                                                                                                                                                                                   | 92  |

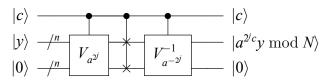

| 4.4  | Quantum circuit for controlled modular multiplication. Ancilla qubits are not shown in the symbols of the two blocks.                                                                                                                                                                                                                                                      | 93  |

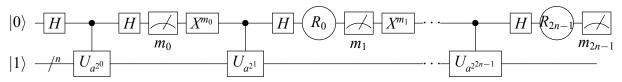

| 4.5  | Design of modular exponentiation circuit using only one qubit to control the modular multipliers. The phase shift gates $R$ depend on all previous measurement results and implement the inverse QFT, while the $X$ gates are negations conditioned on the result of the previous measurement.                                                                             | 93  |

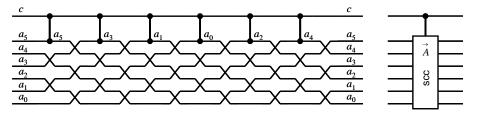

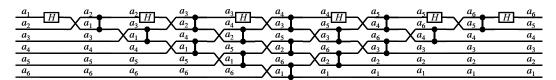

| 4.6  | $\Phi$ ADD adder circuit of depth 1. This circuit adds a constant integer <i>a</i> to the quantum integer <i>b</i> , when <i>b</i> is already in the Fourier domain. The value of integer <i>a</i> is hardwired in the angles of the phase shift gates $A_j$ , $j = 0 \dots n-1$ as defined in Eq. (4.10)                                                                  | 95  |

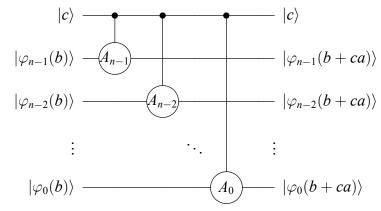

| 4.7  | C $\Phi$ ADD controlled adder circuit of depth <i>n</i> . This circuit adds the constant <i>a</i> to the quantum integer <i>b</i> when the control qubit $ c\rangle$ is $ 1\rangle$ . Again, the constant value <i>a</i> is hardwired in the controlled rotation gates as defined in Eq. (4.10).                                                                           | 95  |

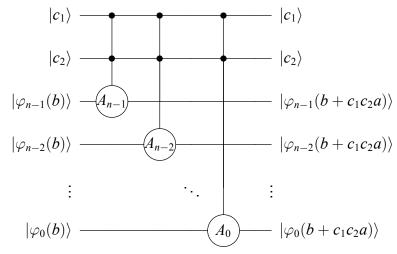

| 4.8  | The doubly-controlled adder circuit CC $\Phi$ ADD of depth <i>n</i> . This is an extension of the C $\Phi$ ADD circuit where the addition is performed when both the control qubits $ c_1\rangle$ and $ c_2\rangle$ are $ 1\rangle$ .                                                                                                                                      | 96  |

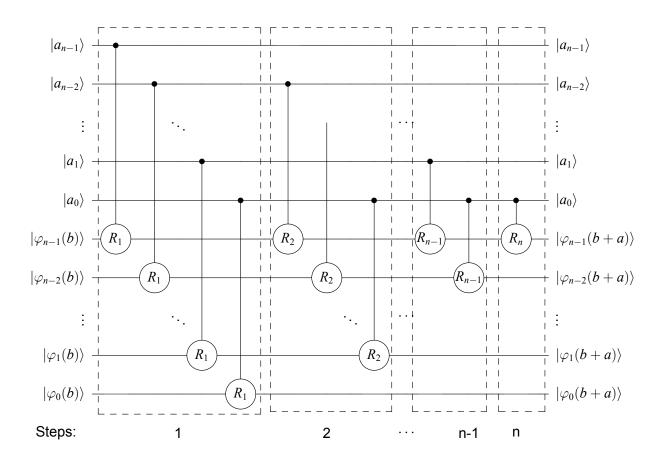

| 4.9  | Generic adder $\Phi$ ADD circuit and its symbol. The top bus consists of the qubits $ a_0\rangle, \ldots,  a_{n-1}\rangle$ that control the rotation gates.                                                                                                                                                                                                                | 96  |

| 4.10 | Symbols for the four introduced QFT adders. (i) Adder with constant $a$ , (ii) controlled adder with constant $a$ , (iii) doubly controlled adder with constant $a$ and (iv) adder of two quantum integers $a$ and $b$ .                                                                                                                                                   | 97  |

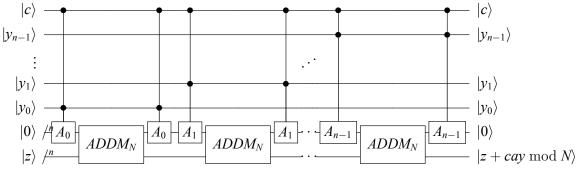

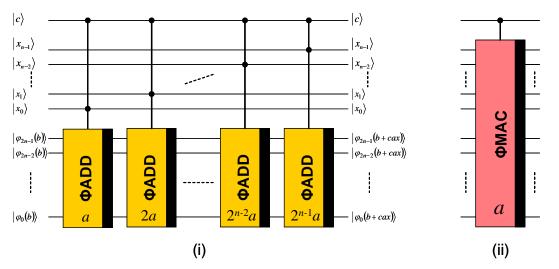

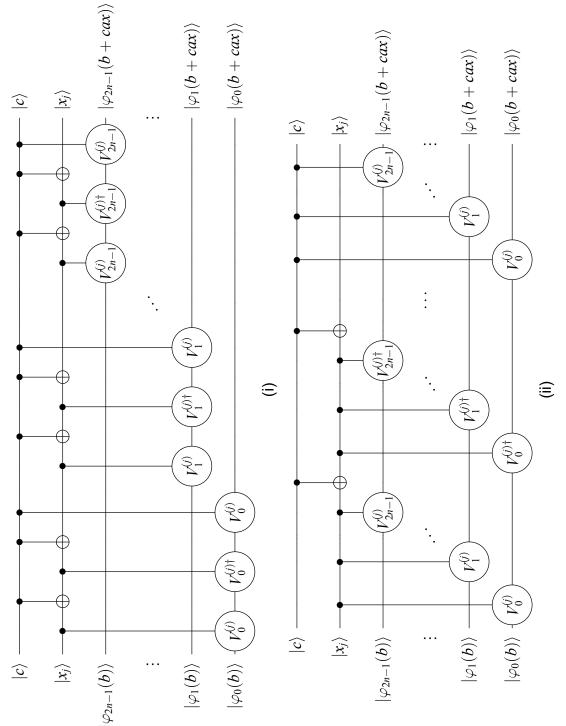

| 4.11 | Block level design of the multiplier/accumulator unit $\Phi$ MAC and its symbol.<br>The basic blocks depicted here are the CC $\Phi$ ADD units of Figure 4.8. A detailed diagram of the above circuit is provided in Figure 4.12.                                                                                                                                          | 98  |

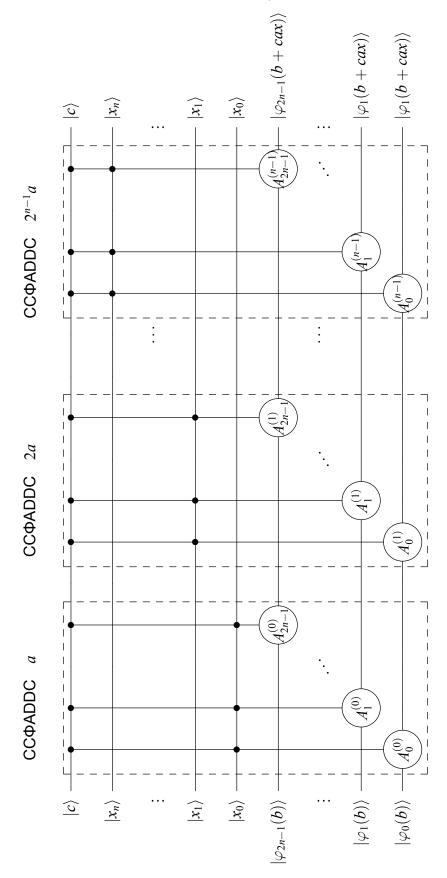

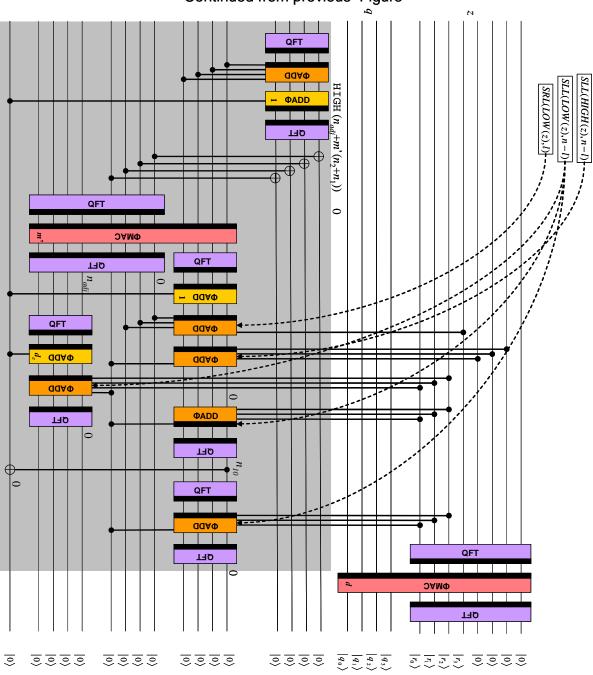

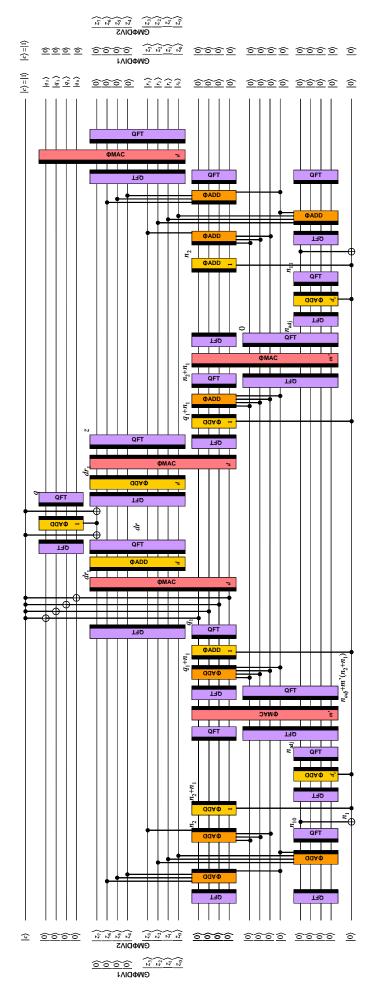

| 4.12 | Detailed design of the initial multiplier/accumulator $\Phi$ MAC unit which has a depth of $2n^2$ . The depth improvement of this circuit is described in Section 4.2 and the improved $\Phi$ MAC is depicted in Figure 4.15.                                                                                                                                              | 99  |

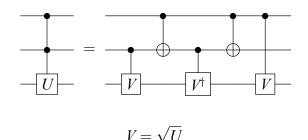

| 4.13 | Doubly controlled three-qubit gate decomposition to a network of two-qubit gates.                                                                                                                                                                                                                                                                                          | 101 |

| 4.14 | (i) The $j^{th}$ $\Phi$ ADD subcircuit of the $\Phi$ MAC, (ii) the rearrangement of the $j^{th}$ $\Phi$ ADD subcircuit after exploiting the decomposition of Figure 4.13.                                                                                                                                                                                                  | 102 |

|      |                                                                                                                                                                                                                                                                                                                                                                            |     |

| 103   |

|-------|

| 109   |

| 110   |

| 111   |

| 113   |

| 114   |

| 115   |

| 115   |

| 116   |

| 123   |

| . 124 |

| 127   |

| 128   |

| /.129 |

| 133   |

| 133   |

|       |

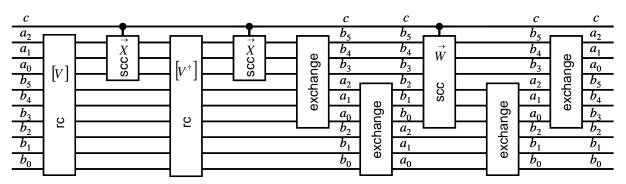

| 5.6  | Shifted control circuit "sc". Two-qubits gates (denoted with vertical lines with dots at their ends) are applied consecutively between qubit $c$ and $a_j$ 134                                                                                                                                                                                                                                                                                                                                                         |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.7  | Shifted control circuit "scc" for commuting gates. The gates applied between qubit $c$ and $a_j$ mutually commute                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.8  | Rotating pattern control circuit "rc" using local interactions                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

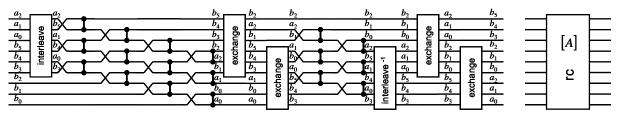

| 5.9  | ΦMAC circuit using local communications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

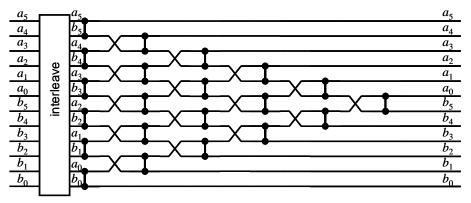

| 5.10 | ΦADD on two 6 qubits integers using local communications                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.11 | QFT on 6 qubits using local communications                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

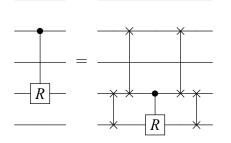

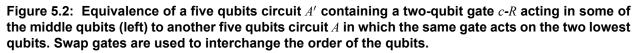

| 5.12 | These two circuits have almost equal depth                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6.1  | High level description of the proposed synthesis methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

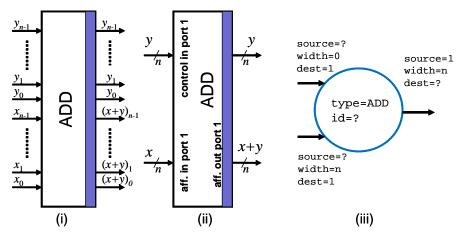

| 6.2  | Representation of a quantum functional block in the QDG notation. (i) Func-<br>tional block showing all the qubits taking part in the operation along with<br>their input and output states, (ii) the same block with the qubits organized in<br>buses connected to ports, and (iii) the abstract notation of the same block<br>as a node with arcs and their labels. The question marks mean that the re-<br>spective label depends on the specific connections of the node relative to<br>the other nodes of the QDG |

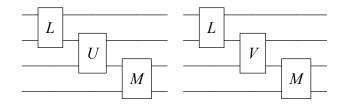

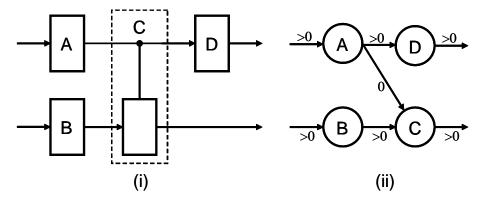

| 6.3  | Mapping between the standard notation (i) and the QDG notation (ii). Af-<br>fected arcs have width >0, while control arcs have width=0                                                                                                                                                                                                                                                                                                                                                                                 |

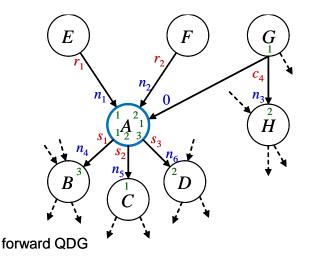

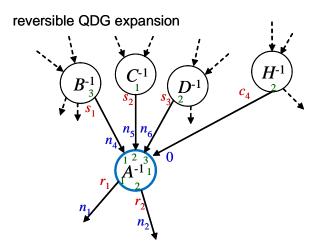

| 6.4  | Part of an example forward QDG node. Attached at the tail of the solid arcs is the output state and at the head of the arcs is the width of the arc (0 for control arc). Inside the circles of the nodes the port numbers for each case of affected input, affected output and control input arcs are shown 146                                                                                                                                                                                                        |

| 6.5  | Inversion of node A of the example forward QDG shown in Fig. 6.4. Legend of arc and node labels is similar as that of Fig. 6.4                                                                                                                                                                                                                                                                                                                                                                                         |

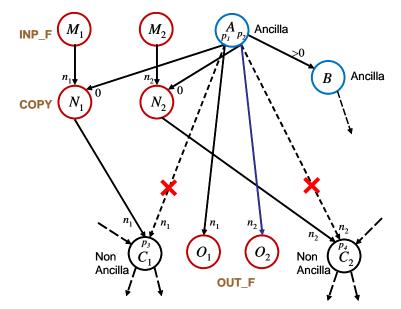

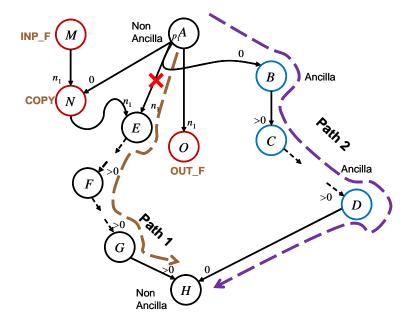

| 6.6  | First type of deadlock resolution. Nodes <i>A</i> and <i>B</i> are ancilla, nodes $C_1$ and $C_1$ are non-ancilla and $M_1, M_2, N_1, N_2, O_1, O_2$ are the nodes added to prevent the deadlock. Next to each arc is shown its width. Ports are shown inside the circles of some nodes                                                                                                                                                                                                                                |

| 6.7  | Second type of deadlock. Nodes $A, E, F, G, H$ are non-ancilla whereas nodes $B, C, D$ are ancilla. Nodes $M, N, O$ added to prevent the deadlock. Width of each arc is shown                                                                                                                                                                                                                                                                                                                                          |

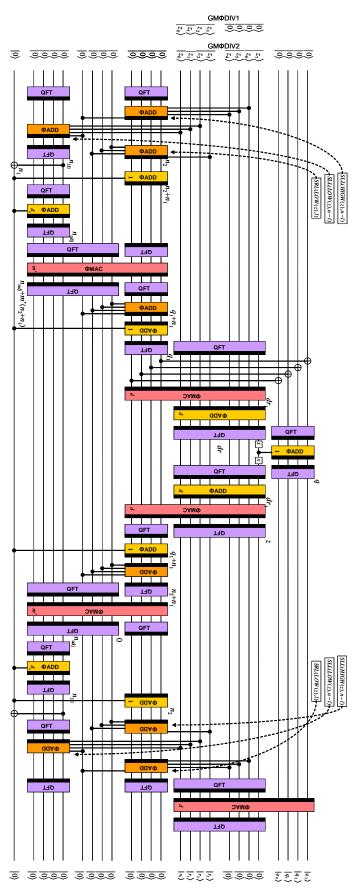

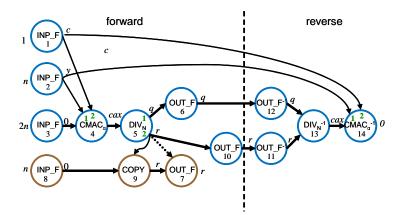

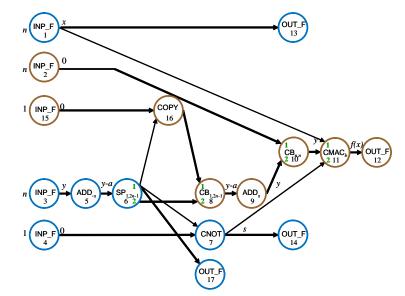

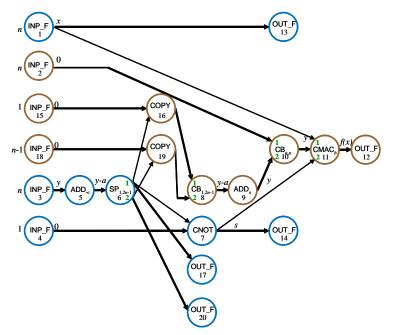

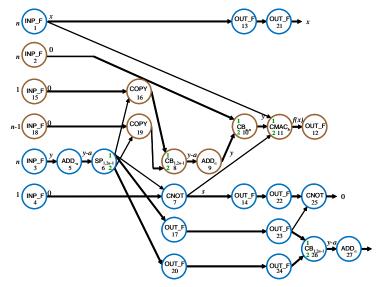

| 6.8  | Quantum or reversible architecture result in the form of QDG (forward and reverse) for the controlled modular multiplier. Inside each node the function type and the id are shown. Next to each arc the state it carries is shown. Thick and thin arcs are affected and control arcs, respectively. Ports numbering is shown inside the node, when necessary                                                                                                                                                           |

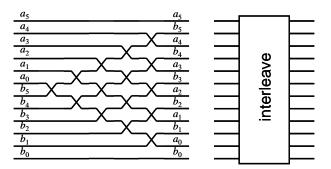

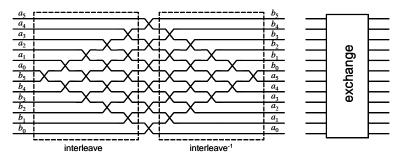

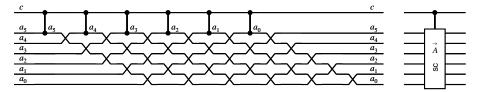

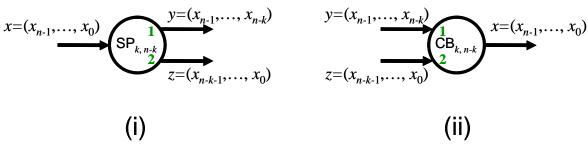

| 6.9  | Splitter (i) and Combiner (ii) blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

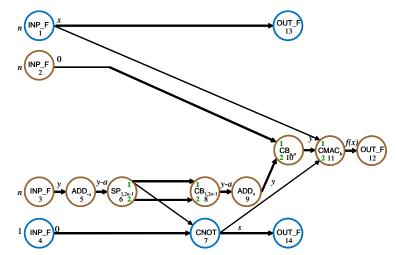

| 6.10 | Forward Synthesis result for the conditional mutiliply/accumulate example. 157                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.11 | Deadlock II resolution for the conditional mutitiply/accumulate example 157                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.12 | Deadlock I resolution for the conditional mutitiply/accumulate example 158                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6.13 | Complete synthesis of the conditional mutitiply/accumulate example after the final reversion procedure.                                                                                                                                                                                                        | 158 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

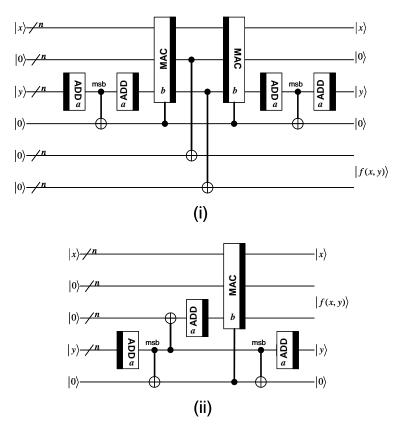

| 6.14 | Comparison of two circuits computing the conditional multiply/accumulate example. (i) Circuit derived by the compute-copy-uncompute method and (ii) circuit derived by the proposed method.                                                                                                                    | 159 |

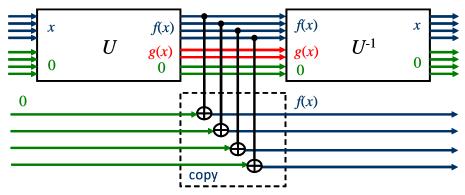

| 6.15 | Input and output wires definitions of a reversible/quantum circuit $U$ (input argument $x$ , ancilla input and output 0, desired output $f(x)$ and garbage output $g(x)$ ) and garbage elimination (except the input argument) using Bennett's trick of copying the output and applying the inverse $U^{-1}$ . | 161 |

## LIST OF TABLES

| 2.1 | Truth tables for NOT, Controlled-NOT and Toffoli reversible gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Embedding of the irreversible AND function into a reversible function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 47  |

| 3.1 | Probabilistic algorithm to factorize an odd, non prime power integer, $N$ by finding the period of sequence $a^x \mod N$ . The output $p$ is a factor of $N$ . The probability of success can be made arbitrary close to 1 with a constant number of iterations.                                                                                                                                                                                                                                                                                                                                                                            | 75  |

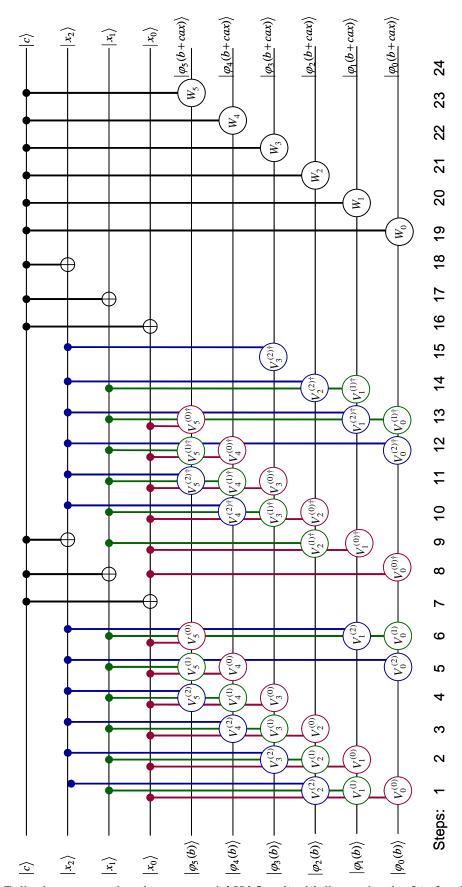

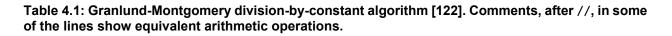

| 4.1 | Granlund-Montgomery division-by-constant algorithm [122]. Comments, after //, in some of the lines show equivalent arithmetic operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 105 |

| 4.2 | Explanation of the various logical operations and data types used in the classical version of the division by constant algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 105 |

| 4.3 | Units used in the $\Phi$ MUL_MOD1 design, depth of each unit, number of gates in each unit, number of units used for each type, gates contribution and depth contribution of each unit type to the total quantum cost and depth of the modular multiplier.                                                                                                                                                                                                                                                                                                                                                                                  | 117 |

| 4.4 | Units used in the $\Phi$ MUL_MOD2 design, depth of each unit, number of gates in each unit, number of units used for each type, gates contribution and depth contribution of each type of unit to the total quantum cost depth                                                                                                                                                                                                                                                                                                                                                                                                              | 117 |

| 4.5 | Comparison of various modular exponentiation quantum circuits in terms of<br>qubits requirement (width), speed (depth), number of gates used (quantum<br>cost) and depth-width product. Second column succinctly describes the ar-<br>chitecture and the basic block used (usually the kind of adder), third column<br>shows the interactions requirement and the fourth column distinguishes be-<br>tween exact or approximate calculations performed. For the depth and gates<br>estimations we have assumed that whenever Toffoli gates are used, they<br>contribute five times the quantum cost and depth of two or single qubit gates. | 119 |

| 6.1 | Example functions of a Quantum Library.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 141 |

| 6.2 | Forward QDG Synthesis Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 145 |

| 6.3 | Node Inversion Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 148 |

| 6.4 | Detection and Resolution of Deadlock I Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 150 |

| 6.5 | Detection of Deadlock II Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 152 |

| 6.6 | Reversing Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 153 |

| 6.7 | Specifications of a controlled modular multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 154 |

| 6.8 | Specifications of a conditional multiplier/accumulator. Bit widths of the variables $x, z, y, s$ are $n, n, n, 1$ respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 156 |

# PREFACE

This thesis was conducted in the Department of Informatics and Telecommunications of the National and Kapodistrian University of Athens during the period 2011-2016.

# **1. EXTENDED SUMMARY**

Quantum Information Theory and Quantum Computing are interdisciplinary research fields that combine different doses of Physics, Informatics and Mathematics depending on which aspect someone focuses. Quantum Computing is a relatively recent research field, al-though Quantum Information Theory has already been developed for the last 40 years, after important results which connect classical Information Theory to Quantum Mechanics (quantum entropies inequalities [1, 2, 3], Holevo bounds for capacities of quantum channels [4, 5], Bekenstein bound [6], etc.)

The theoretical connection of Quantum Mechanics to the Theory of Computation achieved in the 80's [7, 8], while more boost came in the 90's with the invention of efficient quantum algorithms [9, 10, 11], which can be executed on computing machines (quantum computers) exploiting fundamental quantum properties of nature, like superposition and entanglement. Such efficient algorithms can achieve important reduction of time complexity, so that in many instances, problems that cannot be solved in polynomial time on a classical computer with the currently known algorithms, can be solved in polynomial time on a quantum computer. A famous example, with important applications in Cryptography, is the factorization of a composite integer into its prime factors (Shor's algorithm)[10]. Another important example is the efficient simulation of quantum physical systems with many degrees of freedom (like a complex chemical molecule), a computation which is not practically achievable in a classical computer [12].

The physical realization of a quantum computer, while in principle is feasible, requires a complex technological effort to overcome practical problems. An important problem is that the carriers of quantum information, the gubits, are very fragile under the influence of their environment and it is very difficult to maintain them in a constant state for a long enough duration so as they can perform a useful computation. The physical carriers of information can be atoms, ions, nuclei and in general any microscopic system on which guantum mechanical effects can be observed<sup>1</sup>. The disturbance effect on the qubits under the environment influence is known as decoherence and can be thought as an environment noise effect. Decoherence problems increase as the number of gubits increases. Additionally, the basic processing elements of gubits, the guantum gates, introduce another factor of disturbance of quantum information, because usually their operation approximates the ideal theoretical operation with errors which don't allow the construction of useful large guantum computers. These introduced errors can be thought as an additional environment induced noise, converting the ideal gates to noisy or erroneous ones. Thus, although real quantum computers have been already developed using various technologies (photons, ion traps, Josephson junctions), they are limited to about 10 qubits [15, 16, 17, 18].

The decoherence problem has been theoretically addressed in the 90's by exploiting and extending results from classical Error Correcting Codes Theory, leading to the invention of Quantum Error Correcting Codes [19, 20, 21]. Such codes can be applied by combining many noisy quantum physical gates so as to build an ideal quantum logical gate, that is they allow the construction of fault tolerant quantum gates. This can be accomplished under some conditions, of which the most important is that the noise percentage introduced by each physical quantum gate is lower than a threshold (Quantum Threshold Theorem) [22]. In such a case, an ideal quantum logical gate can be constructed by using redundancy, that is using many physical gates. During the recent years, the effort to build high reliability quantum gates has been intensified, so as to permit the construction of quantum computers of adequate size in the near future. Results of these efforts are very encourag-

<sup>&</sup>lt;sup>1</sup>Currently, some of the most promising are ion traps [13] and Josepshon junction superconductors [14]

ing.

This thesis contributes two-fold:

- Design of novel efficient quantum circuits (arrays of interconnected quantum logical gates) for integer arithmetic operations and their combination to a higher hierarchy level to achieve more complex arithmetic operations, like modular exponentiation which is an integral part of Shor's algorithm and important algorithms of the same class. The novelty of the proposed circuits lays in the usage of Quantum Fourier Transform (QFT) on the integers states prior to their processing, resulting in improved efficiency in terms of speed. Problems related to the usage of QFT in arithmetic circuits, such as the requirement for high precision quantum gates and the lack of communications locality between the qubits, are also effectively addressed.

- A generic hierarchical quantum and reversible circuits synthesis methodology. The majority of existing automatic synthesis methods are flat; they operate on the lowest level of gates and while in many cases they lead to optimal or suboptimal results, they have the disadvantage of not being suitable for large circuits as they have exponential requirements in memory usage and run time. The straightforward incorporation of hierarchical synthesis methods into tools of flat methods uses the methodology of Bennett. In contrast, the proposed hierarchical method offers advantages in terms of derived circuit speed and memory, relative to the few hierarchical ones of the literature.

In the context of this thesis, the used gates are assumed to be reliable (logical level) which have been derived from elementary physical quantum gates incorporating any method of error correction. Thus, the thesis concerns the logical level of quantum gates and not the lower level of physical gates. Therefore, the proposed methods of this doctoral thesis can be applied to any technology of physical realization and fault tolerant implementation of logic gates.