# NATIONAL AND KAPODISTRIAN UNIVERSITY OF ATHENS

### SCHOOL OF SCIENCES DEPARTMENT OF INFORMATICS AND TELECOMMUNICATIONS

**BSc THESIS**

# Educational Simulation Framework for Performance Modeling of RISC Microprocessors

Konstantinos V. Chasialis

Supervisor: Dimitris Gizopoulos, Professor

ATHENS

September 2021

# ΕΘΝΙΚΟ ΚΑΙ ΚΑΠΟΔΙΣΤΡΙΑΚΟ ΠΑΝΕΠΙΣΤΗΜΙΟ ΑΘΗΝΩΝ

### ΣΧΟΛΗ ΘΕΤΙΚΩΝ ΕΠΙΣΤΗΜΩΝ ΤΜΗΜΑ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΤΗΛΕΠΙΚΟΙΝΩΝΙΩΝ

ΠΤΥΧΙΑΚΗ ΕΡΓΑΣΙΑ

# Εκπαιδευτικό Περιβάλλον Προσομοίωσης για τη Μοντελοποίηση Απόδοσης Μικροεπεξεργαστών RISC

Κωνσταντίνος Β. Χασιαλής

Επιβλέπων: Δημήτρης Γκιζόπουλος, Καθηγητής

ΑΘΗΝΑ

Σεπτεμβρίος 2021

## **BSc THESIS**

Educational Simulation Framework for Performance Modeling of RISC Microprocessors

Konstantinos V. Chasialis

**S.N.:** 1115201600195

SUPERVISOR: Dimitris Gizopoulos, Professor

### ΠΤΥΧΙΑΚΗ ΕΡΓΑΣΙΑ

Εκπαιδευτικό Περιβάλλον Προσομοίωσης για τη Μοντελοποίηση Απόδοσης Μικροεπεξεργαστών RISC

Κωνσταντίνος Β. Χασιαλής

**A.M.:** 1115201600195

ΕΠΙΒΛΕΠΩΝ: Δημήτρης Γκιζόπουλος, Καθηγητής

# ABSTRACT

One of the most fundamental topics in the field of Computer Science is how hardware works and how it interacts with software in contemporary computing systems. Unfortunately, this topic is hard to understand because students are not able to visualize/simulate and experiment with what they are taught. For that reason, many programs have been developed and their goal is to visualize what happens in the hardware when a program is being executed. Another equally significant topic is about assembly languages. MIPS as RISC ISA is usually the MIPS assembly language that is taught in universities. The main reason that MIPS is used is that assembly languages are very complex, counter-intuitive and difficult to understand while MIPS is simple enough to understand yet complicated enough to teach all the basic points. Additionally, MIPS processors continue to be used in workstations, embedded systems (e.g. routers, set-top boxes, cable modems etc.) and even supercomputers. In this thesis we turn our attention to a widely used project, QtMips. QtMips is a visual educational simulator that uses MIPS RISC ISA and simulates many hardware components during a program execution. We will showcase how it works, which hardware components it simulates and we will add useful extensions to this program by providing simulation for more complex hardware components like branch predictor. Finally, in collaboration with a team from Czech Technical University in Prague, we will develop a more advanced version of this program that uses a modern architecture/instruction set RISC-V.

SUBJECT AREA: Computer Architecture

**KEYWORDS:** Assembly, RISC, MIPS, RISC-V, Instruction Set, CPU, DRAM, SRAM, CPU, ALU, FPU, Pipeline, Branch Predictors, Cache, Memory, Microprocessors, Performance Modeling, Simulation

# ΠΕΡΙΛΗΨΗ

Μια από τις πιο βασικές γνώσεις στον τομέα της Πληροφορικής είναι πως λειτουργεί το υλικό καθώς και η αλληλεπίδραση του υλικού με το λογισμικό σε σύγχρονα υπολογιστικά συστήματα. Δυστυχώς, το κομμάτι αυτό είναι αρκετά δύσκολο στην κατανόηση επειδή οι μαθητές δεν μπορούν να οπτικοποιήσουν/προσομοιώσουν αυτά που διδάσκονται. Γι αυτόν τον λόγο έχουν αναπτυχθεί πολλά προγράμματα που στόχο έχουν να οπτικοποιήσουν αυτήν την αλληλεπίδραση καθώς και πολλές άλλες λειτουργίες του υλικού. Μία άλλη εξίσου σημαντική γνώση αφορά της συμβολικές γλώσσες. Η συμβολική γλώσσα MIPS είναι η πιο συχνά χρησιμοποιούμενη γλώσσα σε μαθήματα πανεπιστημίου. Ο κύριος λόγος που χρησιμοποιείται ευρέως η γλώσσα MIPS είναι γιατί γενικά οι συμβολικές γλώσσες είναι ιδιαίτερα περίπλοκες και δύσκολες στην κατανόηση ενώ η MIPS είναι απλή στην κατανόηση αλλά και όσο περίπλοκη χρείαζεται για να διδαχθούν όλα τα βασικά κομμάτια για τις συμβολικές γλώσσες. Επιπροσθέτως, MIPS μικροεπεξεργαστές χρησιμοποιούνται ακόμη και σήμερα σε σταθμούς εργασίας, ενσωματωμένα συστήματα (π.χ. δρομολογητές, αποκωδικοποιητές, καλωδιακά μόντεμ κ.λπ.) και ακόμη και υπερυπολογιστές. Σε αυτήν την πτυχιακή στρέφουμε το ενδιάφερον μας σε ένα ευρέως χρησιμοποιημένο project, τον QtMips. Ο QtMips είναι ένας προσομοιωτής για εκπαιδευτικούς σκοπούς που χρησιμοποιεί MIPS RISC ISA και προσομοιώνει πολλές βασικές λειτουργίες του υλικού όταν εκτελείται ένα πρόγραμμα. Θα περιγράψουμε τον τρόπο λειτουργίας του, ποιά κομμάτια του υλικού προσομοιώνει/οπτικοποιεί και θα επεκτείνουμε την λειτουργικότητα του πρόγραμματος προσθέτοντας προσομοίωση για πιο περίπλοκα κομμάτια του υλικού όπως ο branch predictor. Τέλος, σε συνεργασία με την ομάδα από το Τεχνικό Πανεπιστήμιο της Πράγας, θα συμβάλουμε στην ανάπτυξη μιας πιο εξελιγμένης έκδοσης αυτού του προγράμματος, που χρησιμοποεί την πιο σύγχρονη αρχιτεκτονική/σύνολο εντολών RISC-V.

ΘΕΜΑΤΙΚΗ ΠΕΡΙΟΧΗ: Αρχιτεκτονική Υπολογιστών

**ΛΕΞΕΙΣ ΚΛΕΙΔΙΑ:** Συμβολική Γλώσσα, RISC, MIPS, RISC-V, Σύνολο Εντολών, CPU, DRAM, SRAM, ALU, FPU, Διοχέτευση, Πρόβλεψη Διακλάδωσης, Κρυφή μνήμη, Μικροεπεξεργαστές, Απόδοση, Μοντελοποίηση, Προσομοίωση

# CONTENTS

| 1.  | INTRODUCTION                                                                                                              | 12                               |

|-----|---------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2.  | MIPS ARCHITECTURE DESIGN & CONCEPTS                                                                                       | 13                               |

| 2.1 | MIPS model                                                                                                                | 13                               |

| 2.2 | Registers                                                                                                                 | 13                               |

| 2.3 | Instruction formats                                                                                                       | 14                               |

| 2.4 | Instructions2.4.1Arithmetic Instructions2.4.2Logical Instructions2.4.3Branching Instructions2.4.4Load & Store Instruction | 15<br>15<br>17<br>18<br>19       |

| 2.5 | MIPS Pipeline & Hazards                                                                                                   | 19<br>19<br>20<br>20<br>21<br>21 |

| 2.6 | MIPS Memory Hierarchy                                                                                                     | 22<br>23                         |

| 3.  | VISUAL EDUCATIONAL SIMULATORS                                                                                             | 28                               |

| 4.  | QTMIPS                                                                                                                    | 34                               |

| 4.1 | Registers                                                                                                                 | 34                               |

| 4.2 | Program Memory                                                                                                            | 34                               |

| 4.3 | Data Memory                                                                                                               | 35                               |

| 4.4 | Program Execution                                                                                                         | 35                               |

| 4.5 | Code Editor & Compiler                                                                                                    | 36                               |

| 4.6 | OS Emulation                                                                                                              | 36                               |

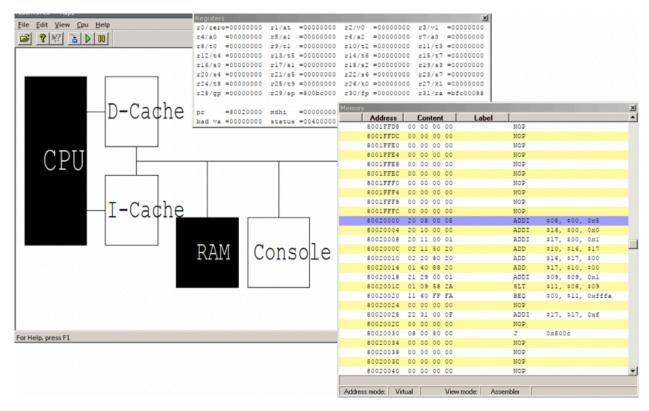

| 4.7 | L1 Program/Data Cache                                                                                                     | 38                               |

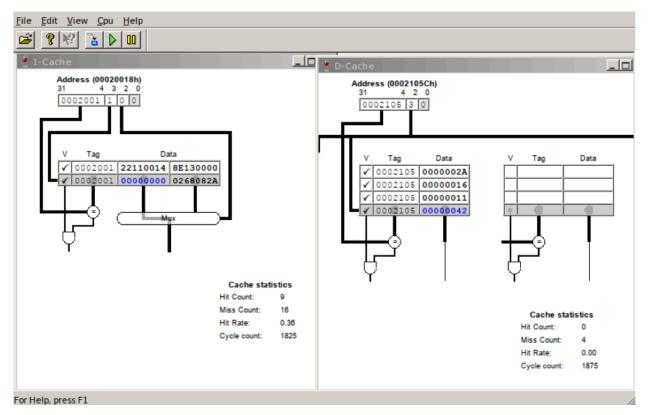

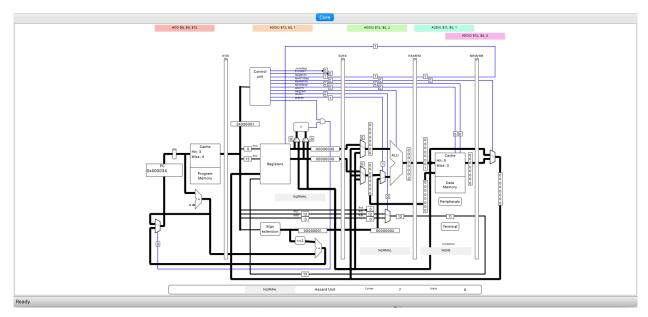

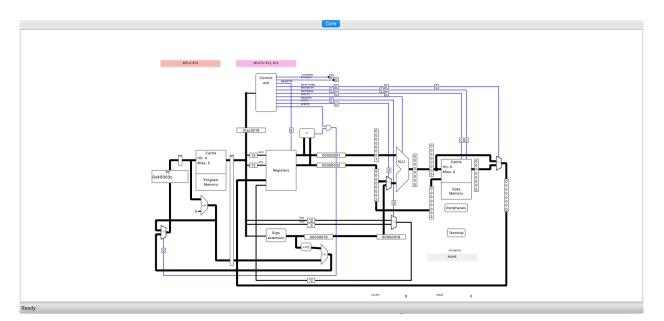

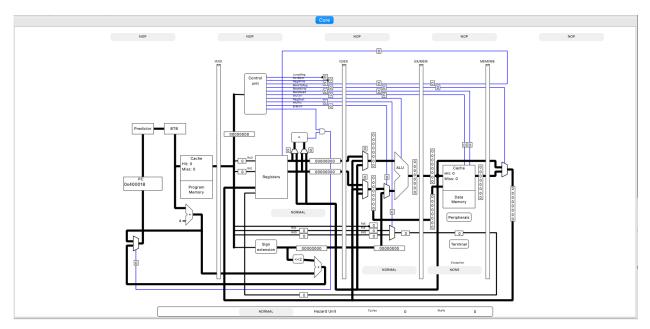

| 4.8 | Coreview                                                                                                                  | 38                               |

| 5.  | EXTENSIONS TO QTMIPS                                                                                                      | 40                               |

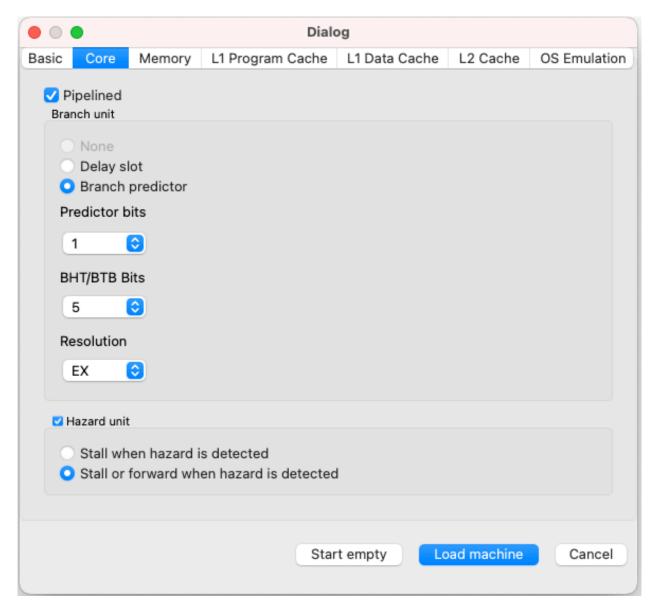

|                          | Branch Predictor                           | 41 |  |  |

|--------------------------|--------------------------------------------|----|--|--|

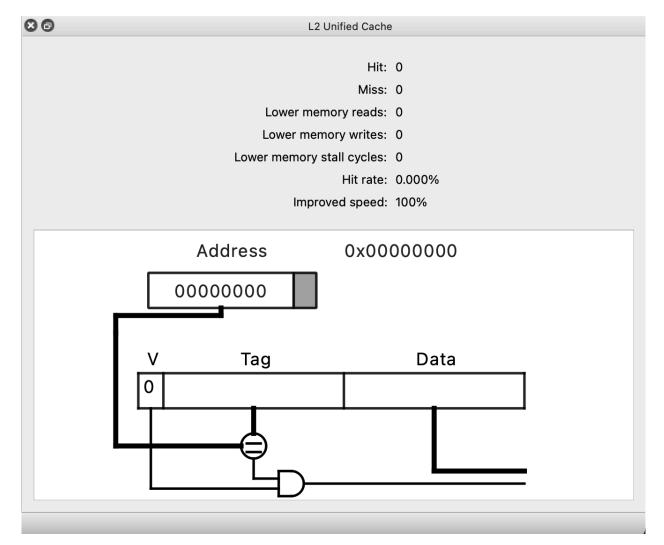

| 5.2                      | Cache                                      | 43 |  |  |

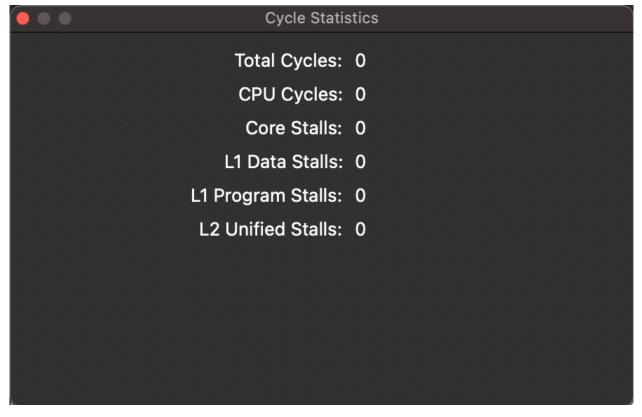

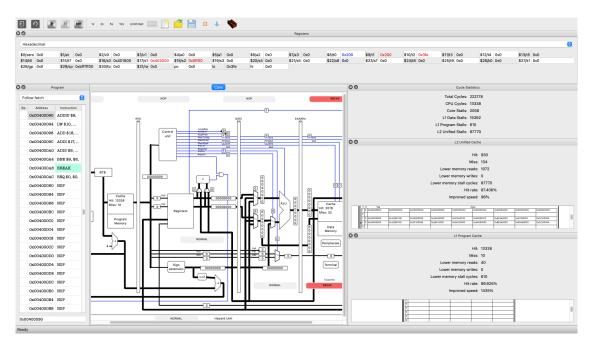

| 5.3                      | Cycle Statistics                           | 44 |  |  |

| 5.4                      | Representation of Register Values          | 44 |  |  |

| 5.5                      | Data and Control Hazard Unit               | 47 |  |  |

| 6.                       | EXPERIMENTS                                | 48 |  |  |

| 6.1                      | Branch Predictor                           | 48 |  |  |

| 6.2                      | L2 Cache                                   | 50 |  |  |

| 7.                       | QtMips MANUAL                              | 53 |  |  |

| 8.                       | EXTENSIONS ON QtMips AND SWITCH TO QtRVSim | 57 |  |  |

| 9.                       | FUTURE WORK                                | 58 |  |  |

| ABBREVIATIONS - ACRONYMS |                                            |    |  |  |

| REFERENCES               |                                            |    |  |  |

# LIST OF FIGURES

| 2.1<br>2.2<br>2.3<br>2.4                                    | Memory Hierarchy                                                  | 22<br>24                         |

|-------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7               |                                                                   | 31<br>31<br>32                   |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9 | QtMips Registers Dock                                             | 35<br>35<br>36<br>37<br>38       |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9 | 1-Bit Branch Predictor                                            | 42<br>43<br>43<br>44<br>45<br>46 |

| 6.1<br>6.2                                                  | QtMips Program Execution (Branch)QtMips Program Execution (Cache) | 49<br>52                         |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5                             | QtMips Program Loader                                             | 53<br>53<br>54<br>55<br>56       |

# LIST OF TABLES

| 2.2<br>2.3<br>2.4 | MIPS Instruction FormatsMIPS Arithmetic InstructionsMIPS Logical InstructionsMIPS Branching & Jump InstructionsMIPS Load & Store Instructions                                | 16<br>17<br>18 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 3.1               | Throughput per simulator                                                                                                                                                     | 33             |

| 6.2<br>6.3<br>6.4 | Cycles (Branch)Speedups (Branch)Speedups (Branch)Speedups (Cache)Cycles (Cache)Speedups per memory configurationCycles (Cache)Speedups (Cache)Cycles (Cache)Speedups (Cache) | 49<br>51<br>51 |

# PREFACE

The are two reasons behind me choosing to extend a tool used for teaching a course as my bachelor thesis.

- I wanted to leave something behind to a university that taught me how to program, taught me how to study and has grown me as a professional and as an individual, and, since this program will be used for educational purposes in Computer Architecture courses, it was exactly what I was looking for.

- To provide help to a beloved professor, Dimitris Gizopoulos, to take his courses to the next level (Don't get me wrong here, they are already very interesting and fun).

# **1. INTRODUCTION**

Computer Architecture is a compulsory course in the curriculum for most Computer Science and Computer Engineering studies. The reason behind this is that every programmer should, at least, have a rough idea of how a processor works internally. One could argue that this is not important for a *Software Engineer* because their main job is to program software and not hardware. This is the compilers job to do, right? To an extent this argument holds, but a Software Engineer that completely ignores all hardware-related components will never be able to program efficiently since they do not take into account important aspects like instruction pipelining, cache behavior, branch mispredictions, register usage and the list goes on and on. In order to be an expert programmer one should at least know what all these mean.

Learning Computer Architecture is not an easy task, teaching it however, is a very demanding job, especially in universities which want to offer a high quality of education. Professors will need all the help they can get. That is where visual simulators of how a processor works come into play. They offer a better understanding of all the important aspects of Computer Architecture by visualizing them and by giving the chance to students to try different configurations on a "processor model" which in turns allows them to dive more deeply onto how a processor really works.

There are many visual simulators available, and each one offers a unique set of features.

In this thesis we turn our attention to QtMips, a recently developed Graphical CPU Simulator with Cache Visualization, which was developed by Ing. Pavel Pisa, Ph.D. and Ing. Karel Koci of the Czech Technical University in Prague, and its source code as well as instructions to build it, can be found here.

On chapter 2 we will first define and analyze how a MIPS processor is designed and how it works, we will present its instruction set and basic concepts of this architecture such us pipelining, hazards and so on. On chapter 3 we will analyze what visual educational simulators offer and how to they aid the teaching of Computer Architecture. On chapter 4 we will present QtMips and what features it offers. On chapter 5 we will present the features that we decided to add to QtMips in order to extend its functionality. More specifically, our additions include:

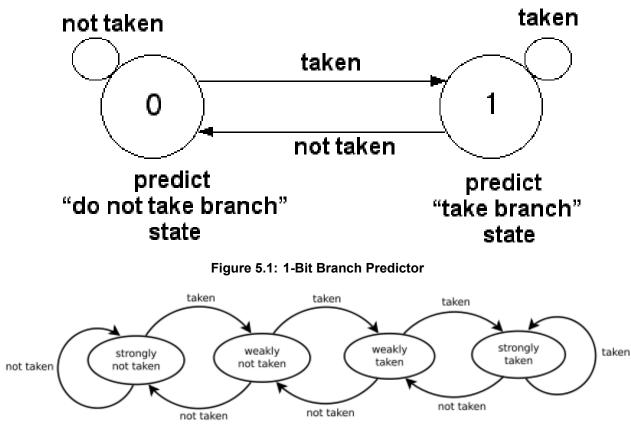

- 1-bit / 2-bit branch predictors (using branch target buffers).

- L2 (Unified) Cache.

- Control hazard unit.

- Detailed statistics for the program that is executed.

- Other tweaks.

On chapter 6 we will showcase program-executions / experiments ran on the new version of QtMips. On chapter 7 we will present a short manual for the new version of QtMips and on chapter 8 we will discuss what features we added to a modern version of QtMips, QtRVSim. Finally, on chapter 9 we will discuss our future work.

# 2. MIPS ARCHITECTURE DESIGN & CONCEPTS

MIPS (Microprocessor without Interlocked Pipeline Stages) is a reduced instruction set computer (RISC) instruction set architecture (ISA) developed by MIPS Computer Systems. It contains a set of instructions that are relatively simple to use, implement and fast to execute, in contrast to x86 architecture (CISC), which has more complex and multi-cycle instructions.

### 2.1 MIPS model

The MIPS32 architecture is based on a fixed-length, regularly encoded instruction set and uses a load/store data model. The architecture is streamlined to support optimized execution of high-level languages. Arithmetic and logic operations use a three-operand format, allowing compilers to optimize complex expressions formulation. Availability of 32 general-purpose registers enables compilers to further optimize code generation for performance by keeping frequently accessed data in registers.

MIPS architecture all contains 4 extensions that are referred to as co-processors (because they were initially implemented as separate chips out of the main CPU).

- CP0: This co-processor is used for vritual memory system, exception handling and various CPU states

- CP1: FPU It is used to handle floating point arithmetic.

- CP2: Free for each platform to utilize as it needs.

- CP3: Reserved for MIPS ISA extension.

## 2.2 Registers

MIPS contains 32 general-purpose registers, and each register has a capacity of 32 bits. The register \$0 (or \$zero) is a special register. It has the value of 0 and its contents cannot be altered, writes to it do not have any effect. Register \$31 is used as a link for jump-and-link instruction (jal). It stores the address of the next instruction that should be executed when the program returns from the block of code that it jumped to. The return address stored in this register is used by a jr instruction that should be the last of the subroutine of code. Besides these 32 registers, there are also the registers HI and LO which are accessible by special commands and they are only used to store the results of operations that would not fit in a single register. These are the results of different multiply and divide instructions which all have a two-word result. There is also the program counter which has 32 bits and contains the address of the instruction to be fetched. The two low-order bits always contain zero since MIPS I instructions are 32 bits long and are aligned to their natural word boundaries.

MIPS convention is to name the general-purpose registers by using two-character names following a dollar sign to represent a register. MIPS software separates 18 of the registers into two groups

|   | \$s0-\$s7, \$t0-\$t9, \$zero, | Fast locations for data. In MIPS, data must be in registers to perform arithmetic, |

|---|-------------------------------|------------------------------------------------------------------------------------|

| 0 |                               | register \$zero always equals 0, and register \$at is reserved by the assembler to |

|   | \$sp, \$ra, \$at              | handle large constants.                                                            |

#### Figure 2.1: MIPS Registers

- \$t0-\$t9: ten temporary registers that are not preserved by the callee (called procedure) on a procedure call.

- \$s0-\$s7: eight saved registers that must be preserved on a procedure call (if used, the callee saves and restores them).

#### 2.3 Instruction formats

Instruction format represents how an instruction is encoded. All MIPS instructions occupy 32 bits, the size of a word. Not all instructions have the same format, consider these 3 for example:

add reg1, reg2, reg3 (R-type) lw reg1, off(reg2) (I-type) j addr (J-type)

But, since all instructions are encoded using 32 bits, how is MIPS able to differentiate in which format to decode the current instruction? For that reason, MIPS Instructions are divided into three types: R (for register), I (for immediate) and J (for jump). Instruction bits are split in segments, which are called fields. Each instruction is split in a different way, depending on its type.

#### • R-Type instructions

- op: Basic operation of the instruction, traditionally called the opcode.

- rs: The first register source operand.

- *rt*: The second register source operand.

- *rd*: The register destination operand. It gets the result of the operation.

- shamt: Shift amount (used only for shift operations).

- *funct*: Function. This field, often called the function code, selects the specific variant of the operation in the op field.

#### I-Type instructions

- op: Same as in R-Type.

- *rs*: Same as in R-Type.

- *rt*: If the instruction writes to register this is the destination register, otherwise its the same as in R-Type instructions.

- address: A 16-bit (signed) number which, if the instruction uses memory, denotes the memory offset to be accessed, in words (relative to rs), if the instruction is a branch, denotes the offset, in words, (relative to the program counter) that the program should jump to if the branch is taken, and if the instruction is an arithmetic it is the number used in the operation.

#### • J-Type instruction

- op: Same as in R-Type and I-Type.

- *target*: This field is 26-bit and denotes to which address we can't the program to jump to. The jump target address is formed by concatenating the high order four bits of the PC (the address of the instruction following the jump), the 26 bits of the target field, and two 0 bits.

- The first three fields of the R-type and I-type formats are the same size and have the same names.

- The length of the fourth field in I-type is equal to the sum of the lengths of the last three fields of R-type.

- The formats are distinguished by the values in the first field: each format is assigned a distinct set of values in the first field (op) so that the hardware knows whether to treat the last half of the instruction as three fields (R-type) or as a single field (I-type).

On table 2.1 we can see how each instruction format is decoded.

| MIPS Instruction Formats |               |              |        |                |           |                 |

|--------------------------|---------------|--------------|--------|----------------|-----------|-----------------|

| Туре                     | Format (bits) |              |        |                |           |                 |

| R                        | opcode (6)    | rs (5)       | rt (5) | rd (5)         | shamt (5) | function<br>(6) |

| 1                        | opcode (6)    | rs (5)       | rt (5) | immediate (16) |           |                 |

| J                        | opcode (6)    | address (26) |        |                |           |                 |

#### Table 2.1: MIPS Instruction Formats

#### 2.4 Instructions

MIPS architecture provides simple instructions that are able to execute various tasks like arithmetic operations (integers and floating point), logical operations, conditional and unconditional branching, data transfer from memory to the CPU and some special instructions. Some of these instructions instructions are presented below.

## 2.4.1 Arithmetic Instructions

Most of these belong to the R-Type category because they operate on 3 registers. Two of the registers included in the instruction are used for read (rs, rt) and one of the register is used for storing the result (rd). The *opcode* field on R-Type instructions is always zero. So how does MIPS know which operation do apply on the registers? The answer is by checking the func field, which, as its name implies, specifies the function for the Arithmetic and Logic Unit (ALU) to use.

The arithmetic instructions that do not belong to the R-Type category belong to the I-Type category. The reason that not all of these instructions belong to the R-Type category is that not all arithmetic instructions require 3 registers (i.e. 3 variables) to be used. Imagine, for example, that we want to add a *constant* value to a register. If MIPS did not support addi (add operation in I-Type) category, we would first have to move the constant value to another register and then use the add operation which requires 3 registers. By including arithmetic operations in the I-Type category MIPS allows us to do fast arithmetic operations using constant values. This, however, comes with a drawback. Recall that the immediate field on I-Type instructions is only 16-bit long but registers are 32-bit long. This limits us to values between  $[0..2^{16}-1](0..65.535)$  if the operation is an unsigned operation and between  $[-2^{15}..2^{15}-1](-32.768..32.767)$  (The MIPS processor uses two's complement for signed immediate operands). The 16-bit offset limitation in arithmetic instructions is solved by using an lui instruction with combination of addi or ori for the constructions of large constants.

On table 2.2 we can see some of the most used arithmetic instructions. The full instruction set of MIPS32 can be found in [1].

| Name                    | Mnemonic | Туре | Operation                                                 |

|-------------------------|----------|------|-----------------------------------------------------------|

| Add                     | add      | R    | rd = rs + rt (rs and rt are interpreted as                |

|                         |          |      | signed)                                                   |

| Add Unsigned            | addu     | R    | signed)<br>rd = rs + rt (rs and rt are interpreted as un- |

|                         |          |      | signed)                                                   |

| Add Immediate           | addi     |      | rt = rs + immediate (rs is interpreted as                 |

|                         |          |      | signed)                                                   |

| Add Immediate Unsigned  | addiu    |      | rt = rs + immediate (rs is interpreted as un-             |

|                         |          |      | signed)                                                   |

| Set Less Than           | slt      | R    | rd = rs < rt ? 1 : 0 (rs and rt are interpreted           |

|                         |          |      | as signed)                                                |

| Set Less Than Unsigned  | sltu     | R    | rd = rs < rf? 1 : 0 (rs and rt are interpreted            |

|                         |          |      | as unsigned)                                              |

| Set Less Than Immediate | slti     |      | rt = rs < Immediate ? 1 : 0 (rs is interpreted            |

|                         |          |      | as signed)                                                |

| Set Less Than Immediate | sltiu    |      | rt = rs < Immediate ? 1 : 0 (rs is interpreted            |

| Unsigned                |          |      | as unsigned)                                              |

| Subtract                | sub      | R    | rd = rs - rt (rs and rt are interpreted as                |

|                         |          |      | signed)                                                   |

| Subtract Unsigned       | subu     | R    | rd = rs - rt (rs and rt are interpreted as un-            |

|                         |          |      | signed)                                                   |

| Divide                  | div      | R    | Lo = rs div rt, Hi = rs % rt (rt and rt are               |

|                         |          |      | interpreted as signed)                                    |

| Divide Unsigned         | divu     | R    | Lo = rs div rt, Hi = rs % rt (rt and rt are               |

|                         |          |      | interpreted as unsigned)                                  |

| Multiply                | mult     | R    | {Hi, Lo} = rs * rt (rt and rt are interpreted as          |

|                         |          |      | signed)                                                   |

| Multiply Unsigned       | multu    | R    | {Hi, Lo} = rs * rt (rt and rt are interpreted as          |

|                         |          |      | unsigned)                                                 |

| Shift Right Arithmetic  | sra      | R    | rd = rt » shamt (The difference with srl is               |

|                         |          |      | that sra does an arithmetic shift, it shifts              |

|                         |          |      | the sign bit in instead of adding zeros)                  |

|                         |          |      |                                                           |

| Table 2.2: | <b>MIPS</b> Arithmetic | Instructions |

|------------|------------------------|--------------|

|            |                        |              |

An important thing to note here is that MIPS supports both integer and floating point arithmetic. MIPS has a floating point coprocessor (numbered 1) that operates on single precision (32-bit) and double precision (64-bit) floating point numbers. This coprocessor has its own registers, which are numbered \$f0-\$f31. Because these registers are only 32-bits wide, two of them are required to hold doubles. To simplify matters, floating point operations only use even-numbered registers—including instructions that operate on single floats. Values are moved in or out of these registers a word (32-bits) at a time by lwc1, swc1, mtc1, and mfc1 instructions or by the l.s, l.d, s.s, and s.d pseudoinstructions. In this thesis we we will omit instructions that operate on floating point numbers because the baseline version of QtMips on which we built our extensions does not support floating point arithmetic. The addition of floating point operations and instructions is an extension that we plan on adding on the future version of the simulator. More about extensions and future work in the chapters below.

### 2.4.2 Logical Instructions

MIPS also offers a variety of logical instructions. These operate bitwise on two sources and write the result to a destination register. The first source is always a register and the second source is either an immediate or another register. On table 2.3 we present the ones which are most frequently used.

| MIPS Logical Instructions |      |                            |                                                    |  |  |

|---------------------------|------|----------------------------|----------------------------------------------------|--|--|

| Name Mnemonic Type        |      |                            | Operation                                          |  |  |

| And                       | and  | R                          | rd = rs & rt                                       |  |  |

| And Immediate             | andi | Ι                          | rt = rs & immediate (interpreted as un-<br>signed) |  |  |

| Nor                       | nor  | R                          | rd = !(rs   rt)                                    |  |  |

| Or                        | or   | R                          | rd = rs   rt                                       |  |  |

| Or Immediate              | ori  | I                          | rt = rs   immediate (interpreted as un-<br>signed) |  |  |

| Shift Left Logical        | sll  | R                          | rd = rt « shamt                                    |  |  |

| Shift Right Logical       | srl  | R                          | rd = rt » shamt                                    |  |  |

| Xor                       | xor  | R                          | $rd = rs \oplus rt$                                |  |  |

| Xor Immediate xori I      |      | $rt = rs \oplus immediate$ |                                                    |  |  |

### 2.4.3 Branching Instructions

MIPS offers instructions that help a program make decisions based on some conditions. Making a decision in a program means that the program can determine which code should be executed and which code should not be executed depending on the input it has in the current moment. These instructions are called branching instructions.

Some of the most frequently used ones are presented on table 2.4.

| MIPS Branching & Jump Instructions |      |                                               |                                                    |  |  |

|------------------------------------|------|-----------------------------------------------|----------------------------------------------------|--|--|

| Branch On Equal                    | beq  | I if rs == rt then PC = PC + 4 + Branch dress |                                                    |  |  |

| Branch On Not Equal                | bne  | I                                             | if rs != rt then PC = PC + 4 + Branch Ad-<br>dress |  |  |

| Branch Less Equal<br>Zero          | blez | Р                                             | if rs <= 0 then PC = PC + 4 + Branch Ad-<br>dress  |  |  |

| Branch Great Than<br>Zero          | bgtz | Р                                             | if rs > = then PC = PC + 4 + Branch Ad-<br>dress   |  |  |

| Branch Less Than                   | blt  | Р                                             | if rs < rt then PC = PC + 4 + Branch Ad-<br>dress  |  |  |

| Branch Greater Than                | bgt  | Р                                             | if rs > rt then PC = PC + 4 Branch Address         |  |  |

| Branch Less Than or<br>Equal       | ble  | Р                                             | if rs <= rt then PC = PC + 4 + Branch Ad-<br>dress |  |  |

| Branch Greater Than<br>or Equal    | bge  | Ρ                                             | if rs >= rt then PC = PC + 4 + Branch Ad-<br>dress |  |  |

| Jump                               | j    | J                                             | PC = Jump Address {PC + 4, address field,<br>00}   |  |  |

| Jump And Link                      | jal  | J                                             | \$ra = PC + 8; PC = Jump Address                   |  |  |

| Jump Register                      | jr   | J                                             | PC = rs                                            |  |  |

| Jump And Link Re-<br>gister        | jalr | J                                             | \$ra= PC + 8; PC = rs                              |  |  |

| Table 2.4 | : MIPS | Branching | & Jum | p Instructions |

|-----------|--------|-----------|-------|----------------|

|           |        |           |       |                |

P means that this instruction is a pseudo-instruction. For example, blez is translated to:

sIt \$t0, \$t1, \$t2 bne \$t0, \$0, L1

And ble is translated to:

slt \$t0, \$t1, \$t2 beq \$t2, \$zero, L1

## 2.4.4 Load & Store Instruction

Load instructions move data from memory into a register. The address for the load is the sum of a register specified in the instruction and a constant value that is coded into the instruction. Load instructions belong in the I-Type category.

Store instructions store data from a register to memory. Like load instructions, the memory address in which the value of the register will be written to is the sum of the immediate field in instruction with the register rs. These instructions also belong in the I-Type category.

MIPS offers the ability to load/store bytes (signed / unsigned), half-words (signed / unsigned), words (signed / unsigned).

Some of the most frequently used ones are presented on table **??** (pseudo-instructions (P) included).

Again, the full instruction set of MIPS32 can be found in [1].

|                             | MIPS Lo | ad & S | tore Instructions                                               |

|-----------------------------|---------|--------|-----------------------------------------------------------------|

| Load Byte                   | lb      | I      | rt = MEM[rs + immediate]{b07} (inter-<br>preted as signed)      |

| Load Byte Unsigned          | lbu     | Ι      | rt = MEM[rs + immediate]{b07} (inter-<br>preted as unsigned)    |

| Load Halfword               | lh      | I      | rt = MEM[rs + immediate]{b015} (inter-<br>preted as signed)     |

| Load Halfword Un-<br>signed | lhu     | I      | rt = MEM[rs + immediate]{b015} (inter-<br>preted as h unsigned) |

| Load Word                   | lw      | Ι      | rt = MEM[rs + immediate]{b031}                                  |

| Store Byte                  | sb      | Ι      | MEM[rs + immediate] = rt{b07}                                   |

| Store Halfowrd              | sbu     | Ι      | MEM[rs + immediate] = rt{b015}                                  |

| Store Word                  | SW      | I      | MEM[rs + immediate] = rt{b031}                                  |

Table 2.5: MIPS Load & Store Instructions

# 2.5 MIPS Pipeline & Hazards

## 2.5.1 Pipeline

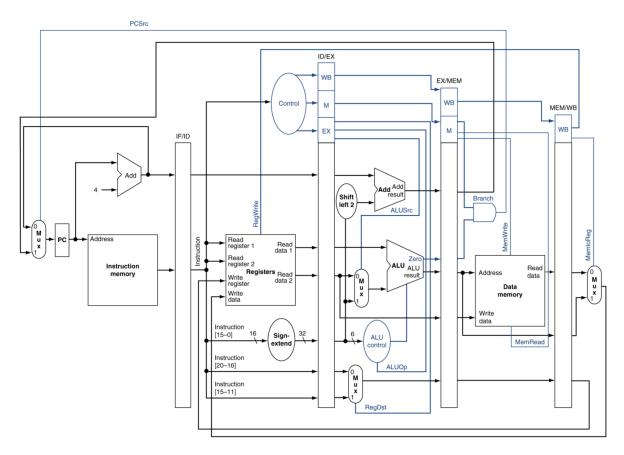

MIPS was designed to support pipelining (table 2.2. Pipelining is an implementation technique in which multiple instructions are overlapped in execution.

It's important to understand that pipelining improves performance by increasing instruction throughput, as opposed to decreasing the execution time of an individual instruction, but instruction throughput is the important metric because real programs execute billions of instructions. The way it achieves that is by partially overlapping the execution of instructions.

By exploiting pipeline, one can achieve high speedup. If we assume perfect conditions, *Time between instructions*<sub>pipelined</sub> =  $\frac{\text{Time between instructions}_{not-pipelined}}{\text{Pipeline Stages}}$

If one wants to build an architecture that implements pipelining, they have to follow three basic steps:

- Identify pipeline stages: This means to identify the common parts of all instructions. These parts are called stages.

- Isolate stages from each other.

- Resolve pipeline hazards that will occur.

The term pipeline hazards refer to situations on which the initiation of a new instruction at every clock cycle is not possible because it may lead to incorrect execution of the program.

MIPS instructions (and most RISC processor instructions) typically take five steps:

- 1. Fetch instruction from memory (Instruction Fetch IF): The instruction that the program counter points to is loaded from memory.

- Read registers while decoding the instruction (Instruction Decode ID): The regular format of MIPS instructions allows reading and decoding to occur simultaneously. Register identifiers rs and rt are used to getting values from given registers and immediate instruction field is sign extended to 32-bits.

- 3. Execute the operation or calculate an address (Execution EX): Execution stage contains ALU. It operates on top of two 32bit values and outputs another 32bit value as a result. For some operations it also updates HI and LO registers. Values passed to ALU are values loaded from registers from instruction decode stage.

- Access an operand in data memory (Memory MEM): Memory stage is dedicated for memory access. As an address is used ALU output from execute stage. For write instructions, the value to be written is value from register from rt passed through execute stage from decode stage.

- 5. Write the result into a register (Write Back WB): Either the output of ALU or from memory is written to the destination register.

We have presented the pipeline stages and isolated one from the other. Its important to mention that not all stages have an equal propagation delay and that is why the longest stage (the one that needs more time to finish) determines the clock cycle of the pipeline. A single instruction needs 5 of these clock cycles (# of stages) but in each cycle an instruction is always completed, allowing for bigger throughput and faster program execution overall due to the partial overlapping of instructions execution.

By introducing pipelining, we also introduce some hazards that pipelining inevitably brings along.

#### 2.5.2 Hazards

#### 2.5.2.1 Structural Hazards

Structural hazards occur when two instructions try to access the memory concurrently. More specifically, when an instruction is on its IF stage and the CPU tries to load the instruction from memory and another instruction is on its MEM stage and tries to load/store

data into memory. If the hardware cannot support the combination of these instructions, one has to wait on its current stage until the other instruction is finished with its stage. This, however, can be, and is actually solved by providing two separate memories, one for data and one for instructions.

### 2.5.2.2 Data Hazards

Data hazards occur when one instruction needs to access data from a register but a previous instruction was not finished writing the data to this register. Consider this simple example:

addi \$t0, \$zero, 15 sub \$t1, \$t1, \$t0

In order for the program to be executed as programmed to, the sub instruction requires the \$t0 register to have the value 15. But, since the value is written to the register on the last pipeline stage (WB) and sub needs the result on the execution stage to perform the operation (EX), sub would have to wait 2 extra cycles for \$t0 to have the correct result. These kind of instruction sequences exist in a large proportion in every program and if left un-handled it could cause severe stalls on the pipeline. MIPS addresses this issue by introducing something called **forwarding**. Forwarding is based on the observation that we don't need to wait for the instruction to complete before trying to resolve the data hazard. For the code sequence above, as soon as the ALU creates the sum for the add, we can supply it as an input for the subtract. Forwarding is achieved by adding extra hardware to retrieve the missing item early from the internal resources.

However, there is a specific data hazard which cannot be solved, even by using forwarding. Let's alter the above code slightly to observe why this occurs.

lw \$t0, 8(\$t4)

sub \$t1, \$t1, \$t0

The pipeline will reach to a point where Iw is on MEM stage and sub is on EX stage and will attempt to read \$t0. However, since Iw will have the result from memory that is to be written to \$t0 on the MEM stage, not in EX, its impossible to forward the correct value to sub because MEM stage has to be executed completely before forwarding. Therefore, sub will still have to wait 1 extra cycle to be executed correctly. These hazards are called load-use hazards and we rely on the compilers to eliminate them if possible.

#### 2.5.2.3 Control Hazards

Control hazards occur when the CPU fetches a control flow (branch or jump) instruction. Notice that we must begin fetching the instruction following the branch on the very next clock cycle. Obviously, the next instruction might be the next in the source code (PC + 4) or it might be somewhere else in the code, depending on the result of the branch. CPU simply does not know which instruction to fetch next and therefore needs to stall for the ALU to resolve the branch and decide where the next instruction to be executed is located. Branch is typically resolved (the branch condition is calculated) at the EX stage, which means the instruction after the branch has to stall for 2 cycles and the next instruction 1 cycle. Sometimes extra hardware is added to resolve branches on ID stage so the stall is only 1 cycle. However, branches are very common in a program and stalling for each

branch is not an efficient solution.

Modern CPUs (and MIPS itself of course) use branch prediction, which basically means that when a branch is fetched, the CPU predicts that it is either taken or not taken. If the prediction is correct, no stalls will get introduced. If the prediction is wrong, we stall the same cycles as without predicting. Its important to note that in modern CPUs branch predictors are very very accurate (98-99%).

Figure 2.2: MIPS Processor (Pipelined)

## 2.6 MIPS Memory Hierarchy

As mentioned previously, MIPS employs the load / store architecture which means that access to memory is provided by 2 basic operations: load data from memory and store data to memory. With this approach, its less complex for programmers who write the code but also enables aggressive compiler optimizations because there are no instructions that might read from or write to memory at the same time. Also, structural hazards are completely eliminated when two separate memories (for instructions and data) are available. This approach, however, does not tackle a very important issue when it comes to performance. The issue is that DRAM access cost is significantly larger than CPU access cost. There is a principle that underlies the way the programs operate. This principle is called principle of locality [[1], [2], [6]].

*Principle of locality*: All programs access a relatively small portion of their address space at any instant of time.

There are two different types of locality:

• Temporal locality (locality in time): When an item is referenced, it will tend to be

referenced again soon.

• *Spatial locality* (locality in space): When an item is referenced, items whose addresses are close by will tend to be referenced soon.

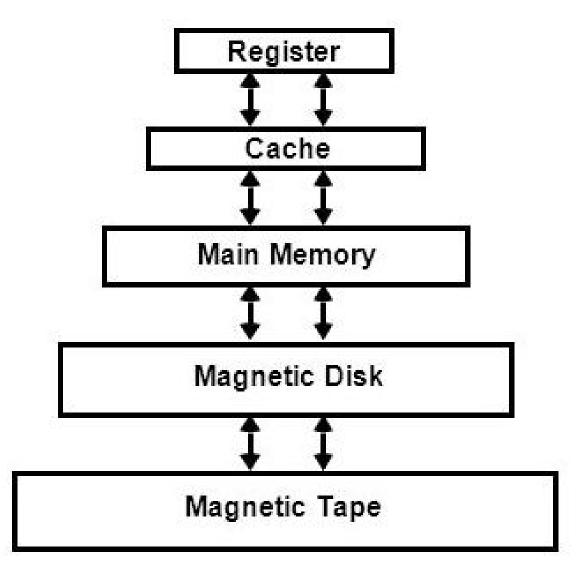

We take advantage of the principle of locality by implementing the memory of a computer as a memory hierarchy. A memory hierarchy consists of multiple levels of memory with different speeds and sizes. The faster memories are more expensive per bit than the slower memories and thus are smaller. Today, there are three primary technologies used in building memory hierarchies. Main memory is implemented from DRAM (dynamic random access memory), while levels closer to the processor (caches) use SRAM. DRAM is less costly per bit than SRAM, although it is substantially slower.

Today, a typical computer comes with a 6-level memory hierarchy (figure 2.3), more specifically:

- 1. *Registers*: This is the fastest memory one can get. Register access is virtually free but there are only a handful of them available in processors.

- 2. *L1 Cache*: This is the memory level closer to the processor. It offers very fast access (close to register access time) but its size is typically small, around 8 64 KB.

- 3. *L2 Cache*: This is the memory level above L1 Cache and its somewhat slower than L1 Cache but its also relatively fast. It's size varies between 256KB to 8MB.

- 4. *L3 Cache*: This is the memory level above L2 Cache. It's size varies between 10 64 MB.

- 5. *DRAM*: This is the main memory of the computer as we all know. DRAM is 10 to 100 times slower than a cache. In a typical computer its size is between 4 128 GB.

- 6. *Magnetic Disk*: This is (sometimes) the last level of memory in a computer. Accessing data from the disk is 100000 (!) slower than accessing data from DRAM. However, magnetic disks offer a capacity of 256GB a lot of TB.

## 2.6.1 Cache

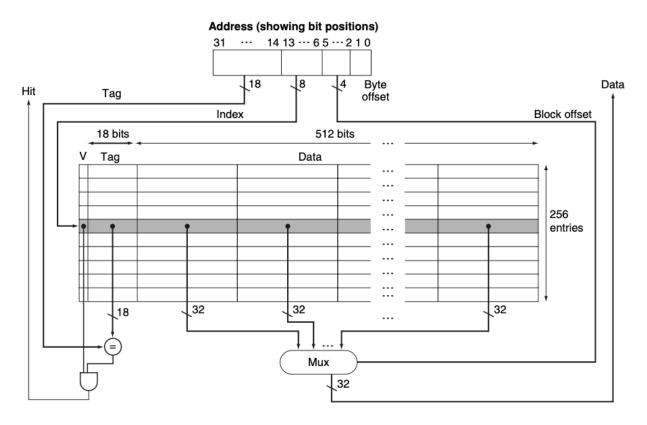

Cache memory (figure 2.4)refers to the memory areas that are close to the processor and offer very fast data access. Their drawback is that they are relatively small because of their cost. We mentioned before that a memory hierarchy can consist of multiple levels. However, data is copied between only two adjacent levels at a time (L1 to L2 for example). Now let's define some frequently used terms when it comes to caches.

The minimum unit of information that can be either present or not present in the two-level hierarchy is called a *block* or a *line*.

If the data requested by the processor appears in some block in the upper level, this is called a *cache hit*. If the data is not found in the upper level, the request is called a *cache miss*. The lower level in the hierarchy is then accessed to retrieve the block containing the requested data.

The *hit rate*, or *hit ratio*, is the fraction of memory accesses found in the upper level; it is often used as a measure of the performance of the memory hierarchy. The *miss rate* (1 –

Figure 2.3: Memory Hierarchy

hit rate) is the fraction of memory accesses not found in the upper level.

Since performance is the major reason for having a memory hierarchy, the time to service hits and misses is important. *Hit time* is the time to access the upper level of the memory hierarchy, which includes the time needed to determine whether the access is a hit or a miss.

*Miss penalty* is the time to replace a block in the upper level with the corresponding block from the lower level, plus the time to deliver this block to the processor. Because the upper level is smaller and built using faster memory parts, the hit time will be much smaller than the time to access the next level in the hierarchy, which is the major component of the miss penalty.

Now let's discuss how values are stored into caches.

The simplest way to assign a location in the cache for each word in memory is to assign the cache location based on the address of the word in memory. This cache structure is called *direct mapped*, since each memory location is mapped directly to exactly one location in the cache. In order to find a block, this formula is used:

Block address % Number of blocks in the cache.

It is obvious that many addresses will inevitably map to the same cache location. Therefore, we need a way to know if the address we want to access is the right one. For that reason, caches use *tags*. The tags contain the address information required to identify whether a word in the cache corresponds to the requested word. The tag needs only to contain the upper portion of the address, corresponding to the bits that are not used as an index into the cache.

Also, imagine that a program finished execution and left leftovers in the cache. The next program might try to access the same locations and even with the same tag, but the data is of course not the data it wants. For that reason cache entries also contain a *valid bit* which basically means if the entry is valid or not at the current time.

We mentioned only one block-placement method, direct mapped. There are however, more flexible ones.

In direct-mapped placement, a block can be placed at exactly one location. On the other side, on a *fully associative* cache, a block can be placed anywhere on the cache and lookup for each block is done using only the tag (and the valid bit). This lookup of course is done in parallel, which requires extra hardware and cost, and that's the reason only small caches are fully associative.

There is a middle ground solution for block placement. It is called *set associative*. In a set associative cache, there are is a certain number of locations where each block can be placed. A *n*-way set associative cache consists of a number of sets, each of which consists of n blocks. Each block in the memory maps to a unique set in the cache given by the index field, and a block can be placed in any element of that set. The block lookup is easy. We first map to the set of the cache which the address might be located and then we parallel-search for all blocks inside the set (again using tags and valid bits).

When CPU requests for an address in cache, it might be for reading or it might be for writing. In both cases, a cache miss can occur and a block should be replaced. The problem is which block should be replaced. When a miss occurs in a direct-mapped cache, the requested block can go in exactly one position, and the block occupying that position must be replaced. In an associative cache, we have a choice of where to place the requested block, and hence a choice of which block to replace. In a fully associative cache, all blocks are candidates for replacement. In a set-associative cache, we must choose among the blocks in the selected set.

The most commonly used scheme is least recently used (LRU), which we used in the previous example. In an LRU scheme, the block replaced is the one that has been unused for the longest time. There are other replacement policies like R (Random Replacement), LFU (Least frequently used), FIFO, LIFO, TLRU (Time aware least recently used), MRU (Most recently used).

One important aspect about caches is how to handle writes to memory. One possible solution is to write the data only in cache, to avoid main memory access but this would cause inconsistency. The simplest way to keep the main memory and the cache consistent is always to write the data into both the memory and the cache. This scheme is called *write-through*. When a miss occurs in a write-through cache, the most common strategy is to allocate a block in the cache, called write allocate. The block is fetched from memory and then the appropriate portion of the block is overwritten. An alternative strategy is to update the portion of the block in memory but not put it in the cache, called no write allocate.

As one probably can conclude, write-through behaves poorly in terms of performance because when we have a cache miss for write because we should first fetch the words of the block from memory and, after the block is fetched and placed into the cache, we overwrite the word that caused the miss into the cache block but we also write the word to main memory using the full address. These writes will take a long time, likely at least 100 processor clock cycles, and could slow down the processor considerably.

One solution to this problem is to use a write buffer. A write buffer stores the data while it is waiting to be written to memory. After writing the data into the cache and into the write buffer, the processor can continue execution.

The alternative to a write-through scheme is a scheme called *write-back*. In a write-back scheme, when a write occurs, the new value is written only to the block in the cache. The modified block is written to the lower level of the hierarchy when it is replaced. Write-back schemes can improve performance, especially when processors can generate writes as fast or faster than the writes can be handled by main memory; a write-back scheme is, however, more complex to implement than write-through.

Since no data is returned to the requester on write operations, a decision needs to be made on write misses, whether or not data would be loaded into the cache.

- Write allocate (also called fetch on write): Data at the missed-write location is loaded to cache, followed by a write-hit operation. In this approach, write misses are similar to read misses.

- Write no-allocate also called write around: Data at the missed-write location is not loaded to cache, and is written directly to the backing store. In this approach, data is loaded into the cache on read misses only.

Both write-through and write-back policies can use either of these write-miss policies, but usually they are paired in this way:[6]

A write-back cache uses write allocate, hoping for subsequent writes (or even reads) to the same location, which is now cached.

A write-through cache uses no-write allocate. Here, subsequent writes have no advantage, since they still need to be written directly to the backing store.

Figure 2.4: Cache

# 3. VISUAL EDUCATIONAL SIMULATORS

Computer Architecture courses are almost always encountered during the first semesters of a student's academic career. MIPS might seem relatively simple, but it is not. MIPS code, even simplified, remains an assembly language. Programming in an assembly language is very cumbersome, error-prone and very counter-intuitive because assembly is just an interface for machine code. It is the lowest level (closest to the machine) for programming. This is why most of the students usually get lost when they try to understand how assembly works. Moreover, even understanding the theoretical concepts of Computer Architecture like how the processor works, what is pipeline, what is cache and so on, is not a straightforward task. Students at my university, DiT, should consider themselves lucky that they have a professor like Prof.Gizopoulos who is very well-known to the Computer Architecture community and has contributed a lot in the field by doing various research activities. Just to mention a few, his Lab has organized twice (2020, 2021) the prestigious IEEE/ACM International Symposium on Microarchitecture (MICRO) which one of the two most important conferences in Computer Architecture (MICRO-53 and MICRO-54).

However, even the best professors need help. They need tools to visualize what they are explaining to the students, to demonstrate how an assembly program runs and, most importantly, to allow students to experiment themselves with assembly. This is why there are so many visual simulators for MIPS architecture which have been designed and developed by instructors or students in order to aid in the teaching of this difficult subject.

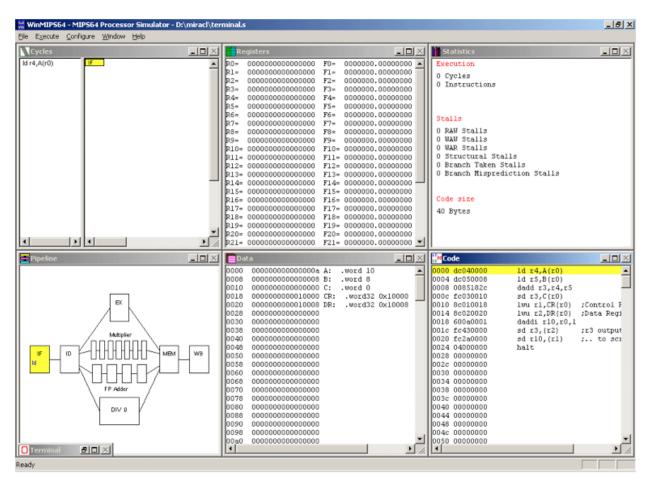

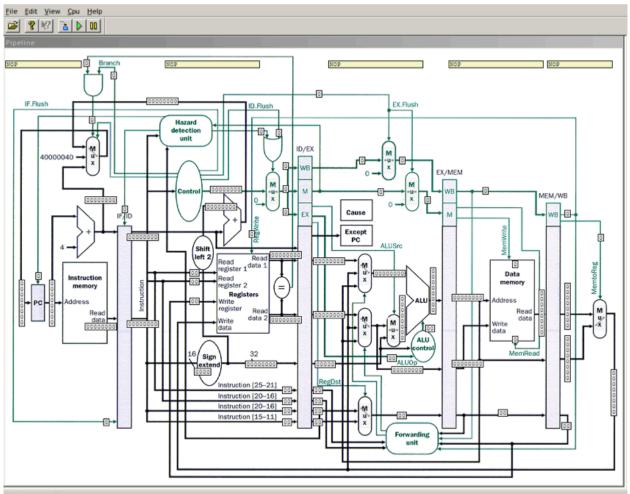

Currently, Prof.Gizopoulos uses a simulator called QtSpim (Figure 3.1) for Computer Architecture I course and WinMIPS64 (Figure 3.2) for Computer Architecture II course. Qt-Spim offers a huge variety of instructions and it remains the greatest tool if someone wants to experiment a lot with MIPS assembly language without delving into details of the hardware implementation of the CPU. It is basically a great interface to MIPS assembly language but it comes with little to no visualization of the processor and cache. These deficiencies greatly limit its usability for more advanced Computer Architecture courses.

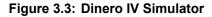

WinMIPS64, on the other hand, offers much more visual docks including visual representation of the pipeline stages, statistics dock which displays how many stalls the program has had and also the type of the stall (data, branch, structural hazards). However, Win-MIPS64 also lacks cache support. Because of this lack of cache support, Prof. Gizopoulos uses Dinero IV (Figure 3.3) simulator alongside WinMIPS64 which provides the user with a very detailed presentation about cache misses on all levels of cache and also splits them into instruction and data misses. But there is no graphical representation for the caches when Dinero is used. Just the statistics which need a lot of effort to understand and analyze. Another drawback of WinMIPS64 is that the program execution inside the simulator is very slow.

We should also mention two very important and frequently used simulators, Mipslt (Figures 3.4, 3.5, 3.6) and MARS (Figure 3.7).

MipsIt is the baseline for the QtMips simulator. It is a very old simulator which was developed only for Windows systems.

| FP Re  | igs     | Int Regs [16] |    | Data       | Text       |                                                                 |   |

|--------|---------|---------------|----|------------|------------|-----------------------------------------------------------------|---|

| nt Reg | js [16] |               | ØX | Text       |            |                                                                 | 8 |

| c      | -       | 0             | 8  |            |            | User Text Segment [00400000][00440000]                          |   |

| PC     |         | 0             |    | [00400000  | ] 8fa40000 | 1w \$4, 0(\$29) ; 183: 1w \$a0 0(\$sp) # argc                   |   |

| ause   | -       | 0             |    | [00400004  | 27a50004   | addiu \$5, \$29, 4 ; 184: addiu \$al \$sp 4 # argv              |   |

| adVA   | ddr -   |               |    |            | ] 24a60004 |                                                                 |   |

| tatu   | s =     | 3000ff10      |    | [0040000c  | 00041080   | sll \$2, \$4, 2 ; 186: sll \$v0 \$a0 2                          |   |

|        |         |               |    | [00400010  | ] 00c23021 | addu \$6, \$6, \$2 ; 187: addu \$a2 \$a2 \$v0                   |   |

| I      | -       | 0             |    | [00400014  | ] 0c000000 |                                                                 |   |

| ø      | -       | 0             |    | [00400018  | 00000000   |                                                                 |   |

|        |         |               |    |            | ] 3402000a |                                                                 |   |

| 0 [    | r0] -   | 0             |    | [00400020  | ) 0000000c | syscall ; 192: syscall # syscall 10 (exit)                      |   |

| u (    | at] -   | 0             |    |            |            |                                                                 |   |

| 2 [    | v0] -   | 0             |    |            |            | Kernel Text Segment [80000000][80010000]                        |   |

| 3 [    | v1] -   | 0             |    |            | ] 0001d821 |                                                                 |   |

| 4 [    | a0] =   | 0             |    |            | ] 3c019000 | 1u1 \$1, -28672 ; 92: sw \$v0 s1 # Not re-entrant and we can't  |   |

| 5 [    | al] -   | 0             |    | trust \$sp |            |                                                                 |   |

| 6 [    | a2] =   | 7ffff4e4      |    |            | ] ac220200 |                                                                 |   |

| 7 [    | a3] -   | 0             |    |            |            | 1ui \$1, -28672 ; 93: sw \$a0 s2 # But we need to use these     |   |

| 8 [    | t0] =   | 0             |    | registers  |            |                                                                 |   |

| 1 69   | t1] -   | 0             |    |            | ac240204   |                                                                 |   |

| 10 [   | t2] =   | 0             |    |            |            | mfc0 \$26, \$13 ; 95: mfc0 \$k0 \$13 # Cause register           |   |

| 11 [   | t3] -   | 0             |    |            | 001a2082   |                                                                 |   |

| 12 [   | t4] =   | 0             |    |            |            | andi \$4, \$4, 31 ; 97: andi \$a0 \$a0 0x1f                     |   |

| 13 [   | t5] -   | 0             |    |            | 34020004   |                                                                 |   |

| 14 [   | t6] -   | 0             |    |            |            | lui \$4, -28672 [m1_] ; 102: la \$a0m1_                         |   |

| 15 [   | t7] =   | 0             |    |            | 0000000c   |                                                                 |   |

| 16 [   | s0] -   | 0             |    |            |            | ori \$2, \$0, 1 ; 105: li \$v0 1 # syscall 1 (print_int)        |   |

| 17 [   | s1] =   | 0             |    |            |            | srl \$4, \$26, 2 ; 106: srl \$a0 \$k0 2 # Extract ExcCode Field |   |

| 18 [   | s2] -   | 0             |    |            |            | andi \$4, \$4, 31 ; 107: andi \$a0 \$a0 0x1f                    |   |

|        | s3] =   |               |    |            | 000000c    |                                                                 |   |

|        | s4] -   |               |    |            | 34020004   |                                                                 |   |

|        | s5] =   |               | U  |            |            | andi \$4, \$26, 60 ; 111: andi \$a0 \$k0 0x3c                   |   |

|        | s6] -   |               |    |            |            | lui \$1, -28672 ; 112: lw \$a0excp(\$a0)                        |   |

|        | s7] -   |               |    |            |            | addu \$1, \$1, \$4                                              |   |

|        | t8] -   |               |    |            |            | lw \$4, 384(\$1)                                                |   |

|        | t9] -   |               |    |            | 00000000   |                                                                 |   |

|        | k0] =   |               |    |            | 0000000c   |                                                                 |   |

|        | k1] -   | 0             |    | 180000108  | 34010018   | ori \$1, \$0, 24 ; 116: bne \$k0 0x18 ok_pc # Bad PC exception  |   |

Figure 3.1: QtSPIM

Figure 3.2: WinMIPS64

MipsIt offers some desirable and undesirable features. Some desirable features include:

- Program and data cache simulation.

- Usage statistics.

- Configurable environment.

Some of the undesirable features are:

- Bugs in fully pipelined mode.

- Often crashes.

- Non open-source, making it impossible for developers to fix anything.

MARS is a simulator written using Java language which makes it cross-platform. MARS uses its own MIPS assembler, offers an almost complete MIPS ISA, a MIPS code editor, attachable simulated hardware and other various tools such us instruction execution visualization.

However, it does not support pipelined CPU and does not offer cache simulation.

All of the previously mentioned simulators have one thing in common. They have low simulator throughput. Simulator throughput refers to the number of simulated instructions executed per second.

| 🚰 moda@netsec:~/computer                                                                                                                                                                                                                                                                                                                                        | r_architecture/d4                                          | -7 |        |        |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----|--------|--------|--|--|

| -ll-isize 1024<br>-ll-dsize 1024<br>-ll-dsize 0<br>-ll-dsize 0<br>-ll-dsbzize 0<br>-ll-dsbzize 0<br>-ll-dsbzize 0<br>-ll-isssoc 1<br>-ll-isssoc 1<br>-ll-isepl 1<br>-ll-ifetch d<br>-ll-dfetch d<br>-ll-dfetch d<br>-ll-dfetch d<br>-ll-dsback a<br>-skipcount 0<br>-stat-interval 0<br>-interval 0<br>-ontrigger 0x0<br>-off-trigger 0x0<br>5imulation begins. |                                                            |    |        |        |  |  |

| Simulation complete.<br>11-icache                                                                                                                                                                                                                                                                                                                               |                                                            |    |        |        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                 |                                                            |    |        |        |  |  |

| Demand Fetches<br>Fraction of total                                                                                                                                                                                                                                                                                                                             |                                                            |    |        |        |  |  |

| Demand Misses<br>Demand miss rate                                                                                                                                                                                                                                                                                                                               |                                                            |    |        |        |  |  |

| Multi-block refs<br>Bytes From Memory<br>( / Demand Fetches)<br>Bytes To Memory<br>( / Demand Writes)<br>Total Bytes r/w Mem<br>( / Demand Fetches)                                                                                                                                                                                                             | 0<br>1788600<br>2.3617<br>0<br>0.0000<br>1788600<br>2.3617 |    |        |        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                 |                                                            |    |        |        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                 |                                                            |    |        |        |  |  |

| Demand Fetches                                                                                                                                                                                                                                                                                                                                                  | 242661                                                     |    | 242661 | 159631 |  |  |

|                                                                                                                                                                                                                                                                                                                                                                 |                                                            |    |        |        |  |  |

| Demand Misses<br>Demand miss rate                                                                                                                                                                                                                                                                                                                               |                                                            |    |        |        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                 |                                                            |    |        |        |  |  |

| Bytes From Memory<br>( / Demand Fetches)                                                                                                                                                                                                                                                                                                                        | 408184<br>1.6821                                           |    |        |        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                 |                                                            |    |        |        |  |  |

| ( / Demand Writes)<br>Total Bytes r/w Mem                                                                                                                                                                                                                                                                                                                       | 2.3086<br>599864                                           |    |        |        |  |  |

| ( / Demand Fetches)                                                                                                                                                                                                                                                                                                                                             | 2.4720                                                     |    |        |        |  |  |

| Execution complete.<br>(moda@netsec d4-7)\$                                                                                                                                                                                                                                                                                                                     |                                                            |    |        |        |  |  |

Figure 3.4: Mipslt Windows

For Help, press F1

Figure 3.6: Mipslt Pipeline

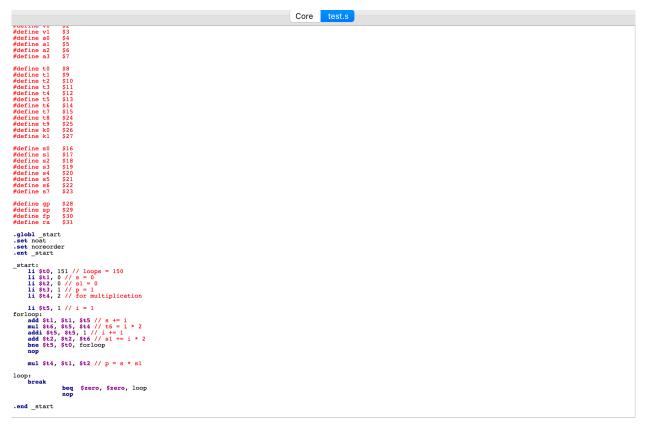

Educational Simulation Framework for Performance Modeling of RISC Microprocessors

| <u>File Edit Run S</u> ettings <u>T</u> ools <u>H</u> elp      |                            |   |        |              |             |

|----------------------------------------------------------------|----------------------------|---|--------|--------------|-------------|

|                                                                |                            |   | -      | max (no inte | Ò           |

| Edit Execute                                                   |                            |   | Coproc | 1 Copro      | c 0         |

| # Add Some Integers                                            |                            |   |        | Regist       | ers         |

| +                                                              |                            |   | Name   | Number       | Value       |

| <pre># read num1 and num2 from keyboard</pre>                  |                            |   | \$zero | 0            | 0x000000000 |

| # print (on screen) the sum of the p                           | numbers read               |   | \$at   | 1            | 0x00000000  |

| #<br># v0: num1 and num2                                       |                            |   | \$v0   | 2            | 0x00000000  |

| # t0: sum                                                      |                            |   | \$v1   | 3            | 0x00000000  |

| #                                                              |                            | = | \$a0   | 4            | 0x00000000  |

| .data                                                          |                            |   | \$a1   | 5            | 0x00000000  |

| prompt: .asciiz "\n Enter a number:                            |                            |   | \$a2   | 6            | 0x00000000  |

| lresult: .asciiz "The sum of your nu                           | nbers is "                 |   | \$a3   | 7            | 0x00000000  |

| 2 .globl main                                                  |                            |   | \$t0   | 8            | 0x00000000  |

| 3 .text<br>4 main:                                             |                            |   | \$t1   | 9            | 0x00000000  |

| 5 # read and add first num                                     |                            |   | \$t2   | 10           | 0x00000000  |

| 6 li \$v0, 4 # system                                          | call code for print string |   | \$t3   | 11           | 0x00000000  |

| 7 la \$a0, prompt # load ad                                    | idr of prompt in \$a0      |   | \$t4   | 12           | 0x00000000  |

| s syscall # print ;                                            | prompt                     |   | \$t5   | 13           | 0x00000000  |

| 9 li \$v0, 5 # system                                          | call code for read int     |   | \$t6   | 14           | 0x00000000  |

| ) syscall # read no                                            | uml into \$v0              |   | \$t7   | 15           | 0x00000000  |

| 1 add \$t0, \$t0, \$v0 # add nu<br>2 # read and add second num | n1 to sum                  |   | \$30   | 16           | 0x00000000  |

|                                                                | call code for print string |   | \$31   | 17           | 0x00000000  |

|                                                                |                            |   | \$32   | 18           | 0x00000000  |

|                                                                |                            |   | \$33   | 19           | 0x00000000  |

| ine: 15 Column: 25 🗹 Show Line Numbers                         |                            |   | \$34   | 20           | 0x00000000  |

|                                                                |                            |   | \$85   | 21           | 0x00000000  |

| Mars Messages Run I/O                                          |                            |   | \$36   | 22           | 0x00000000  |

|                                                                |                            | 1 | \$37   | 23           | 0x00000000  |

|                                                                |                            |   | \$t8   | 24           | 0x00000000  |

|                                                                |                            |   | \$t9   | 25           | 0x00000000  |

| Clear                                                          |                            |   | \$k0   | 26           | 0x00000000  |

|                                                                |                            |   | \$k1   | 27           | 0x00000000  |

|                                                                |                            |   | \$gp   | 28           | 0x10008000  |

|                                                                |                            |   | I.a.   | 20           |             |

Figure 3.7: MARS