# ΕΘΝΙΚΟ ΚΑΙ ΚΑΠΟΔΙΣΤΡΙΑΚΟ ΠΑΝΕΠΙΣΤΗΜΙΟ ΑΘΗΝΩΝ

# ΣΧΟΛΗ ΘΕΤΙΚΩΝ ΕΠΙΣΤΗΜΩΝ ΤΜΗΜΑ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΤΗΛΕΠΙΚΟΙΝΩΝΙΩΝ ΠΡΟΓΡΑΜΜΑ ΜΕΤΑΠΤΥΧΙΑΚΩΝ ΣΠΟΥΔΩΝ

#### ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

"Evaluation of gem5-based Modeling Frameworks for Heterogeneous SoC Designs with Domain-Specific Accelerators."

Αργυρώ Α. Ριτσογιάννη

Επιβλέπων (ή Επιβλέπουσα ή Επιβλέποντες): Δημήτρης Γκιζόπουλος, Καθηγητής

AOHNA

09/24

#### ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

Evaluation of gem5-based Simulation Frameworks for Heterogeneous System-on-Chip Designs with Domain-Specific Accelerators

Αξιολόγηση Εργαλείων Προσομοίωσης Ετερογενών Σχεδιάσεων Συστημάτων-σε-Τσιπ με Επιταχυντές Συγκεκριμένου Τομέα

Αργυρώ Α. Ριτσογιάννη

A.M.: CS3190007

**ΕΠΙΒΛΕΠΩΝ (ή Δημήτρης Γκιζόπουλος,** Καθηγητής **ΕΠΙΒΛΕΠΟΝΤΕΣ)**:

**ΕΞΕΤΑΣΤΙΚΗ ΕΠΙΤΡΟΠΗ** Γκιζόπουλος Δημήτρης, Καθηγητής (εάν υπάρχει): Πασχάλης Αντώνης, Καθηγητής Παπαδημητρίου Γεώργιος, Διδάκτωρ Πληροφορικής

#### ΠΕΡΙΛΗΨΗ

Στον τομέα της αρχιτεκτονικής υπολογιστών, η χρήση επιταχυντών υλικού σε σύγχρονα συστήματα καθίσταται κρίσιμη για την επίτευξη της καλύτερης απόδοσης. Αυτή η διπλωματική εξετάζει διάφορα εργαλεία προσομοίωσης που βασίζονται στον μικροαρχιτεκτονικό προσομοιωτή gem5 ή μπορούν να ενταχθούν σε αυτόν, σχεδιασμένα να δοκιμάζουν διαφορετικές σχεδιάσεις System-on-Chip (SoC) που περιλαμβάνουν συγκεκριμένους επιταχυντές υλικού για συγκεκριμένες εργασίες. Ελέγχει πόσο καλά αυτά τα πλαίσια μπορούν να μιμηθούν ετερογενή SoC του πραγματικού κόσμου, εστιάζοντας σε παράγοντες όπως το πόσο γρήγορα εκτελείται η προσομοίωση, πόσο προσαρμόσιμα είναι και πόσο εύκολα είναι στη χρήση τους. Η πτυχιακή αυτή διερευνά επίσης πώς διαφορετικές ρυθμίσεις και μέθοδοι μοντελοποίησης στον gem5 επηρεάζουν την ομαλή ενσωμάτωση αυτών των συγκεκριμένων επιταχυντών στα συστήματα. Τα ευρήματα παρέχουν χρήσιμες πληροφορίες για τη λήψη ενημερωμένων αποφάσεων σχετικά με τα πλαίσια προσομοίωσης που θα χρησιμοποιηθούν, βοηθώντας στην αποτελεσματική αξιολόγηση και ανάπτυξη προηγμένων σχεδίων SoC.

#### **ABSTRACT**

In the field of computer architecture, using hardware accelerators in modern systems is becoming crucial for achieving the best performance. This thesis surveys various simulation frameworks that are based on or can be integrated into the microarchitectural simulator gem5, designed to test different System-on-Chip (SoC) designs that include specific hardware accelerators for certain tasks. It analyzes how well these frameworks can mimic real-world heterogeneous SoCs, focusing on aspects such as the simulation speed, ease of customization, ease of use. The study also explores how different settings and modeling methods in gem5 affect the smooth addition of these specific accelerators into systems. The findings provide useful information for making informed decisions about which simulation frameworks to use, helping in the effective evaluation and development of advanced SoC designs.

**SUBJECT AREA**: Computer Architecture

**KEYWORDS**: Hardware Accelerators, gem5 Simulation Framework, Heterogeneous System-on-Chip, Domain-Specific Accelerators, Computer Architecture, Simulation Framework Comparison, gem5-aladdin, gem5-SALAM, Maestro, SMAUG, gem5-x

# **THANKS**

I would like to thank my prof. Dimitris Gizopoulos for suggesting the idea of my thesis and for giving me the opportunity to work on such an interesting topic.

I would also like to thank my supervisor, PostDoc Researcher George Papadimitriou, for the continuous support and the help towards completing this thesis by providing help and suggestions throughout it.

October 2024

# **CONTENTS**

# Πίνακας περιεχομένων

| 1. | 1. INTRODUCTION                                                            | 11 |

|----|----------------------------------------------------------------------------|----|

|    | 1.1 Overview of the importance of accelerators in modern computing         | 11 |

| a  | 1.2 The significance of having a framework for designing and eval          | _  |

| 2. | 2. BACKROUND AND SIMULATION FRAMEWORKS ANALYSIS                            | 15 |

|    | 2.1 gem5-Aladdin                                                           | 15 |

|    | 2.2 SMAUG                                                                  | 19 |

|    | 2.3 gem5-SALAM                                                             | 24 |

|    | 2.4 gem5-X                                                                 | 26 |

|    | 2.5 MAESTRO                                                                | 29 |

|    | 2.6 Similarities                                                           | 32 |

|    | 2.7 Architectural Details of Each Framework                                | 34 |

|    | 2.7.1 Framework Architectures                                              | 34 |

|    | 2.7.2 Design Philosophies                                                  | 39 |

|    | 2.8 Operational Mechanisms and Workflow of the Frameworks                  | 40 |

|    | 2.9 Advantages and Disadvantages of Each Framework                         | 41 |

|    | 2.10 Advantages, disadvantages, and critical aspects                       | 44 |

| 3. | 3. RATIONALE FOR SELECTION                                                 | 51 |

|    | 3.1 Explanation for choosing gem5-SALAM and gem5-Aladdin for in comparison | -  |

|    | 3.2 In-Depth Power Consumption Study                                       | 52 |

|    | 3.3 Scalability and Adaptability Exploration                               | 52 |

|    | 3.4 Integration and Usability Assessment                                   | 52 |

|    | 3.5 Looking Ahead: Anticipating Challenges and Outcomes                    | 52 |

| 3.6 Comparison and Experimental Measurement Evaluation               | 52 |

|----------------------------------------------------------------------|----|

| 4. EXPERIMENTAL SETUP & EVALUATION                                   | 55 |

| 4.1 Experimental Setup                                               | 55 |

| 4.1.1 Installation Procedure                                         | 55 |

| 4.1.2 Source Code Repository Updates                                 | 55 |

| 4.1.3 Constructing the Simulation Environment Building gem5-Aladdin  | 56 |

| 4.1.4 Executing the Initial Model                                    | 56 |

| 4.1.5 Adaptation for Alternative Benchmarks                          | 56 |

| 4.1.6 Commencement of Installation Protocols                         | 59 |

| 4.1.7 Configuration and Deployment of LLVM/Clang                     | 60 |

| 4.1.8 Repository Acquisition and Framework Compilation               | 60 |

| 4.1.9 Execution of gem5-SALAM                                        | 60 |

| 4.1.10 Modification of Benchmarks and Analysis of Results            | 61 |

| 4.2 Details of the evaluation process                                | 64 |

| 4.2.1 Evaluation Strategy                                            | 65 |

| 4.2.2 Benchmark Selection and Justification                          | 65 |

| 4.2.3 Test Environment and Configuration                             | 65 |

| 4.2.4 Execution of Benchmarks                                        | 65 |

| 4.2.5 Data Collection Methodology                                    | 65 |

| 4.2.6 Analysis of Test Results                                       | 65 |

| 4.2.7 Addressing Anomalies and Inconsistencies                       | 65 |

| 4.2.8 Implications of Findings                                       | 66 |

| 4.3 Modifications Made to Run Common Benchmarks for Analysis and Com | -  |

|                                                                      |    |

| 4.4 Any challenges or collisions encountered during the experiments  |    |

| 5. RESULTS AND REVIEW (ANALYSIS)                                     |    |

| 5.1 Types of benchmarks used for analysis                            | 70 |

| 5.2 P   | resentation of results through diagrams and charts          | 72 |

|---------|-------------------------------------------------------------|----|

|         | nterpretation of results, including performance metrics (cy | ·  |

| 6. CON  | CLUSION                                                     | 89 |

| 6.1 O   | verall conclusion                                           | 89 |

| 6.2 S   | ummary of findings from the comparison                      | 89 |

| 7. FUTU | JRE WORK                                                    | 91 |

| REFER   | ENCES                                                       | 93 |

# **List of Figures**

| Figure 1: Example of a System on Chip (SoC)1                                     | 6  |

|----------------------------------------------------------------------------------|----|

| Figure 2: Shared Scratchpad Memory1                                              | 8  |

| Figure 3: Smaug's execution flow                                                 | :1 |

| Figure 4: Accelerator model creation                                             | :5 |

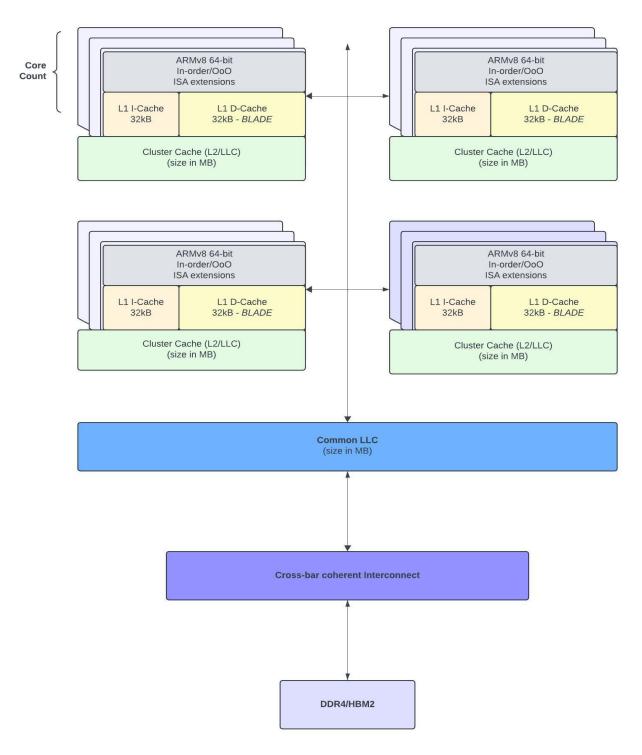

| Figure 5: Gem5-X's platform2                                                     | 28 |

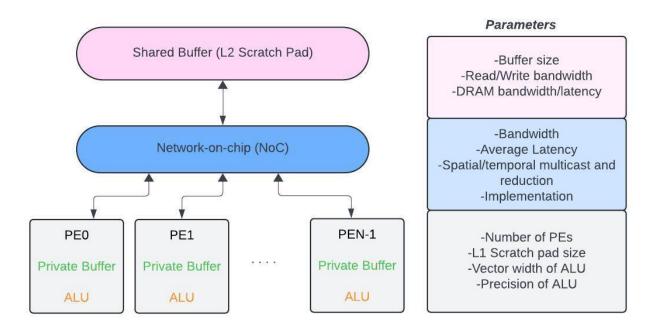

| Figure 6: Abstract parameterized DNN accelerator                                 | 1  |

| Figure 7: Screenshots of Aladdin indicative benchmark results5                   | 8  |

| Figure 8: Screenshots of gem5-Aladdin indicative benchmark results5              | 8  |

| Figure 9: Screenshots of gem5-SALAM's indicative benchmark results6              | 2  |

| Figure 10: Screenshots of gem5-SALAM's indicative benchmark results6             | 3  |

| Figure 11: Code change to run benchmark without accelerator6                     | 7  |

| Figure 12: Code change to run benchmark without accelerator6                     | 8  |

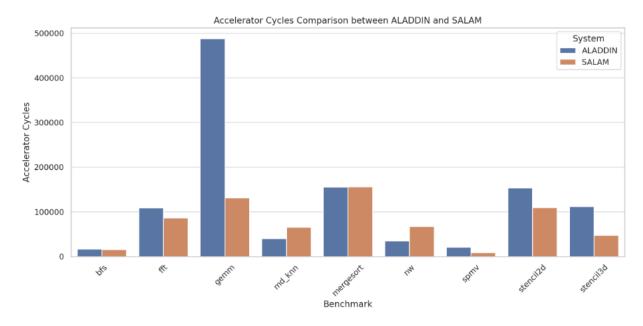

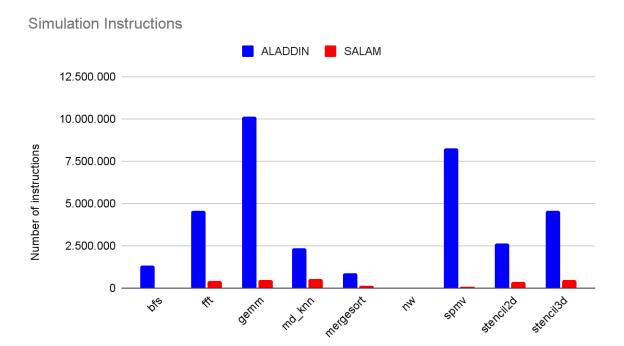

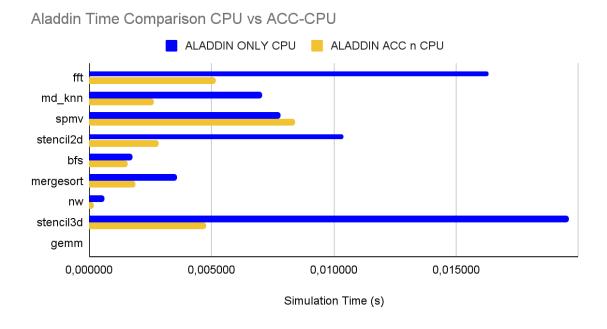

| Figure 13: Accelerator cycles comparison between gem5-Aladdin and gem5-SALAM7    | '3 |

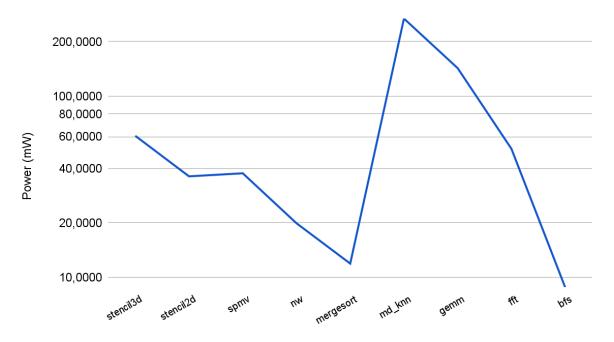

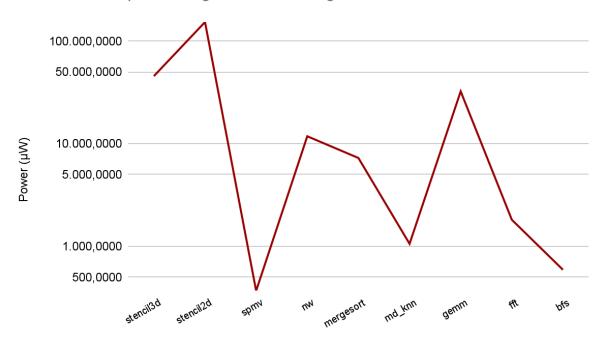

| Figure 14: Power consumption for gem5-Aladdin in logarithmic scale7              | '4 |

| Figure 15: Power consumption for gem5-SALAM in logarithmic scale7                | '4 |

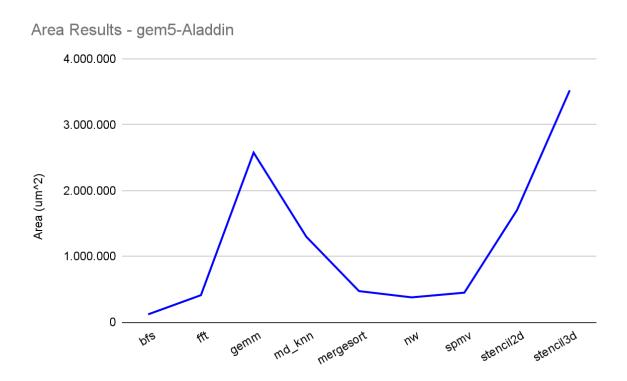

| Figure 16: Area results of gem5-Aladdin across benchmarks                        | 5  |

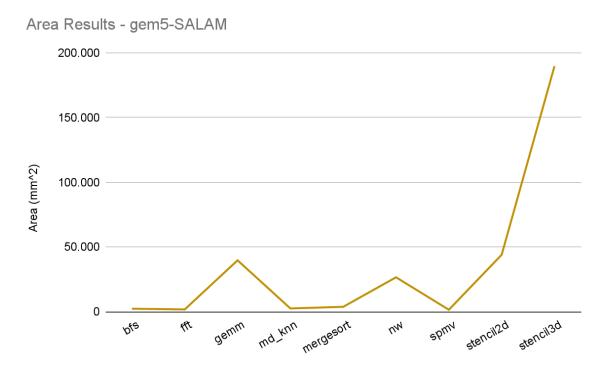

| Figure 17: Area results of gem5-SALAM across benchmarks                          | 5  |

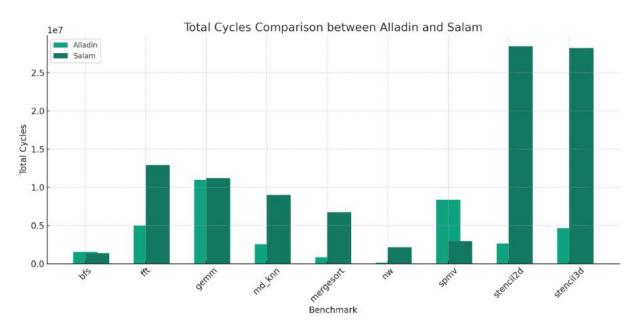

| Figure 18: Total cycles comparison between gem5-Aladdin and gem5-SALAM7          | '6 |

| Figure 19: Comparison of instructions for gem5-Aladdin vs gem5-SALAM acros       |    |

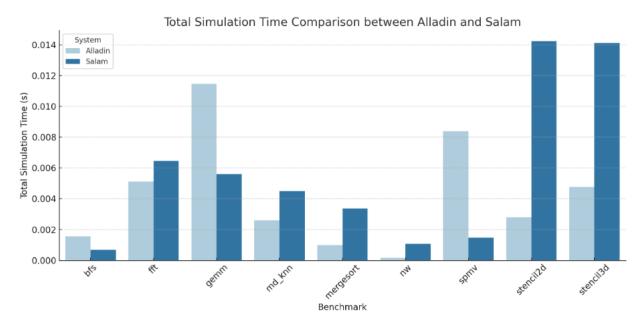

| Figure 20: Total simulation time comparison between gem5-Aladdin and gem5-SALAM7 | 7  |

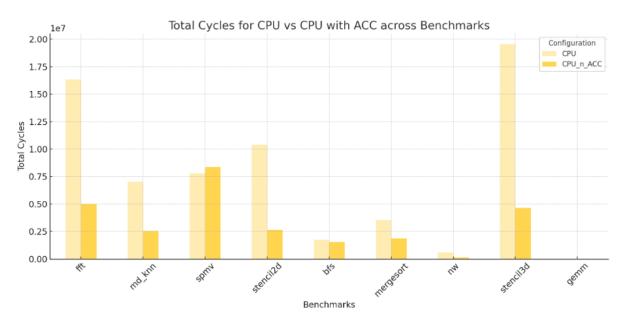

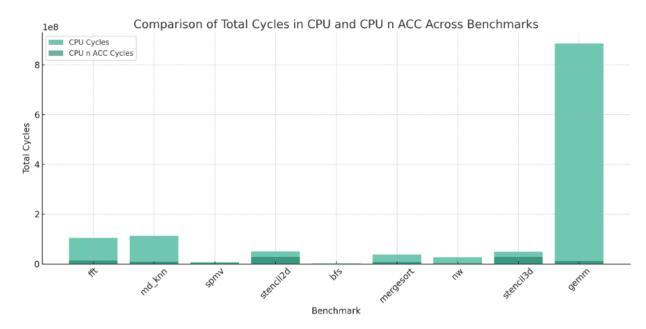

| Figure 21: Total cycles for CPU vs CPU with accelerator across benchmarks7       | '8 |

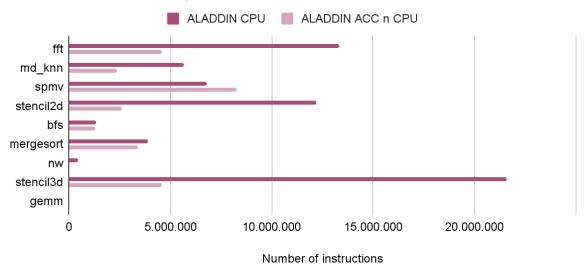

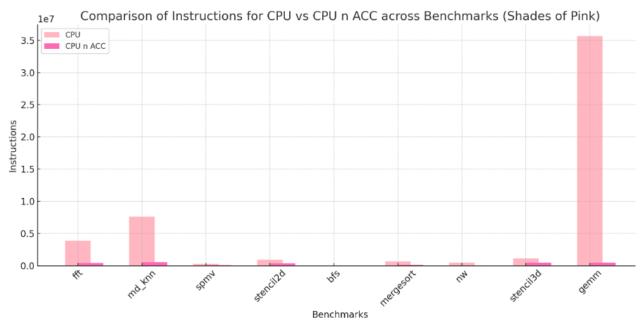

| Figure 22: Instructions comparison between CPU and accelerator vs CPU only7      | '9 |

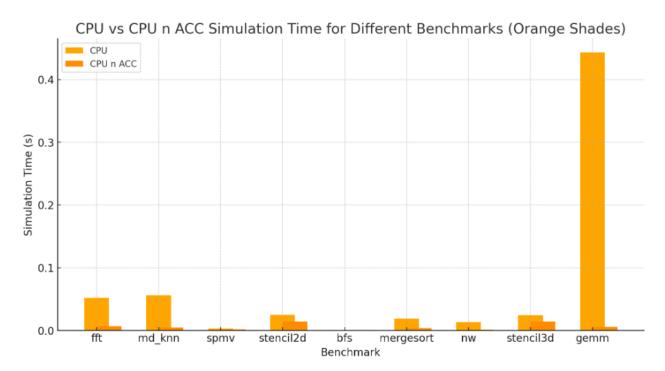

| Figure 23: Simulation time comparison CPU vs CPU & Accelerator7                  | œ. |

| Figure 24: Comparison of total cycles in CPU only and CPU and accelerator acros  |    |

| Figure 25: Comparison of instructions for CPU vs CPU and accelerator across benchmarks |

|----------------------------------------------------------------------------------------|

| 80                                                                                     |

| Figure 26: CPU vs CPU with accelerator simulation time for different benchmarks81      |

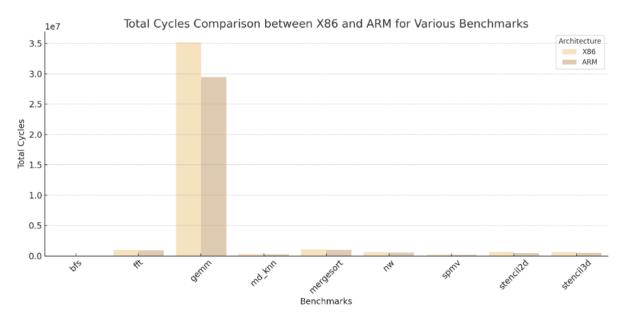

| Figure 27: Total cycles comparison between X86 and ARM for various benchmarks82        |

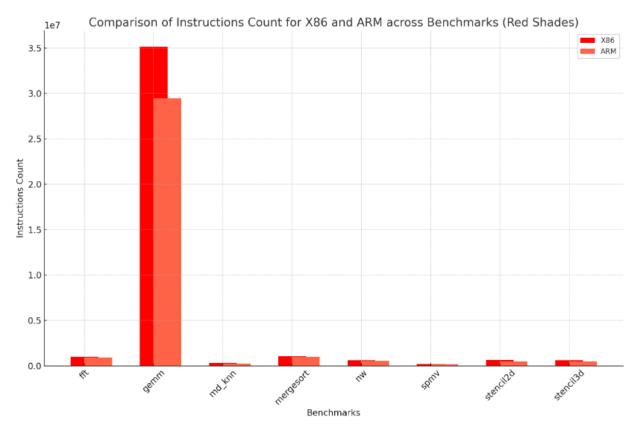

| Figure 28: Comparison of instructions count for X86 and ARM across benchmarks82        |

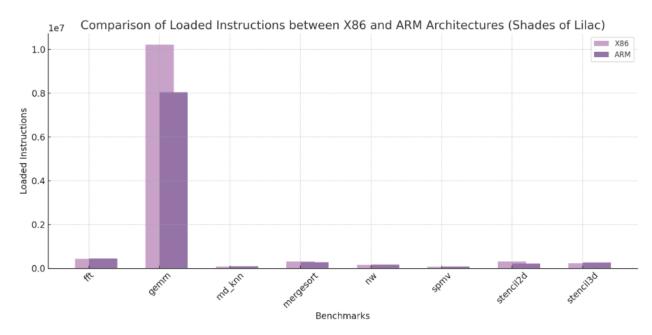

| Figure 29: Comparison of loaded instructions between X86 and ARM acrhitectures83       |

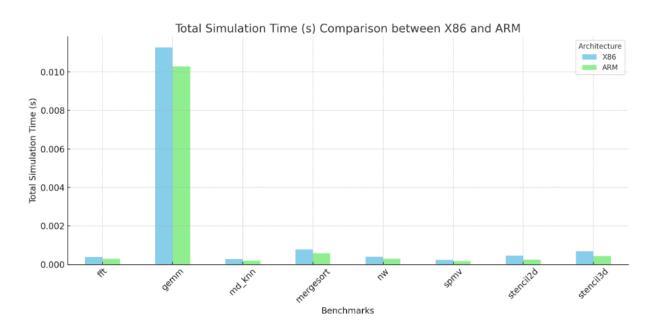

| Figure 30: Total simulation time comparison between X86 and ARM83                      |

|                                                                                        |

| List of Tables                                                                         |

| Table 1: Aspects of each framework46                                                   |

| Table 2: More features and characteristics46                                           |

| Table 3: ISA and usage description of each framework48                                 |

| Table 4: Supported modes and additional notes for each framework                       |

# **PROLOGUE**

This thesis examines gem5-based and gem5-compatible simulation frameworks in the context of modern computing. It aims to evaluate these tools in relation to heterogeneous SoC designs, offering a comprehensive understanding of their role in contemporary computer architecture. The work is rooted in both technical analysis and academic inquiry, reflecting the broader pursuit of knowledge within the academic community.

#### 1. INTRODUCTION

# 1.1 Overview of the importance of accelerators in modern computing

In the dynamic landscape of modern computing, the rapid evolution of System-on-Chip (SoC) designs underscores the indispensable role of specialized hardware accelerators, which, meticulously crafted for specific computational tasks, stand as pivotal components driving the performance and functionality of modern architectures [13]. Unlike general-purpose processors, accelerators are tailored to execute specific workloads efficiently, ranging from complex scientific simulations to data-intensive algorithms [33].

As applications and workloads diversify, the demand for optimized computational solutions intensifies. Herein lies the significance of accelerators within the intricate field of modern computing. They serve as dedicated engines, fine-tuned to excel in particular tasks, thereby unlocking unparalleled performance gains and energy efficiency. In the quest for enhanced computational capabilities, SoC designs increasingly integrate domain-specific accelerators (DSA), ushering in an era where customization and specialization become paramount.

However, the integration of accelerators introduces a complex interplay of architectural elements, necessitating sophisticated simulation frameworks for thorough evaluation and design space exploration. This study deepens within the critical task of assessing the variety of gem5-based simulation frameworks, which are inherently designed to aid in understanding the functionality and performance of heterogeneous architectures incorporating domain-specific accelerators. Gem5 [2], a well-established open-source microarchitectural simulator, emerges as a linchpin, providing a flexible and extensible platform for computer architects and developers to explore the intricate nuances of these specialized hardware components.

By seamlessly integrating DSAs into heterogeneous SoC designs, designers can tailor their architectures to optimize performance for specific workloads. This customization not only enhances computational efficiency but also contributes to a reduction in power (and energy) consumption and overall area utilization [34]. The intersection of accelerators and SoC designs encapsulates a transformative paradigm in computing, where adaptability and specialization converge to meet the evolving demands of diverse applications.

In essence, this study embarks on an exploration of the symbiotic relationship between accelerators and SoC designs. It scrutinizes the intricate balance between performance gains and architectural complexities, shedding light on the imperative need for efficient simulation frameworks. Through this perspective, the thesis highlights the importance of accelerators in modern computing, showing how they drive innovation in the field.

### 1.2 The significance of having a framework for designing and evaluating accelerators

In heterogeneous computing, dedicated frameworks for modeling and validating accelerator designs are paramount, particularly as System-on-Chip designs rapidly evolve. These frameworks are crucial for several reasons [13][31]:

- Complexity Management: Modern SoCs incorporate a variety of components, including CPUs, GPUs, and specialized accelerators, each with unique performance and energy characteristics. A structured framework aids in managing this complexity, allowing designers to simulate and analyze the behavior of these components in a unified environment.

- Domain-specific Acceleration: As computing demands diversify across applications like machine learning, image processing, and scientific simulations, the need for accelerators optimized for specific tasks has grown. Dedicated simulation frameworks enable the exploration of novel accelerator designs before committing to expensive fabrication processes.

- Integration Challenges: Integrating accelerators into heterogeneous architectures

presents challenges, including memory access patterns, data movement, interconnects

and communication with general-purpose processors. Frameworks that model these

aspects can help identify bottlenecks and optimize system architecture for balanced

performance and energy efficiency.

- Performance Validation: Through simulation, designers can validate the expected performance improvements offered by accelerators within the context of a full system. This is critical for ensuring that the inclusion of an accelerator leads to tangible benefits under realistic workloads.

- Rapid Iteration for design space exploration: Dedicated frameworks support rapid prototyping and iteration of accelerator designs, enabling a more agile development process. Designers can quickly assess the impact of changes to architecture, algorithms, or system integration strategies.

At the forefront of these simulation frameworks stands gem5, an open-source CPU simulator widely adopted for its flexibility and extensibility [2]. This transformative capability aligns with the ever-growing demand for specialized solutions in the face of diverse computational workloads. The primary function of a simulation framework is to create a virtual environment that emulates the intricacies of real-world scenarios. The framework serves as a sandbox, facilitating the exploration of diverse architectural parameters and configurations.

A major benefit of using a simulation framework is the broad early design space exploration using thorough evaluation of various metrics, including simulation output results, efficiency, configurability, and ease of use. These metrics contribute to a nuanced understanding of how well a framework can accurately model and emulate heterogeneous SoC designs

featuring domain-specific accelerators. Simulation frameworks play a crucial role in evaluating the impact of configuration choices and modeling techniques within gem5 on overall simulation performance. This investigation becomes vital in the ongoing efforts to design efficient simulation methodologies for next-generation SoC architectures. Understanding the balance between configurability and performance is paramount for achieving optimal results in accelerator design and integration.

The challenges associated with incorporating different domain-specific accelerators into simulation frameworks are also explored in this context. Addressing issues such as integration SoCs and optimization performance is crucial for ensuring that the simulated environment accurately reflects the expected behavior of accelerators in real-world scenarios. These challenges underscore the nuanced nature of accelerator integration and the importance of a robust simulation framework in overcoming hurdles in the design and evaluating phase.

In the culmination of this research, specific gem5-based frameworks, namely gem5-Aladdin and gem5-SALAM, take center stage in the demonstration of metric outcomes. Distinguished by their user-friendly nature, these frameworks showcase how the choice of a simulation tool can impact the ease with which designers and researchers navigate the complexities of heterogeneous SoC designs.

In conclusion, the significance of having a framework for designing and evaluating accelerators extends beyond mere technical functionality. It encapsulates a paradigm shift in the approach to SoC evolution, providing a structured pathway for developers to innovate, optimize, and adapt to the ever-changing demands of modern computing. A robust simulation framework is not just a tool it is a catalyst for progress, empowering designers to chart the course of next-generation SoC architectures with precision and efficiency.

# 2. BACKROUND AND SIMULATION FRAMEWORKS ANALYSIS

In the domain of heterogeneous SoC, five frameworks, namely, gem5-Aladdin [32], SMAUG [35], gem5-SALAM [28], gem5-X[24,25], and MAESTRO[17] have emerged as prominent gem5-based simulation frameworks that provide valuable tools for modeling and evaluating domain-specific accelerators integrated to a host CPU. These frameworks offer a range of features and capabilities to support the design and optimization of accelerators. The thesis examines their architectural aspects, similarities, differences, advantages, disadvantages, and the functionalities they support.

# 2.1 gem5-Aladdin

gem5-Aladdin stands out for its integration with the Aladdin framework [37], enabling cyclelevel simulation and in-depth analysis of accelerators [32]. It offers a comprehensive modeling infrastructure and supports the evaluation of accelerator performance, power consumption, and area characteristics. gem5-Aladdin creates a unified environment for accelerator simulation within a gem5-based SoC architecture. The gem5 simulator provides the system-level context, modeling the various components of the SoC such as Processing Units like ARM, x86, MIPS, RISC-V, and SPARC, while the Aladdin framework specializes in modeling and analyzing domain-specific accelerators including those for machine learning, graphics, and custom digital signal processing tasks [2]. It allows for cycle-level simulation of these accelerators, providing insights into their performance, power consumption, and area (PPA) metrics within the context of the larger system simulated by Through synchronization mechanisms. gem5-Aladdin enables communication and information exchange between the gem5 simulator and the Aladdin framework, which allows for capturing fine-grained details of accelerator behavior.

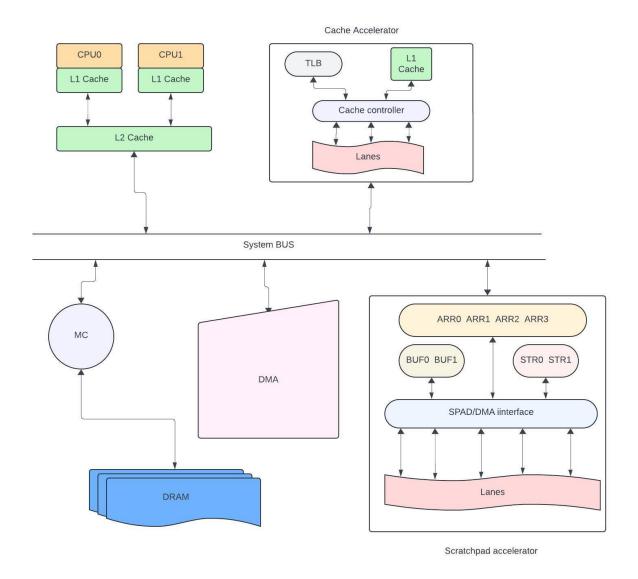

Data movement that is not effectively managed or accounted for in the system can consume a substantial part of the overall runtime, making the use of highly parallel datapaths redundant. Understanding the impact of emulation effects on accelerator behavior necessitates simulation infrastructures capable of modeling these heterogeneous systems. gem5-Aladdin addresses this need by modeling interactions between accelerators and CPUs, Direct Memory Access (DMA), hardware-managed caches, and virtual memory. Each of these features has implications for the behavior and performance of the accelerators. For example, Figure 1 illustrates an example of a System on Chip (SoC), featuring general-purpose cores, memory controllers, a DMA engine, and various types of fixed-function accelerators, all interconnected via the system bus.

Figure 1: Example of a System on Chip (SoC)

The gem5-Aladdin framework allows accelerators to utilize the DMA engine in gem5 by inserting special function calls for data loading and storing. These calls are recognized as DMA operations by Aladdin, which then communicates with the gem5 DMA engine. An analytical model is integrated into the DMA engine to handle cache flush and invalidation latency. gem5-Aladdin effectively models a wide range of accelerator workloads, including system-level considerations, without modifying gem5's cache models. The paper discusses the design considerations when choosing between a DMA- or cache-based memory system for an accelerator, evaluating the performance of both approaches. It emphasizes the

importance of considering system-level effects, such as data movement, in accelerator design to achieve optimal performance.

The Aladdin accelerator simulator plays a crucial role in this research by modeling the power, performance, and cycle-level activity of standalone, fixed-function accelerators without the need to generate register transfer level (RTL) designs. It operates as a tracebased accelerator simulator, profiling the dynamic execution of a program and constructing a dynamic data dependence graph (DDDG) as a dataflow representation of the accelerator. The DDDG comprises LLVM IR instructions as vertices, with edges denoting true dependencies between operations. Aladdin employs common accelerator design optimizations and schedules the graph for execution through a breadth-first traversal, while considering user-defined hardware constraints. However, it is important to note that Aladdin solely focuses on the standalone datapath and local memories of accelerators. It assumes that all data has been preloaded into the local scratchpads, omitting the modeling of any interactions between accelerators and the larger system to which they belong. Scratchpad memory is a type of on-chip memory that does not employ automatic data caching mechanisms. Instead, data management (loading and eviction) is explicitly controlled by the software or hardware designer. This allows for more predictable memory access times since the latency is consistent and does not depend on the cache state or replacement policies. Scratchpads are typically found in systems where timing predictability and efficiency are paramount, such as in real-time systems or in the domain-specific accelerators that Aladdin models. Preloading data into local scratchpads is a critical strategy in the design of hardware accelerators, like those modeled by Aladdin, due to several compelling benefits it offers in terms of performance, energy efficiency, and predictability. Scratchpad memory (SPM) is a form of statically managed memory that differs from the traditional cache in several keyways, making it especially suited for the deterministic workloads often encountered in specialized computing tasks [13]. Figure 2 shows a shared scratchpad memory. The benefits of preloading data into local Scratchpads are performance prediction, energy efficiency, reduced latency, the avoidance of Cache Coherence Overheads and the Customization to Workload [31]. Please note that the proportions of the shape are not accurate and the figure serves only as an indicative representation.

Figure 2: Shared Scratchpad Memory

While gem5 offers support for a wide range of architectures, gem5-aladdin provides support exclusively for the x86 architecture. All the experiments that were conducted using gem5-Aladdin were in syscall emulation mode, which adequately captures the effects of system-level considerations on performance and power usage and offers the advantage of faster simulation compared to full-system simulation. Full-system simulation, which models operating system effects, was not utilized due to its scope limitations. However, certain interactions with the operating system, such as device driver to hardware interactions, are supported by the simulator through real hardware measurements and analytical inclusion in the models.

The design of gem5-Aladdin is centered around the concept of bridging the gap between hardware and software in heterogeneous systems. This integration is crucial as specialized hardware accelerators are increasingly being used alongside traditional CPU cores. gem5 offers a detailed simulation of processor cores, memory systems, and system-level architecture, providing a realistic environment for architectural exploration. Aladdin complements this by offering precise modeling of accelerators, focusing on their power consumption and performance metrics.

# **Unique Features and Capabilities:**

- **Co-Simulation Environment**: gem5-Aladdin co-simulates both CPU and hardware accelerators, supporting x86 and syscall emulation. This is pivotal in analyzing system interactions, particularly for compute-intensive functions.

- Flexibility and Customization: Based on the gem5 framework, which supports various ISAs including Alpha, ARM, SPARC, MIPS, POWER, RISC-V and x86, it allows researchers to integrate custom accelerator models for specific research needs.

- In-Depth Power and Performance Analysis: Aladdin's integration within gem5 provides detailed insights into both power usage and performance aspects of SoC designs, critical for optimizing systems for energy efficiency and computational effectiveness.

- User Accessibility: Despite its sophistication, gem5-Aladdin is designed with a user-friendly interface, making it accessible to a wide range of users, from academic researchers to industrial practitioners.

### **Diverse Application Scenarios:**

- In the domain of Artificial Intelligence, gem5-Aladdin plays a crucial role. This tool

enables the simulation and evaluation of different hardware accelerators, which are

essential for running Al algorithms. It assists in optimizing these systems for

enhanced speed and power usage efficiency.

- Exploring Heterogeneous Computing: The framework is ideal for researching heterogeneous computing systems that combine CPUs with specialized accelerators.

Researchers can experiment with different configurations to achieve optimal performance and energy consumption ratios.

- Big Data Processing: For big data applications, gem5-Aladdin can simulate how accelerators interact with memory systems to optimize data movement between global memory and local memory. This provides critical insights into designing accelerators with specialized interfaces for efficient bulk data transfers, especially in workloads like memcached[40] and database partitioning[41], where large datasets need to be processed efficiently.

The significance of gem5-Aladdin in both academic and industrial contexts is underscored by numerous high-impact publications and citations. For example, Xi et al. in [35] discuss the broader implications of accelerator-focused simulations in emerging computing paradigms. Also, Binkert et al. in [2] emphasize its role in the broader context of computer architecture research. These works illustrate the widespread adoption and importance of gem5-Aladdin in advancing the field of SoC design and architectural exploration. The framework's ability to simulate complex interactions between different system components and its detailed power-performance analysis capabilities make it an indispensable tool in the field.

# **2.2 SMAUG**

SMAUG builds on gem5-Aladdin, which employs a preRTL approach to model the power, performance, and area of accelerator designs. Studying end-to-end behavior in simulation is crucial for designing DNN-centric SoCs, yet no DNN framework supports fast, early-stage design exploration. SMAUG addresses this gap as the first architecture-simulation friendly deep learning framework that runs in a user-level simulator. Its compatibility with gem5-

Aladdin allows for flexible SoC and memory topologies without requiring RTL for design space exploration, simplifying the research and development process.

In this paper, the authors introduce SMAUG, a gem5-based framework and the first deep neural network (DNN) framework specifically designed for the simulation of end-to-end deep learning applications. SMAUG offers a range of capabilities for evaluating DNN workloads, including diverse network topologies, easy accelerator modeling, and seamless system-on-chip integration. The paper emphasizes the importance of evaluating the full-stack performance of hardware-accelerated computing tasks like neural network inference, highlighting the need for suitable research infrastructure to address components such as data transformation and movement costs and software framework overheads.

To address the above challenges, the authors developed SMAUG, a DNN framework that can be simulated within a cycle-level SoC simulator. They demonstrate how SMAUG can optimize end-to-end performance for a wide range of DNNs by leveraging various strategies, such as optimizing the SoC-to-accelerator interfaces, exploiting multi-accelerator systems, and optimizing the software stack.

SMAUG's "end-to-end" definition encompasses the entire process, from the computation of the result to the CPU receiving the inference request. The authors break down the overall time spent on accelerator computing, data transfer to/from scratchpads, and CPU time spent in the software stack. They emphasize the importance of studying end-to-end behavior in simulation to holistically design DNN-centric SoCs, especially during the early stages of hardware design.

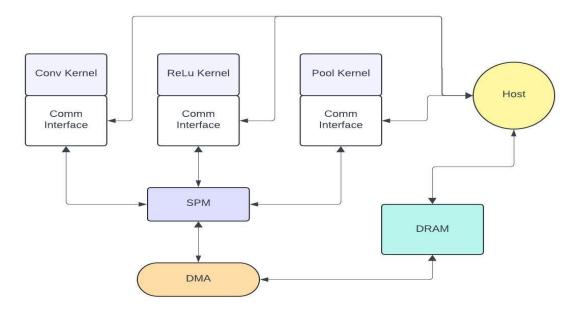

Figure 3 depicts the execution flow and the architecture of SMAUG. This framework consists of three major components: a Python frontend for network configuration, a C++ runtime for execution management, and a backend comprising a set of hardware-accelerated kernels. The accelerated kernels can be modeled using either Aladdin or native gem5 simulation objects, offering flexibility and control to the user. SMAUG is compatible with LLVM-based toolchains required by the Aladdin accelerator simulator and exposes gem5 APIs, with improvements made to support C++ binaries, multi-threaded workloads, and sampling.

Figure 3: Smaug's execution flow

Efficient tiling schedules, maximizing data reuse, and minimizing data movement, are critical for achieving high-performance DNN computations. SMAUG supports different tiling strategies, where changing the tiling shape may impact overall runtime, particularly for operations relying on data reuse. Accelerators can be modeled in SMAUG using Aladdin, which supports various complex hardware constructs. However, from SMAUG's perspective, all accelerators export a common interface defined by dataflow, minimum tile shape, and maximum tile size.

To distribute work across multiple accelerators, SMAUG implements an accelerator worker pool and a command queue per accelerator. Tasks are assigned to the next available accelerator in the pool, while unsupported operators are executed on the CPU. SMAUG also supports dividing CPU work across multiple threads, utilizing a thread pool with round-robin scheduling. The gem5-Aladdin API exposes accelerators as threads, simplifying concurrent execution management.

SMAUG provides features such as a Python API for network configuration, support for common operators and network topologies, plug-and-play hardware accelerator implementations, and a complete software stack managing operator tiling, multi-accelerator and multi-thread scheduling, synchronization, and more. The framework enables researchers to evaluate different accelerator and SoC designs, facilitating hardware-software co-design and end-to-end system studies.

The paper presents several case studies showcasing SMAUG's capabilities and insights gained from end-to-end DNN studies. These case studies demonstrate methods to improve overall performance in various DNNs, including:

- **SoC-Accelerator Interfaces**: Enhancing CPU-accelerator coupling to achieve significant speedup and energy savings.

- **Tile-Level Parallelism**: Utilizing multiple independent accelerators to boost compute and data-transfer throughput.

- Multithreading for Data Preparation: Implementing multithreading in the software stack to optimize data preparation time, resulting in improved overall performance.

- **Optimizing Data Transfers**: Using a coherent interface between the accelerator and CPU to enhance data transfer speeds.

- **Software Tiling Transformations**: Reducing CPU processing time through optimized tiling techniques to improve inference latency.

Additionally, the integration of SMAUG with a state-of-the-art camera pipeline in Halide demonstrates its ability to model complex applications and identify opportunities for more efficient system design.

SMAUG offers an easy pathway for implementing new hardware accelerator models and studying end-to-end system interactions. It simplifies the development of new hardware models and enables researchers to focus on their specific interests. The framework supports user-level simulators, such as gem5 syscall-emulation mode, reducing simulation time with

sampling and handling incomplete system call emulation. SMAUG also supports multithreading without a thread scheduler, implementing a custom thread pool.

At its core, SMAUG is a versatile and efficient platform for simulating and evaluating SoCs. It supports exploring complex architectures with CPUs, GPUs, and specialized accelerators, enabling in-depth analysis of system performance and interactions between components.

# Unique Aspects of SMAUG:

- Heterogeneous System Modeling: One of the standout features of SMAUG is its

ability to model and simulate heterogeneous computing systems. This includes a

detailed representation of different processing elements, which is vital in an era where

SoCs increasingly rely on a mix of general-purpose processors and specialized

accelerators for tasks like machine learning and data processing.

- Extensibility and Flexibility: SMAUG is designed with extensibility in mind, allowing researchers to add custom models or modify existing ones. This level of customization is crucial for simulating emerging technologies and architectural innovations in SoC design.

- Performance and Power Efficiency Analysis: SMAUG provides detailed insights into both the performance and power efficiency of SoC designs. This dual focus is essential in optimizing SoCs for a balance between computational speed and energy consumption, particularly in applications like mobile devices and high-performance computing.

- Integration with Real-World Workloads: SMAUG can integrate and run real-world workloads, which allows for more realistic and practical simulation results. This feature is particularly useful for evaluating the real-world performance implications of different SoC designs.

SMAUG has been employed in various scenarios, reflecting its versatility and effectiveness in SoC simulation:

- Machine Learning Systems: SMAUG has been instrumental in simulating and optimizing SoC designs that include machine learning accelerators. This is particularly important for understanding the performance characteristics of these systems under different workload conditions.

- Energy-Efficient Computing: For applications where energy efficiency is paramount, SMAUG provides valuable insights into how different SoC components can be optimized for lower power consumption without compromising performance.

- High-Performance Computing: SMAUG is designed to handle and optimize complex SoCs in scenarios that demand high computational throughput. It ensures efficient modeling in high-performance environments, enabling the development of more powerful and efficient computing systems.

### 2.3 gem5-SALAM

gem5-SALAM, which stands for 'System Architecture for LLVM-based Accelerator Modeling,' is a system architecture that moves beyond traditional trace-based simulation. While not an event-driven simulator, it significantly differs from conventional trace-based approaches due to its architecture and its ability to model multiple accelerators within clusters. Trace-based simulators often lack the necessary mechanisms for efficient simulation, especially in complex multi-accelerator environments. In contrast, gem5-SALAM provides a non-trace-based simulation environment, designed to support scalable modeling of custom hardware accelerators integrated into the gem5 framework.

One of the key strengths of gem5-SALAM is its ability to enable inter-accelerator pipelining, which results in substantial improvements in end-to-end execution compared to baseline models. This feature, along with its capability to simulate various scenarios of multi-accelerator integration, makes gem5-SALAM uniquely suited to accurately model complex accelerator interactions. By overcoming the limitations of trace-based methods, gem5-SALAM offers a more dynamic and efficient simulation environment, particularly in advanced system architectures.

The system architecture has been designed with long-term scalability in mind and is fully compatible with the gem5 system framework. It offers a modular communication interface and a flexible memory hierarchy, seamlessly integrated into the gem5 ecosystem. This integration significantly simplifies the design and modeling of accelerators for emerging applications.

According to the paper, gem5-SALAM is considered one of the most efficient simulators, as evidenced by the comparative tables below. However, while it performs exceptionally well in most scenarios, there may be cases where a different simulation approach could better meet specific needs or requirements, depending on the unique demands of the system being modeled. Despite these exceptions, the paper highlights gem5-SALAM's strengths, including its capabilities for cycle-level profiling and comprehensive full-system design space exploration in accelerator-rich environments.

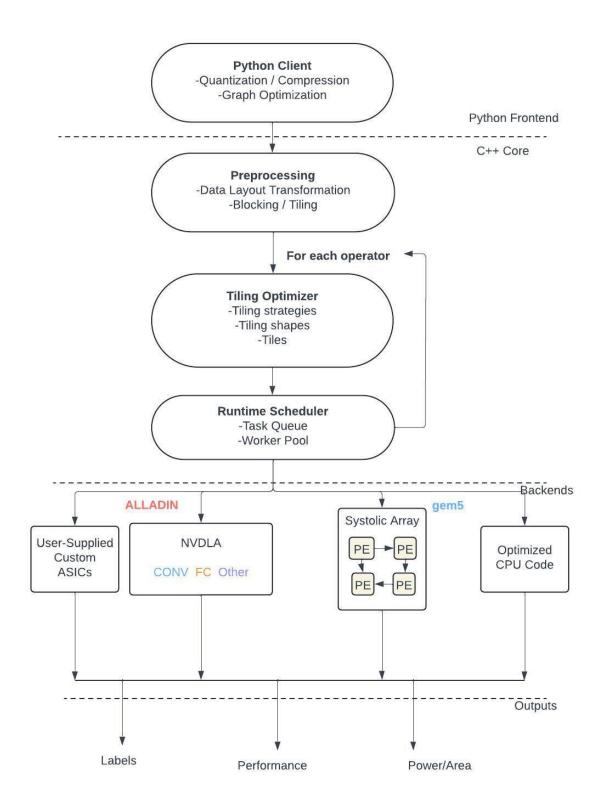

gem5-SALAM's LLVM-based simulation platform allows for scalable simulation of accelerator-rich systems on SoCs. Unlike the existing platforms mentioned in this thesis, gem5-SALAM introduces a new Sim-Object as the run-time engine within the gem5 ecosystem, enabling flexible full-system simulation with multiple hardware accelerators. Users can leverage unmodified LLVM code generated from any language along with their desired accelerators and system configurations to automatically create a full system simulation. Figure 4 includes the Accelerator Model Generation process, showcasing its role within the overall system architecture. Furthermore, gem5-SALAM demonstrates significant advantages in supporting full system simulations and design space exploration for both single and multiple accelerators with varying design configurations.

Figure 4: Accelerator model creation

gem5 currently supports various system element models, such as memory, CPUs, GPUs, and buses. However, it lacks models for application-specific hardware accelerators. To address this limitation, researchers have integrated application-specific accelerator modeling into gem5 through gem5-SALAM. This system architecture introduces accurate modeling of the datapath structure, area, and static leakage power based on algorithmintrinsic characteristics exposed by LLVM. Additionally, gem5-SALAM incorporates cycleaccurate modeling of dynamic power consumption and timing through a dynamic LLVMbased runtime execution engine, enabling precise simulation of runtime-dependent accelerators and their interactions with other system elements. The gem5-SALAM also separates the datapath and memory infrastructure, allowing independent tuning and design space exploration, and provides a flexible system integration that directly exposes accelerator models to other system elements, fostering complex inter-accelerator communication and synchronization using pre-existing gem5 simulation constructs. The general-purpose C++/Python API for accelerator modeling in gem5-SALAM decouples computation from system communication, enabling customization and specialization to cater to various user modeling needs.

The architecture of gem5-SALAM is notable for its hybrid approach, connecting traditional CPU simulation with advanced accelerator modeling. Its core components include:

- Core gem5 Simulator: Forms the primary platform for simulating the CPU aspects of SoCs.

- Co-Simulation Capabilities: Enables simultaneous simulation of CPU components and any accelerators, essential for understanding interactions and the collective impact of SoC components.

- Modularity and Extensibility: Emphasizes modularity and extensibility, allowing for the addition of new models and adaptations to existing ones, accommodating diverse SoC designs.

gem5-SALAM brings significant enhancements to SoC simulation:

- Enhanced Precision in Accelerator Simulation: Improves accuracy and detail in simulating accelerators.

- Comprehensive System Analysis: Provides insights into interactions among SoC components and their influence on performance.

- Energy and Performance Optimization: Supports analysis and optimization of energy efficiency and computational performance.

- Facilitating Research and Innovation: Serves as a tool for researchers and developers, fostering innovation in SoC designs.

- Real-World Scenario Simulation: Simulates real-world scenarios and workloads to evaluate SoC performance under realistic conditions.

gem5-SALAM represents a significant advancement in SoC simulation, combining gem5's robust capabilities with innovative features. This integration enhances simulation accuracy

and efficiency, particularly for complex computational applications, meeting the evolving needs of modern SoC designs.

# 2.4 gem5-X

Gem5-X is a system-level simulation framework built upon gem5, designed to optimize many-core systems in terms of performance and power efficiency. This framework facilitates the identification of bottlenecks and the evaluation of architectural extensions, such as incache computing and 3D stacked High Bandwidth Memory (HBM), which are crucial for enhancing system-level architectural innovations [2]. Additionally, gem5-X has made strides in enhancing simulation speed and efficiency. By optimizing simulation algorithms and implementing more efficient data structures, it has significantly reduced the time required to model complex systems, a vital feature for conducting large-scale experiments and simulations.

Figure 5: Gem5-X's platform

The gem5-X platform, as shown in Figure 5, is also designed for architectural exploration and optimization of real-time video analytics applications. It simulates an ARMv8 64-bit ISA

with Linux and includes application profiling via gperf to identify bottlenecks. The platform supports 9P over virtual IO for efficient file sharing and allows for the simulation of heterogeneous architectures with both in-order and out-of-order cores. It supports core clustering, custom accelerators, ISA extensions, and large-scale many-core simulations, accommodating up to 256 cores. These features make it suitable for high-performance and energy-efficient processing tasks.

To achieve efficient energy utilization and superior performance, there's a need for a system-level simulator capable of simultaneously executing multi-threaded applications on many-core systems. gem5-X, described as a "gem5-based full-system simulator with architectural eXtensions," offers a versatile platform for fast profiling, architectural exploration, and the characterization of performance-power aspects of novel architectural concepts. It seamlessly integrates applications running on modern Linux operating systems.

With the increasing importance of efficient on-chip communication in multicore processors and SoCs, gem5-X's improved models for simulating Convolutional Neural Networks (CNNs) are particularly noteworthy, offering deeper insights into the performance and scalability of these systems.

The integration capabilities of gem5-X with other simulation and modeling frameworks are where it truly stands out. For instance, its ability to integrate with power and energy modeling tools like McPAT [38] enables the simultaneous analysis of both performance and power consumption (thus also energy), a critical aspect in the design of energy-efficient computing systems. Moreover, gem5-X supports heterogeneous architectures, such as in-order and out-of-order (OoO) cores, as long with custom accelerators like an in-cache computing engine [42]. Additionally, it supports heterogeneous memory types, including DDR4 and 3D stacked HBM2, enabling the simulation of highly heterogeneous systems with a full Linux stack. To the best of available knowledge, this is the first work simulating a complete Linux-based system with clustered heterogeneous compute cores (in-order and OoO) and an incache computing engine, along with 3D stacked HBM2 memory.

In the field of AI and machine learning, gem5-X's compatibility with various machine learning frameworks is a boon for researchers and developers. This feature is instrumental in simulating and evaluating the performance of AI algorithms on different hardware configurations, particularly for hardware accelerators designed for machine learning applications. Additionally, gem5-X's support for external input/output (I/O) models enhances its capability to conduct comprehensive system-level simulations that include various I/O devices and peripherals.

In summary, gem5-X emerges as an indispensable tool in the field of computer architecture simulation. Its comprehensive enhancements in processor and memory modeling, combined with improved simulation efficiency and extensive integration capabilities, render it a vital resource for researchers and developers. Whether it's exploring new processor architectures, digging into the intricacies of memory systems, or integrating complex

hardware and software components, gem5-X provides a robust and versatile platform for advancing the frontiers of computing technology.

#### 2.5 MAESTRO

MAESTRO, short for "Modeling Accelerator Efficiency via Spatio-Temporal Reuse and Occupancy," introduces a comprehensive framework for enhancing the design and optimization of Deep Neural Network (DNN) accelerators. It begins by offering a set of datacentric directives, which provide a succinct and compiler-friendly means to describe DNN dataflow patterns. These directives are instrumental in identifying and harnessing various forms of data reuse, thereby leveraging hardware capabilities efficiently. The effect of different tiling strategies on overall operation, which can be harder to predict, can be estimated with analytical models like MAESTRO. While tiling strategy may have little impact on element-wise operations, it significantly affects operations where data reuse is critical, potentially altering runtime. gem5, compatible with these analytical models, provides an essential simulation environment for understanding such effects in accelerator design.

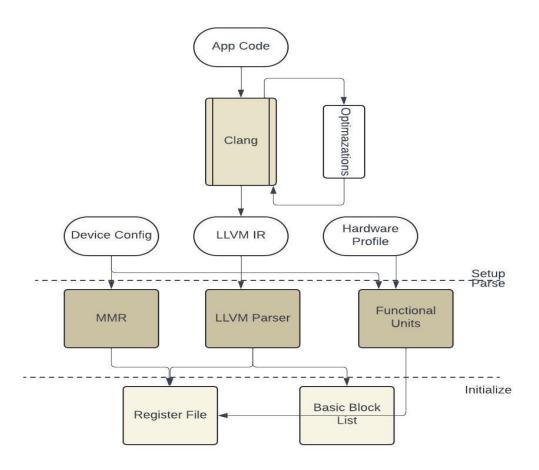

In the pursuit of achieving both high performance and energy efficiency within DNN accelerators (Figure 6), the optimization of dataflow is paramount. This optimization encompasses how DNN computations are scheduled and mapped across processing elements (PEs). MAESTRO recognizes that effective data reuse, such as maximizing data reuse within PEs and on-chip scratchpads, plays a pivotal role in this context. The energy costs associated with data movement are often more significant than computation costs, underscoring the critical importance of dataflow optimization.

Figure 6: Abstract parameterized DNN accelerator

MAESTRO introduces an analytical cost model that explores the intricate trade-offs inherent in dataflow design, particularly in the context of neural network (NN) architectures. NN architectures, which are fundamental to deep learning, consist of interconnected layers of nodes or neurons that process data through various transformations. These architectures can vary significantly in their structure, such as feedforward networks, convolutional neural networks (CNNs), and recurrent neural networks (RNNs), each having unique characteristics and computational requirements.

Unlike simulation-based approaches, MAESTRO does not rely on executing simulations to evaluate different design choices. Instead, it uses mathematical models to predict the performance, energy consumption, and resource utilization of different dataflow mappings on hardware accelerators [17]. This distinction is crucial for several reasons, including speed and scalability, insight and understanding, predictive capability, and focus on dataflow [13]. MAESTRO is a powerful tool that estimates various aspects, including execution time and energy efficiency, concerning both the DNN model and the hardware configuration. This means it analyzes how different designs of neural networks interact with the underlying hardware, optimizing for both the architecture of the neural network and the capabilities of the hardware, such as GPUs or TPUs.

Furthermore, the framework emphasizes the synergistic optimization of both hardware microarchitecture and the associated dataflows, which is a crucial objective for accelerator design. The term "dataflow" refers to the movement of data through the computational graph

of a neural network. Different dataflow strategies (e.g., streaming, batch processing, or pipelining) can significantly affect performance and efficiency. The microarchitecture, which includes aspects like memory hierarchy and processing units, influences how data is handled. MAESTRO explores how different ways of organizing dataflow can impact the hardware's performance, ultimately leading to more efficient designs.

By providing a structured mechanism for evaluating dataflow choices and their interplay with microarchitectural alternatives, MAESTRO offers a thorough understanding of these complex relationships. Key contributions include a data-centric notation for representing accelerator dataflows, facilitating insight into data mappings and reuses. Moreover, it introduces three transformations that encompass the complete spectrum of dataflow possibilities:

- Scheduling: This involves determining the order in which operations (like matrix multiplications or activations) are performed. Effective scheduling can minimize waiting times and improve resource utilization, ensuring that the processing units are kept busy.

- Tiling: Tiling breaks down large data sets or operations into smaller, manageable

pieces or "tiles." This technique helps improve data locality, allowing the hardware to

access data more efficiently and reducing memory access times, which is critical for

performance in large DNNs.

- Mapping: Mapping refers to the assignment of specific computations or data to particular hardware resources (like cores or memory banks). By strategically mapping operations to the right resources, MAESTRO can optimize performance, leveraging the unique strengths of the hardware.

MAESTRO's significance lies not only in its ability to identify data reuse opportunities but also in its practicality. It acknowledges that appropriate hardware support is essential for realizing these opportunities. Hardware communication types, such as multicast for input tensors and reduction for output tensors, are crucial considerations. For instance, multicast delivers the same data to multiple targets in either space or time, demanding specific network-on-chip structures or stationary buffers. Reduction, on the other hand, processes partial sums to generate final outputs.

MAESTRO aids in understanding the trade-offs between computational cost and performance. This understanding is essential in making informed decisions about the complexity and cost-effectiveness of the hardware design. For instance, a more complex dataflow strategy might offer better performance but could also lead to increased power consumption and chip area. MAESTRO provides the necessary analytics to balance these aspects effectively. Dataflow, in this context, refers to the pattern in which data is passed through the computational units of the accelerator [43][44]. Different dataflow strategies can lead to significant variations in performance, power consumption, resource utilization and neural network accuracy.

Moreover, MAESTRO allows designers to simulate and analyze these different strategies, providing a comprehensive view of their impact on the accelerator's efficiency. It offers insights into the optimal use of resources such as memory bandwidth and computational units, helping in designing accelerators that are both high-performance and energy-efficient. This aspect of MAESTRO is especially important in scenarios where power and resource constraints are critical, such as in mobile and edge computing devices.

One of the key applications of MAESTRO is in the design of neural network accelerators. These accelerators, which are specialized hardware designed to efficiently run neural network models, can greatly benefit from MAESTRO's analysis. For example, in designing accelerators for Convolutional Neural Networks (CNNs), MAESTRO can model different dataflow strategies and predict their impact on throughput and efficiency. This predictive capability was particularly relevant in the design of specialized hardware like Google's TPU (Tensor Processing Unit), which is optimized for tensor operations commonly found in neural networks.

In the realm of edge computing, where devices often operate under stringent power constraints, MAESTRO's role becomes even more critical. It assists in creating accelerators that are optimized for power efficiency while still delivering the necessary computational power. This is vital for applications like autonomous vehicles and Internet of Things (IoT) devices, where processing needs to be fast yet power-efficient.

In high-performance computing (HPC) environments, where processing large and complex datasets swiftly is a priority, MAESTRO contributes by aiding in the design of accelerators capable of handling such demanding workloads efficiently. It helps in reducing computation time and energy consumption, which are key considerations in HPC systems.

In summary, MAESTRO is indispensable for deep learning accelerator design, offering predictive analytics, resource analysis, and optimization capabilities crucial for advancing AI technologies.

# 2.6 Similarities

At their core, all these tools aim to advance SoC design and simulation. They are pivotal in analyzing and optimizing performance, energy efficiency, and resource utilization, which are critical aspects in the design of efficient and effective computing systems. They offer detailed simulation and modeling capabilities, enabling designers and researchers to gain in-depth insights into complex computing architectures. This common ground in functionality underscores their shared purpose in the field of computer architecture.

While these technologies share a common goal of advancing SoC simulation, their distinct features and focus areas set them apart from each other in significant ways:

#### gem5-Aladdin vs. SMAUG:

gem5-Aladdin: Tailored for co-simulation of CPUs and hardware accelerators, gem5-Aladdin excels in analyzing performance across various architectural designs and configurations. It integrates the gem5 simulator with Aladdin, focusing on the detailed simulation of SoC architectures.

SMAUG: Offers a broader platform for heterogeneous system simulation. While also supporting CPUs and accelerators, SMAUG is recognized for its versatility and wider applicability in simulating diverse systems and especially DNN.

# gem5-SALAM vs. MAESTRO:

gem5-SALAM: An extension of the gem5 simulator, gem5-SALAM specializes in cosimulating CPU components with advanced accelerators. It emphasizes system-level analysis, examining the interplay between different SoC components.

MAESTRO: Concentrates on dataflow efficiency within hardware accelerators. Its focus is on optimizing dataflow strategies, essential for high-efficiency accelerator design.

#### MAESTRO vs. SMAUG:

MAESTRO: Primarily focused on optimizing dataflow within specialized accelerators. It is highly effective for designs where dataflow efficiency is a key consideration.

SMAUG: More versatile in its application, SMAUG can handle a range of simulation scenarios, making it a go-to for diverse system simulations, including those with complex architectural requirements.

# gem5-SALAM vs. gem5-Aladdin:

gem5-SALAM: This framework extends gem5's capabilities to co-simulate advanced accelerators alongside CPUs, emphasizing comprehensive system-level analysis.

gem5-Aladdin: Specifically designed for detailed simulations involving CPU and accelerator co-operation, it is adept at exploring the performance impacts of different SoC configurations.

#### gem5-X vs. Others:

gem5-X: Distinguishes itself with broad enhancements to the original gem5 simulator. Its versatility extends to improved processor and memory modeling, along with enhanced simulation speed and efficiency. gem5-X is adaptable for a variety of simulation tasks, making it a versatile tool in SoC design.

In essence, while all these tools are geared towards advancing SoC design and simulation, their differences lie in their specific areas of specialization. gem5-Aladdin and SMAUG are more focused on the interaction between CPUs and accelerators, with the former providing a more specialized environment for this purpose, while the latter offers greater general applicability. gem5-SALAM and MAESTRO both explore the accelerator design, but from different angles – gem5-SALAM from a system-level perspective and MAESTRO from the standpoint of internal dataflow efficiency. gem5-X, meanwhile, serves as a more comprehensive extension of the gem5 simulator, enhancing its overall capabilities across a broader spectrum of architectural simulation tasks.

This comparative analysis underscores the importance of selecting the appropriate tool based on the specific requirements of a given simulation or design task, highlighting the specialized nature of these advanced SoC design and simulation frameworks.

#### 2.7 Architectural Details of Each Framework

#### 2.7.1 Framework Architectures

Focusing solely on the architectural analysis of the gem5-Aladdin framework:

- Co-Design Approach: The architectural foundation of gem5-Aladdin is built on the

principle of co-designing accelerator microarchitectures with their respective

systems. This approach is crucial for creating balanced and efficient designs,

especially given the complexity and diversity of hardware accelerators in modern

SoCs. The framework emphasizes the importance of considering data movement and

coherence management, which are often overlooked but significant in determining

the overall performance and efficiency of accelerators.

- Dynamic Interaction Simulation: At its core, gem5-Aladdin is designed to simulate the

dynamic interactions between accelerators and the broader SoC platform. This

aspect of the architecture is critical for accurately predicting the performance of

accelerators in real-world scenarios. By capturing these interactions, gem5-Aladdin

can provide more realistic and useful insights into the design and optimization of

accelerator microarchitectures.

- Aladdin as a Power-Performance Simulator: Aladdin, a key component of the framework, functions as a pre-RTL power-performance simulator. It is architecturally distinct in that it uses dynamic data dependence graphs (DDDG) to represent accelerators based on high-level language descriptions of algorithms. This eliminates the need for low-level RTL generation, streamlining the design process. The architectural design of Aladdin allows for the application of optimizations and constraints to the DDDG, resulting in a realistic model of accelerator activity that is validated for performance, power, and area.

- Integration Challenges and Solutions: The architecture of gem5-Aladdin addresses the challenges in current SoC designs, which often lack higher-level coordination and

- optimization between various components such as general-purpose cores, accelerators, and shared resources. The framework advocates for a design methodology that facilitates broader design space exploration of customized architectures, considering these elements in an integrated manner.

- In essence, the architectural analysis of the gem5-Aladdin framework reveals a sophisticated and forward-thinking approach to SoC design. It underscores the importance of co-design and system-level consideration in developing efficient and effective hardware accelerators, marking a significant advancement in the field of computer architecture.

The SMAUG framework represents a significant advancement in the field of deep learning (DL) research, particularly in hardware acceleration for deep neural networks (DNNs). Its architecture is designed to address the challenges in studying end-to-end DNN performance during early-stage design, especially before Register-Transfer Level (RTL) development. SMAUG stands out for its capability to simulate deep learning applications in a full-stack manner, from hardware accelerators to software frameworks.

## As of its keys features:

- Integration with gem5-Aladdin: SMAUG is closely integrated with gem5-Aladdin, a System on Chip simulator. This integration supports the modeling of complex heterogeneous SoCs, making SMAUG the first architecture-simulation friendly deep learning framework. This design enables rapid evaluation of different accelerator and SoC designs, and facilitates hardware-software co-design.

- Python API and C++ Runtime: The framework is divided into three major components:

- O A Python frontend for network configuration, which allows users to build networks using a declarative style. This part handles input and weights data, and the configuration of accelerated kernels.

- O A C++ runtime manages the execution flow, handling the operation of the deep learning models.

- O A backend consisting of hardware-accelerated kernels, which can be modeled using Aladdin or as native gem5 simulation objects.

- Tiling Optimizer and Scheduler: SMAUG features a tiling optimizer that computes the

best tiling shapes for each operation, ensuring optimal use of the accelerator's

compute and memory resources. The scheduler then prepares and dispatches these

tiles to the appropriate compute elements, managing multiple accelerators and

threads efficiently.

- Flexible Backend Implementation: The backend supports a range of operations required by DNN models, including convolutions and inner products. The models for these operations can be written using Aladdin or as native gem5 objects. This flexibility allows users to implement new hardware accelerator models easily into the framework.

- Sampling Support with Aladdin: SMAUG extends Aladdin to include a new API for sampling at the per-loop level. This feature allows for efficient simulation of DNNs, reducing the time required for forward pass simulation significantly while maintaining accuracy.

- Efficient Operation within Simulator Limitations: SMAUG is designed to operate effectively within the limitations of user-space simulators. It minimizes its interactions with the operating system, running as a single C++ binary and managing its thread operations within these constraints.

- Power and Area Modeling: The framework also includes capabilities for power and area estimation. This is done by characterizing various 16-bit functional units and modeling accelerator local scratchpads, among other components.

- Case Studies and Performance Optimization: SMAUG demonstrates its utility through various case studies. These studies show how the framework can optimize data transfers, exploit tile-level parallelism in multi-accelerator systems, and improve tiling transformations in software. These optimizations significantly speed up overall inference latency.

The architecture of SMAUG is carefully designed to bridge gaps in deep learning research infrastructure, particularly in the early stages of hardware-software co-design. Its integration with gem5-Aladdin, Python API, tiling optimizer, flexible backend, and efficient operation within simulator limitations collectively make it a powerful tool for DNN researchers. The framework's ability to simulate and optimize end-to-end DNN performance makes it a significant contribution to the field of deep learning and hardware acceleration.

The MAESTRO framework is a highly specialized tool designed for understanding and optimizing dataflows in deep neural network (DNN) accelerators. Its architecture and implications can be summarized as follows:

- Data-Centric Approach: MAESTRO employs a data-centric approach for representing various accelerator dataflows, emphasizing data mappings and reuses as primary elements. This contrasts with traditional compute-centric notations, enabling a more precise analysis of data reuse and movements across the accelerators.

- Analytical Cost Model: It introduces an analytical cost model named MAESTRO (Modeling Accelerator Efficiency via Spatio-Temporal Reuse and Occupancy) for estimating the cost-benefit tradeoffs of a dataflow, including execution time and energy efficiency. This model is essential for evaluating different design choices in terms of performance and energy usage.

- Dataflow Optimization: The framework focuses on optimizing dataflow for DNN accelerators. The performance and energy efficiency of these accelerators heavily depend on how the computations are scheduled and mapped across processing elements (PEs). MAESTRO helps in understanding and optimizing these aspects for improved efficiency.

- Reuse Taxonomy and Hardware Implementation: MAESTRO identifies and utilizes various data reuse opportunities, like multicasting and reduction, to enhance the efficiency of DNN accelerators. It also provides insights into suitable hardware implementations for these reuse strategies, helping in the design of more efficient accelerators.

- Key Directives and Clustering: The architecture involves key directives like spatial

and temporal mapping, data movement order, and clustering. These directives help

in organizing data flows and processing across the accelerator, impacting how

effectively the DNN computations are executed.

- Dataflow Transformations: MAESTRO encompasses transformations such as scheduling, tiling, and mapping, providing a comprehensive framework for understanding all aspects of dataflows in DNN accelerators.

In summary, MAESTRO provides a sophisticated framework for DNN accelerators, focusing on data-centric analysis and optimization of dataflows, which is crucial for achieving high performance and energy efficiency in DNN computations.

One of the key features of gem5-SALAM is its "execute-in-execute" LLVM-based model. This model is distinct from traditional simulation methods in that it allows for a more integrated and efficient way of simulating hardware accelerators. The use of LLVM (Low Level Virtual Machine) as the basis for modeling ensures that gem5-SALAM is adaptable and capable of simulating a wide range of hardware accelerators in a more realistic environment. This adaptability is crucial for modern system architectures, which are increasingly reliant on custom hardware accelerators to meet the demands of advanced computational tasks.

The architecture of gem5-SALAM necessitates specific requirements, including dependencies on gem5 and LLVM-9 or newer versions. The setup involves the use of a front-end LLVM compiler for the preferred development language, like clang for C, which facilitates the integration of the model with the gem5 environment. This integration is a critical aspect of the framework, as it enables the seamless interaction between the simulated hardware accelerators and the rest of the system modeled in gem5.

In the gem5-SALAM framework, accelerators are constructed by associating their LLVM Intermediate Representation (IR) with an LLVMInterface. This interface is then connected to the desired CommInterface in the gem5 memory map. This approach underscores the framework's flexibility and its ability to cater to a wide range of system configurations and requirements.

This framework represents a significant step forward in the field of system architecture and hardware accelerator modeling, offering a more versatile and efficient approach to simulation that can adapt to the rapidly evolving demands of modern computing systems.

The Top accelerator within the gem5-SALAM framework is an essential component designed to manage and control the operations of specialized hardware accelerators. It functions as the primary interface between the system's main processing unit and the

specialized hardware, orchestrating data flow and control signals to ensure efficient and synchronized operations.

In the context of the gem5-SALAM framework, the Top accelerator's role is particularly pivotal in managing hardware components designed for specific tasks. It's tasked with initializing and controlling these hardware accelerators, as well as managing the Direct Memory Access (DMA) operations that are crucial for the efficient transfer of data between the system's main memory and the accelerators' scratch-pad memory. This capability is critical for operations that require rapid and frequent data exchanges, such as complex computational tasks or data-intensive processes.

The operational mechanism of the Top accelerator involves receiving and interpreting commands from the system's CPU, initiating the appropriate hardware accelerators, and overseeing the DMA processes. The control mechanism is implemented through a series of Memory Mapped Registers (MMRs), which the CPU utilizes to communicate with the Top accelerator. These MMRs serve as a bridge, allowing the CPU to pass control signals and data addresses to the Top accelerator, which then translates these into actions for the hardware accelerators and DMAs.

The Top accelerator's code, typically organized in a file like top.c, begins with the declaration of these MMR addresses. These addresses correspond to locations in the accelerator's memory space, which the CPU later fills with relevant data. Additionally, the Top accelerator sets up static addresses linked to the MMRs of the connected hardware accelerators, enabling direct control over these components.

A significant feature of the Top accelerator is its ability to manage data transfers through DMAs. This process involves setting up the MMRs of the DMA to execute memory transfers efficiently between the main memory and the accelerator's scratch-pad memory. The Top accelerator initiates these transfers and continuously polls the DMA for completion status, ensuring a seamless data flow crucial for the optimal functioning of the hardware accelerators.

The Top accelerator's capabilities are not just limited to managing data flow but also extend to optimizing system performance. By efficiently controlling the hardware accelerators and DMAs, the Top accelerator plays a critical role in reducing the computational load on the main CPU, allowing for more efficient overall system performance. This is particularly important in scenarios where the system is running complex, data-intensive tasks that would otherwise significantly burden the main processor.

The gem5-X framework is an advanced full-system simulator based on the gem5 simulator, with a focus on architectural extensions and the optimization of heterogeneous systems. Key aspects of the gem5-X framework include:

Architectural Exploration and Optimization: gem5-X facilitates architectural exploration and optimization, particularly for heterogeneous systems. It integrates advanced features like in-cache computing and 3D stacked High Bandwidth Memory, allowing for a detailed analysis of system performance and potential bottlenecks.

- Performance Validation: The framework's performance results have been validated against real-world hardware, such as the ARMv8 JUNO board, demonstrating a high accuracy rate (below 4% error) in execution time comparisons.

- Support for State-of-the-Art Processors: gem5-X is designed to support current leadingedge processors, including ARMv8 in-order and out-of-order architectures. This makes it a valuable tool for exploring and optimizing modern processing architectures.

- User-Friendly Environment: Aimed at computer architects from both academia and industry, gem5-X offers a user-friendly environment that simplifies the learning curve associated with gem5. It provides a fully operational environment and setup right out of the box, fostering easier and faster development.

- Open-Source and Community Engagement: As an open-source project, gem5-X encourages engagement and contribution from the wider computer architecture community. This collaborative approach enhances the framework's capabilities and aligns it closely with real-world application requirements and architectural constraints.

- Specialized Architectural Extensions: The framework includes specialized environments

for various architectural extensions, such as Analog In-Memory Cores (AIMCs), wireless

in-package links, and tightly-coupled systolic arrays. These extensions are available in

separate repositories within the gem5-X GitHub organization, underscoring the

framework's versatility and adaptability to diverse architectural needs.

Overall, gem5-X represents a significant development in full-system simulation, offering comprehensive tools for analyzing and optimizing complex and heterogeneous system architectures.

# 2.7.2 Design Philosophies

In the intricate field of computer architecture and hardware acceleration, the design of frameworks like gem5-Aladdin, SMAUG, gem5-SALAM, MAESTRO, and gem5-X is not just a matter of technical necessity but also a reflection of visionary foresight. These frameworks are conceived to address the multifaceted challenges and leverage the opportunities presented by the dynamic landscape of modern computing.

gem5-Aladdin stands as a prime example of innovative design in the realm of hardware-software co-simulation. Its philosophy is anchored in the integration of system-level and accelerator-level simulations, providing a dual lens through which the interplay of hardware accelerators with traditional CPU and memory systems can be studied. The rationale behind this is rooted in the recognition that the future of computing lies in the synergy between heterogeneous computing elements. The ability of gem5-Aladdin to simulate diverse accelerator configurations alongside CPUs offers invaluable insights into performance bottlenecks and energy efficiency, making it an indispensable tool in the era of specialized computing.

SMAUG takes a slightly different approach, focusing on the burgeoning field of neural network accelerators. Its design philosophy emphasizes adaptability and user-friendliness, recognizing the rapid pace at which this field is evolving. By providing a flexible platform that